Изобретение относится к вычислительной технике и может быть использовано в процессоре реляционной алгебры систему управления реляционными базами данных и знаний интеллектуальной системы автоматизированного проектирования РЭА и ЭВА.

Известно устройство для преобразования кодов с одного языка на другой, содержащее регистр приема, Два дешифратора, блок памяти, регистр выдачи, регистр управления, две группы элементов И, группу элементов ИЛИ, элемент НЕ.

Недостаток - структурная сложность и низкое быстродействие.

Известно устройство для преобразования кодов с одного .языка на другой, содержащее регистр приема, группу элементов ИЛИ, две группы элементов И, дешифратор,

.©

блок памяти, регистр выдачи, два элемента И.

Недостаток - структурная сложность и низкое быстродействие.

Наиболее близкое по технической сущности устройство для редактирования элементов таблиц, содержит счетчик, Две группы элементов И, группу элементов ИЛИ, дешифратор, блок памяти, регистр ин- формации, блок микропрограммного управления, регистр строки и узелсравнения, причем вход регистра информации соединен с выходом блока памяти, а выходы разрядов регистра информации подключены к первым входам элементов И первой и второй групп, выходы элементов И первой группы являются выходом устройства, выходы элементов И второй группы соединены с первыми входами элементов ИЛИ группы, первый вход узла сравнения и вход дешифч|00 Ю Ю О

СА

ратора соединены с выходом регистра информации, §ы х ойГрегйстра строки соединен с вторым входом узла сравнения и информационным входом блока памяти, адресный вход которого соединен с выходом счетчика, информационный и установочный входы кб- торогр являются соответственно адресным и установочным входами устройтсва,инфор- мафонны Й вход которого соединен с вто- вхёйамй элементов ИЛИ группы, выходы KOfo pVx соединены с входом реги- стр$гстроки, шход узла сравнения соединен с разрешающим входом блока микропрограммного управления, вход запуска и вход сигнала конца таблицы которого соединены соответственно с входом запуска устройства и с выходом дешифратора, выходы блока микропрограммного управления соединены соответственно с входом считывания, с входом записи блока памяти, с вторыми входами первой и второй групп элементов И и со счетным входом счетчика.

Недостаток - низкое быстродействие, обуслбвлённде микропрограммным принципом управления устройством.

Цель изобретения - повышение быстродействия устройства.

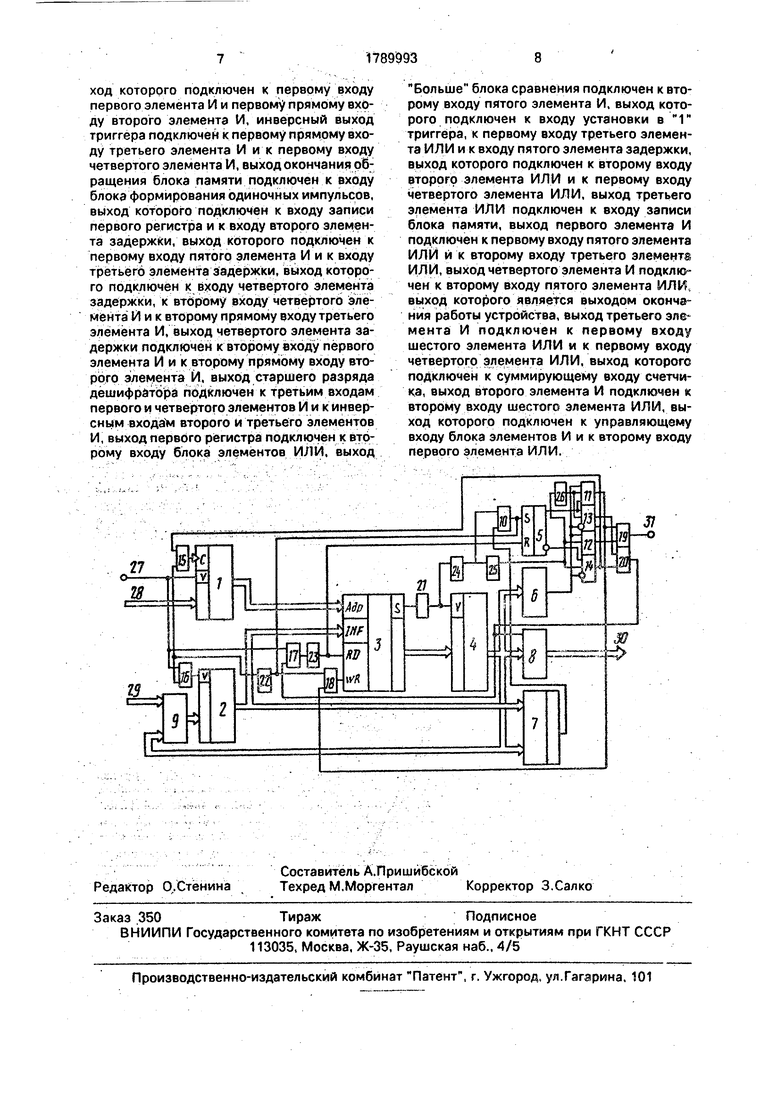

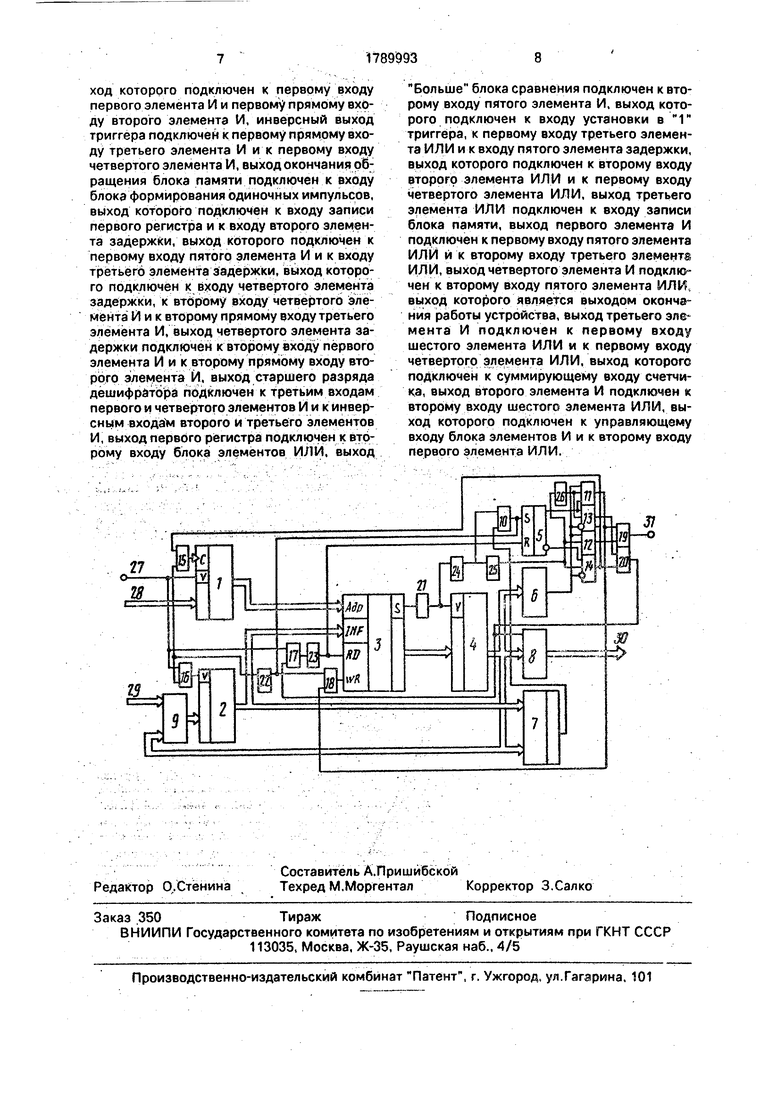

На чертеже представлена структурная схема устройства.

Устройство содержит счетчик 1, дешифратор 2, блок3 сравнения, блок4 элементов И. блок 5 элементов ИЛИ, регистры 6 и 7, блок 8 памяти, элементы И 9-13, элементы ИЛИ 14-19, блок 20 формирования одиночных импульсов, элементы 21-25 задержки, информационный выход 26 устройства, вход 27 задания адреса таблицы устройства, информационный вход 28 устройства, вход 29 запуска устройства, триггер 30, выход 31 окончания работы устройства. Причем вход регистра 7 соединен с выходом блока 8, а выходы его разрядов подключены к входам элементов И 4, выходы которых являются выходом 26, первый вход блока 3 и вход дешифратора 2 соединены с выходом регистра 7, выход регистра 8 соединен с вторым входом блока 3 и информационным входом {блока 8, адресный вход которого соединен с выходом счетчика 1, информационный вход которого является входом 27, информационный вход 28 соединен со вторыми входами элементов ИЛИ 5, выходы которых соединены с входом регистра 6, вход &9 соединен с входом записи счетчика 1, а через элемент ИЛИ 15 с входом записи регистра 6, с первым входом элемента ИЛИ 16, выход которого подключен через элемент 21 к входу считывания блока 8 и нулевому входу триггера 30, прямой и инверсный выходы которого подключены к первым входам элемента И 9,элемента И 10 и элементов И 11, И 12 соответственно, выход 5 блока 8 подключен через блок 20 к входу записи регистра 7, а через элемент 22 к первому входу

элемента И 13 и входу элемента 23. выход которого подключен к вторым входам элементов И 11 и И 12, а через элемент 24 к вторым входам элементом И 9 и И 10, третьи входы элементов И 9 и 11 и инверсные вхо0 ды элементов И 10 и 12 подключены к выходу дешифратора 2, выходы разрядов регистра 7 подключены к первым входам элементов ИЛИ 5, выход Больше блока 3 подключен через элемент И 13 к единично5 му входу триггера 30, через элемент ИЛИ 17 к входу записи блока 8, а через элемент 25 к вторым входам элементов ИЛИ 14 и 15, выход элемента И 9 подключен к первому входу элемента ИЛИ 18 и второму входу

0 элемента ИЛИ 17, выход элемента И 11 подключен через элемент ИЛИ 18 и второму входу элемента ИЛИ 17, выход элемента И 11 подключен через элемент ИЛИ 18 к сигнальному входу 31, выход элемента И 12

5 подключен к второму входу элемента ИЛИ 19, а через элемент ИЛИ 14 к счетному входу счетчика 1, выход элемента И 10 подключен через элемент ИЛИ 19 к входам опроса элементов И 4 и второму входу элемента ИЛИ

0 16.

Принцип работы устройства состоит в следующем.

Устройство запускается импульсом, подаваемым на вход 29. При этом в счетчик 1

5 с входа 27 записывается адрес первого реляционного отношения в базе, куда необходимо включить новое реляционное отношение. Включаемое реляционное отношение заносится в регистр б со входа 28

0 через элемент ИЛИ 5, Это реляционное отношение будет вставлено в базу таким образом, что реляционные отношения останутся отсортированными. Задержанный на элементе 21 на время записи исходной инфор5 мации в счетчик 1 и регистр 6, импульс обнуляет триггер 30 и разрешает считывание из блока 8 первого отношения. После окончания переходных процессов при выборке кода первого отношения на асинхрон0 ном выходе 5 окончания переходных процессов блока 8 появляется положительный порог (перепад у ровней 0-1) преобразуемый блоком 20 импульс стандартной длительности, который разрешает считыва5 ние первого (в дальнейшем очередного) отношения в регистр 7. Блок 8 содержит базу данных, состоящую из некоторого количества реляционных отношений, каждое из которых занимает одну ячейку памяти. В базе отношения отсорбированы по возрастанию

ключей для ускорения поиска требуемого отношения. В ячейке блока 8, непосредственно следующей за последним отношением базы, записывается код конца базы (уникальный код, расшифровываемый де- шифратором 2), содержащий в качестве ключа максимально возможный код, который запрещается использовать в качестве ключа какого-либо отношения. В блоке 3 сравниваются ключи очередного считанно- го отношения (регистр 7) и заключаемого отношения (регистр 6). Если ключ отношения, находящегося в регистре 7, больше ключа отношения из регистра б, то появляется сигнал ха выходе Больше блока 3, который открывает элемент И 13, и импульс с выхода блока 20, задержанный на элементе 22 на время записи в регистр 7 и время срабатывания схемы 3, переводят триггер 30 в единичное состояние, инициализируя тем самым режим записи отношения. Импульс с выхода элемента И 13 поступает через элемент ИЛ И 17 на вход записи блока 8, разрешая запись в него включаемого отношения с выхода регистра 6 по адресу, поступающему с выхода счетчика 1. Задержанный на элементе 25 на время записи информации в блок 8, импульс поступает через элемент ИЛИ 15 на вход записи регистра б, разрешая перезапись информации из регистра 7 через элемент ИЛИ 5 в регистр 6. Одновременно с этим импульс поступает через элемент ИЛИ 14 на вход счёта счетчика 1, увеличивая его содержимое на единицу. Если на выходах регистра 7 не присутствует код конца базы, то на выходе

дешифратора 2 присутствует О потенциал, поэтому импульс с выхода элемента 23, задержка которого ра вна времени срабатывания триггера 30, проходит через элементы 24 и И 10, открытый 1 потенциалом с прямого выхода триггера 30 и О потенциалом с выхода дешифратора 2, элемент ИЛИ 19 и открывает 5/1ём ё нты И 4, разрешая поступление информации с выхода регистра 7 на выход 26. Также импульс поступает через элемент ИЛИ 16 на вход элемента 21. Если на выходах регистра 7 присутствует код конца базы, то на выходе дешифратора 2 проходят через элемент 24, где задерживается на время, достаточное для разделения двух процессов записи в блок 8, и элемент И 9, открытый 1 потенциалами с прямого выхода триггера 30 и выхода дешифратора 2, и поступает через элемент ИЛИ 17 на вход записи блока 8. Такие импульсы с выхода элемента И 9 проходят через элемент И 18 на выход 31. Если ключ отношения из регистра 7 меньше или равен ключу отношения из регистра 8, то триггер 30 остается в нулевом состоянии, а импульсе выхода элемента 23 в зависимости от состояния выхода дешифратора 2 проходит через элемент И 11 и поступает через элемент ИЛ И 18 на выход 31 (при 1 потенциале на выходе дешифратора 2) или проходит через элемент 12 и поступает через элемент ИЛИ 14 на вход счета счетчика 1, а также поступает через элемент ИЛИ 19 на входы опроса элементов И 4 и проходит через элемент ИЛИ 16 на вход элемента 21.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения пересечения множеств | 1990 |

|

SU1756903A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для выполнения операций редактирования записей таблиц | 1984 |

|

SU1543419A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Устройство для редактирования записей в таблицах | 1987 |

|

SU1479941A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Устройство адресации памяти | 1988 |

|

SU1575188A1 |

| Устройство для редактирования элементов таблиц | 1984 |

|

SU1208563A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1140120A1 |

Изобретение относится к вычислительной технике и может быть использовано в процессоре реляционной алгебры систем управления реляцибннйми базами данных и знаний интеллектуальной системы автоматизированного npoeKfHpTSWaHW РЭА и ЭВА. Цель изобретения - повышение быстродействия. Устройство содержит счетчик, два регистра, блок памяти, дешифратор, схему сравнения, группы элементов И и ИЛИ, триггер, три элемента И, два элемента ЗАПРЕТ, шесть элементов ИЛИ, формирователь импульса и пять элементов задержки с соответствующими связями. Изобретение позволяет повысить быстродействие устройства за счет перехода от микропрограммной синхронной архитектуры к аппаратной с местным асинхронным управлением. 1 ил.

Формула изобретения

Устройство для редактирования элементов таблиц, содержащее счетчик, дешифратор, блок сравнения, блок элементов И, блок элементов ИЛИ. два регистра и блок памяти, причем информационный выход блока памяти подключен к входу дешифратора, к первому информационному входу блока еравнения и к информационному входу первого регистра, выход которого подключен к информационному входу блока элементов И, выход которого является информационным выходом устройства, вход задания адреса таблицы устройства подключен к информационному входу счетчика, выход которого подключен к адресному входу блока памяти, информационный вход устройства подключен к первому входу блока

элементов ИЛИ, выход которого подключен к информационному входу второго регистра, выход которого подключен к второму информационному входу блока сравнения и к информационному входу блока памяти, отличающееся тем, что, с целью повышения быстродействия, в него введены пять элементов И, шесть элементов ИЛИ, блок формирования одиночных импульсов и пять элементов задержки, причем вход пуска устройства подключен к входу записи счетчика, к первому входу первого элемента ИЛИ и к первому входу второго элемента ИЛИ, выход которого подключен к входу записи второго регистра, выход первого элемента ИЛИ подключен к входу первого элемента задё ржки, выход которого подключен к входу чтения блока памяти и к входу установки в О триггера, прямой выход которого подключен к первому входу первого элемента И и первому прямому входу второго элемента И, инверсный выход триггера подключен к первому прямому входу третьего элемента И и к первому входу четвертого элемента И, выход окончания обращения блока памяти подключен к входу блока формирования одиночных импульсов, выход которого подключен к входу записи первого регистра и к входу второго элемента задержки, выход которого подключен к первому входу пятого элемента И и к входу третьего элемента задержки, выход которого подключён к входу четвертого элемента задержки, к второму входу четвертого элемента Пик второму прямому входу третьего элемента И, выход четвертого элемента задержки подключен к второму входу первого элемента И и к второму прямому входу второго элемента И, выход старшего разряда дешифратора подключен к третьим входам первого и четвертого элементов И и к инверсным входам второго и третьего элементов И, выход первого регистра подключен к второму входу блока элементов ИЛИ, выход

Больше блока сравнения подключен к второму входу пятого элемента И. выход которого подключен к входу установки в Т триггера, к первому входу третьего элемента ИЛИ и к входу пятого элемента задержки, выход которого подключен к второму входу второго элемента ИЛИ и к первому входу четвертого элемента ИЛИ, выход третьего элемента ИЛИ подключен к входу записи блока памяти, выход первого элемента И подключен к первому входу пятого элемента ИЛИ и к второму входу третьего элемента ИЛИ, выход четвертого элемента И подключен к второму входу пятого элемента ИЛЦ выход которого является выходом окончания работы устройства, выход третьего эле- мента И подключен к первому входу шестого элемента ИЛИ и к первому входу четвертого элемента ИЛИ, выход которого подключен к суммирующему входу счетчика, выход второго элемента И подключен к второму входу шестого элемента ИЛИ, выход которого подключен к управляющему входу блока элементов И и к второму входу первого элемента ИЛИ.

| Устройство для преобразования кодов с одного языка на другой | 1978 |

|

SU780011A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Запоминающее устройство | 1984 |

|

SU1208583A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-23—Публикация

1990-10-16—Подача