Изобретение относится к вычисли- тельной технике и может быть использовано в информационных системах дпя приема и передачи информации в последовательных кодахо

Цель изобретения - повышение достоверности приема информации с

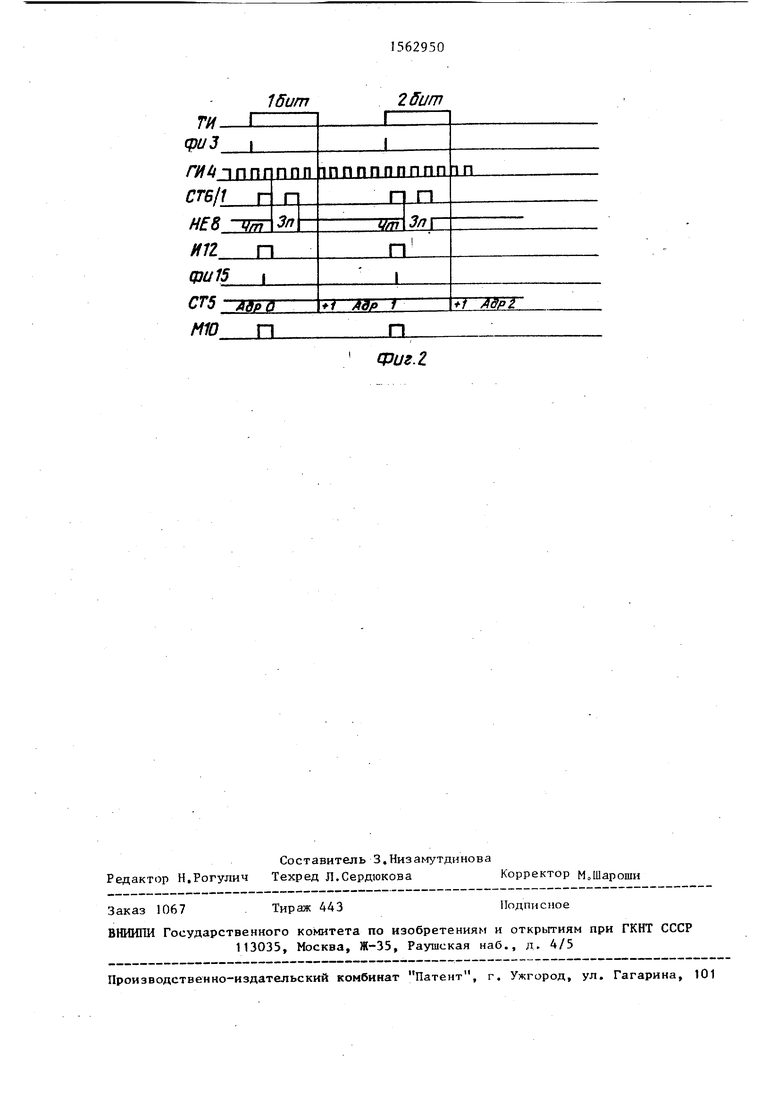

На фиг„1 приведена блок-схема устройства; на фиг02 - временная диаграмма его работы,

Устройство содержит регистр 1, дешифратор 2, формирователь 3 импульсов, генератор 4 импульсов, счетчики 5-7, элементы НЕ 8, И-НЕ 9, блоки 10 и 11 памяти, элемент И 12, блок 13 сравнения, элемент И 14, формирователь 15 импульсов, элемент И 16 и триггеры 17 и 18,

Вход приема кодограмм соединен с блоками 10 и 11 памяти, блоком 13

сравнения и входом регистра 1, второй вход которого соединен с тактовым входом устройства,, Выходы регистра 1 подключены к дешифратору 2, выход которого соединен со счетчиками 5 и 7 и триггером 170 Тактовый вход устройства соединен с входом счетчика 5, через формирователь 3-е генератором 4 и входом счетчика 6, Выход генератора 4 соединен со счетчиком 6, Вы- ходы счетчика 5 соединены с адресными входами блоков 10 и 11 памяти. Первый выход счетчика 6 соединен с CS-входами блоков 10 и 11 памяти, и входами элемента И 12, Второй выход счетчика 6 соединен с входом элемента И 12. Второй выход счетчика 6 соединен с входом элемента И-НЕ 9 и J через элемент НЕ 8 с W/R входом блока 10 памяти и входом элемента И 12, выход которого через формирователь 15 импульсов подключен к входу элемента И 14„ Выход блока 13 сравнения соединен с элементом И 14, выход которо

,

$

0

5

го соединен с нулевыми входами счетчика 7 и триггера 180 Выход последнего соединен с входом элемента И-НЕ 9, подключенного выходом к входу W/F блока 11 памятио Первый выход счетчика 7 соединен с триггером 18, второй выход - с триггером 17, выход которого соединен с входом элемента И 16, подключенного к выходу блока 11 памяти, а выход элемента И 16 соединен с выходом устройства0

Устройство работает следующим об- разоМо

В исходном состоянии регистр 1, блоки 10 и 11 памяти, счетчики 5-7, триггеры 17 и 18 установлены в нулевое положение (цепи начальной уста- новки не показаны)о Нулевой сигнал с выхода триггера 18 закрывает элемент И-НЕ 9, на выходе которого формируется сигнал высокого уровня, обеспечивающий режим чтения информа- ции из блока 11 памяти. Нулевой сигнал с выхода триггера 17 закрывает элемент И 16 и отключает выход устройства,,

Информация в последовательном коде поступает на информационный вход устройства в виде серий из идентичных кодограмм, причем кратность повторения одной и той же кодограммы определяется требованиями достоверности доведения ее до пользователя. Каждая кодограмма содержит байт маркера, соответствующий началу кодограммы и предшествующий информационным байтамс Длина кодограммы задана определенным числом бит. Каждый бит кодограммы сопровождается импульсом , который подается на вход ТИ устройства,, Биты кодограммы последовательно подаются на D-входы блоков 10 и 11 памяти, на вход блока 13 сравнения и записываются в сдвигающий регистр 1 о Дешифратор 2 декодирует код маркера после того, как он заполнит регистр 1. Сигнал маркера, Т0е0 сигнал начала кодограммы, с выхода дешифратора 2 подается на счетный вход счетчика 7, который считает число поступающих кодограмм, обнуляет адресный счетчик 5 и триггер 17. По каждому тактовому импульсу от начала кодограммы адресный счетчик 5 увеличивает свое содержимое на единицу, т.е обеспечивает формирование адреса для каждого бита информации. После подсчета всего заданного числа бит в кодограмме счетчик 5 прекращает счет тактовых импульсов сигналом с выхода своего старшего разряда. Если число бит в кодограмме не кратно двум, счетчик 5 должен останавливаться специальным дешифратором, подключенным входами к выходам счетчика 5 и дешифрирующим число бит в кодограмме. Кроме того, по переднему фронту тактового импульса формирователь 3 импульсов формирует узкий импульс, который синхронизирует работу генератора 4 и обнуляет счетчик 6, Импульсы генератора 4 подаются на счетный вход счетчика 6, который считает по заданному фронту импульсов генератора 4 и после счета четырех импульсов прекращает счет подачей запрещающего сигнала со своего третьего выхода на управляющий С-вход„ Сигнал с первого выхода счетчика 6 подается на С-входы блоков 10 и 11 памяти и на первый вход элемента И 12. Сигнал с второго выхода счетчика 6 подается на вход элемента И-НЕ 9 и через элемент НЕ 8 на вход W/В блока 11 памяти и на вход элемента И 12. Счетчик 6 обеспечивает за один период тактовых импульсов (период между би тами информации) организацию одного цикла чтения и записи в блоки 10 и 11 памяти, в зависимости от управляю-, щих сигналов на их W/R входах (фиг02)0 Так как в исходном состоя нии блок 11 памяти находится постоянно в режиме чтения, то с его выхода при прохождении всех бит первой кодограммы считываются только нулевые сигналы, но на вход устройства че- рез элемент И 16 не выдаются. Параллельно для каждого бита этой кодо- i граммы в блоке 10 памяти организуется цикл чтения и записи,, При этом в цикле чтения поступающий бит и счи0

5

0

тайный бит (в исходном положении - нулевой) сравниваются блоком 13 сравнения, который при несовпадетш этих бит выдает сигнал, стробируемый через элемент И 14 импульсом, сформированным элементом И 12 и формирователем 15 (фиг.2)о Импульс с выхода элемента И 14 обнуляет счетчик 7 и триггер 18. Таким образом, после приема первой кодограммы она записывается в блок 10 памяти, а из блока 11 памяти считаны нулевые сигналы .

При поступлении второй и т.д. идентичной кодограммы, сигнал маркера вновь обнуляет счетчик 5 и прибавляет единицу к текущему числу в счет - чике 7. Дальнейшая работа устройства при приеме бит кодограммы аналогична описанной. Однако теперь при чтении из блока 10 памяти биты поступающей кодограммы сравниваются с битами идентичной предыдущей кодограммы. При совпадении этих бит сигнал 5 на выходе элемента И 14 отсутствует и счетчик 7 сохраняет свое значение до прихода следующей кодограммы,. при этом каждый раз вновь поступающая кодограмма переписывается в блок 10 памяти.После поступления некоторого порогового числа совпадающих побит- но кодограмм, которое является критерием достоверности сообщения, счетчик

7при поступлении пороговой идентичной кодограммы, формирует выходной сигнал, от которого срабатывает триггер 18. Сигнал с его выхода снимает через элемент И-НЕ 9 постоянно действующий режим чтения с блока 11 памяти. При зтом на входах CS и W/F блока 11 памяти для текущей пороговой кодограммы действуют те же сигналы, что и для блока 10 памяти, т.е. для каждого бита обеспечивается цикл чтения и записи в блок 11 памяти.

Таким образом, пороговая кодограмма записывается в блок 11 памяти, но пользователю не выдается. Биты пороговой кодограммы при поступлении непрерывно сравниваются с битами предыдущей кодограмьы соответственно, записанной в блоке 10 памяти,

8случае несовпадения этих бит счетчик 7 и триггер 18 обнуляются и запись кодограммы в блок 11 памяти прекращается до прихода группы следующих идентичных кодограмма

Если сбоев при приеме кодограммы нет, то после поступления пороговой

0

5

0

5

0

5

10

15

кодограмм, триггер 18 сработал, счетчик 7 сохраняет свое состояние и, после поступления еще некоторого заданного числа кодограмм формирует сигнал на своем втором выходе и прекращает счет о Сигнал с второго выхода счетчика 7 включает триггер 17, который открывает элемент И 16 и считываемая во время циклов чтения из блока 11 предыдущая кодограмма поступает на выход устройства. После считывания каждого бита данной кодо граммы в блоке 11 памяти происходит запись бита текущей кодограммы и, если произойдет сбой (несравнение бит текущей и предыдущей кодограмм) то запись в блок 11 памяти прекращается, но считывание записанной ранее достоверной кодограммы и выдача ее через элемент И 16 продолжается до конца, т.е„ до прихода следующей кодограммы. Маркер следующей кодограммы сбрасывает в нулевое положение триггер 17 и выдача кодограммы данной серии во внешнее устройство прек-i раЩается, В случае изменения самой кодограммы, т,е0 с приходом накапливания их числа в счетчике 7, запись в блоках 10 и 11 памяти и, при отсут- 30 ствии ошибок, выдача с помощью триггеров 17 и 18 во внешнее устройство,

В устройстве за счет введения второго блока памяти и двух триггеров

15629508

нератор импульсов, формирователи импульсов, блок сравнения, элементы И, элемент И-НЕ, второй и третий счетчики, элемент НЕ, о тли чающееся тем, что, с целью повышения достоверности приема информации, в него введены триггеры и второй блок памяти, вход первого формирователя импульсов и запускающий вход первого счетчика объединены и являются тактовым входом устройства, выход первого формирователя импульсов подключен через генератор импульсов и непосредственно к запускающему установочному входу второго счетчика соответственно, первый выход второго счетчика соединен с первыми управляющими входами первого и второго блоков памяти и первым входом первого элемента И, второй выход второго счетчика подключен к первому входу элемента И-НЕ и через элемент НЕ к второму входу первого элемента И и второму управляющему входу первого блока памяти, выходы группы первого счетчика подключены к адресным входам первого и второго блоков памяти, выходы которых подключены к первым входам соответственно блока сравнения и второго элемента И, выход дешифратора соединен с запускающим входом третьего счетчика и установочным входом первого триггера, выход кото20

25

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации | 1986 |

|

SU1336074A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Устройство для фиксации сбоев | 1987 |

|

SU1462320A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

| Устройство передачи и приема информации | 1991 |

|

SU1793454A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1594554A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

Изобретение относится к вычислительной технике и может быть использовано в информационных системах для приема и передачи информации в последовательных кодах. Цель изобретения - повышение достоверности приема информации. Кодограммы в виде серий из N идентичных сообщений в последовательных кодах поступают в блоки 10 и 11 памяти. Сдвигающий регистр 1 с дешифратором 2 фиксируют маркер - начало кодограммы, счетчик 5 формирует адреса для каждого бита кодограммы, счетчик 6 формирует циклы записи/чтения блоков 10 и 11 памяти, счетчик 7 считает число поступающих кодограмм. Вначале кодограммы записываются в блок 10 памяти и с помощью блока 13 сравнения сравниваются предыдущая и последующая кодограммы. После поступления порогового числа совпадающих кодограмм текущая кодограмма записывается в блок 11 памяти, счетчик 7 устанавливает в единичное состояние триггер 17, который подключает через элемент И 16 выход блока 11 памяти к выходу устройства. 2 ил.

обеспечивается многократный прием се- ,5 рого подключен к второму входу вторории идентичных кодограмм, их побитное сравнение между собой и после заданного числа совпадений, формирование разрешения записи и выдачи кодограммы пользователю. Это повышает достоверность приема информации в последовательных кодах, снижает вероятность ошибки при приеме и исполнении команд, исключает аварийные ситуации в управляющих комплексах,,

Формула изобретения Устройство для приема информации, содержащее регистр, первый и второй входы которого являются соответственно тактовым и информационным входами устройства, выходы регистра соединены с соответствующими входами дешифратора, выход которого подключен к установочному входу первого счетчика, первый блок памяти, информационный вход которого является информационным входом устройства, ге40

45

50

55

го элемента И, выход которого является выходом устройства, второй вход блока сравнения и информационный вход второго блока памяти объединены и являются информационным входом устройства, выход первого элемента И через второй формирователь импуль- , сов соединен с первым входом третье- го элемента И, второй вход которого подключен к выходу блока сравнения, выход третьего элемента И подключен к установочным входам второго триг- ,гера и третьего счетчика, первый и Iвторой выходы которого соединены со счетными входами первого и второго триггеров соответственно, выход которого подключен к второму входу элемента И-НЕ, выход которого соединен с вторым управляющим входом второго блока памяти, выходы последнего разряда первого, второго и третьего счетчиков подключены к своим синхронизирующим входам0

рого подключен к второму входу второго элемента И, выход которого является выходом устройства, второй вход блока сравнения и информационный вход второго блока памяти объединены и являются информационным входом устройства, выход первого элемента И через второй формирователь импуль- , сов соединен с первым входом третье- го элемента И, второй вход которого подключен к выходу блока сравнения, выход третьего элемента И подключен к установочным входам второго триг- ,гера и третьего счетчика, первый и Iвторой выходы которого соединены со счетными входами первого и второго триггеров соответственно, выход которого подключен к второму входу элемента И-НЕ, выход которого соединен с вторым управляющим входом второго блока памяти, выходы последнего разряда первого, второго и третьего счетчиков подключены к своим синхронизирующим входам0

1бит

МЮ

П

Составитель З.Низамутдинова Редактор Н.Рогулич Техред Л.СердюковаКорректор м.Шарошн

Заказ 1067

Тираж 443

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

2 бит

П

Фиг. 2

Подписное

| Устройство для приема информации | 1986 |

|

SU1336074A1 |

Авторы

Даты

1990-05-07—Публикация

1988-08-15—Подача