Фиг. 1

формирователь 6 импульсов, счетчик 7 дешифратор 8, формирователь 9 импульсов, элемент ИЛИ Ю, элементы И 11,12, элемент НЕ 13, формирователи 14,15 импульсов, элемент ИЛИ 16, счетчики 17,18, элемент НЕ 19, дешифратор 20, счетчик 21, регистр 22, дешифратор 23, коммутатор 24, блок 25 памяти, блок 26 сравнения, счетчик 27, элемент И 28. В устройстве за счет введения коммутатора, двух регистров, трех дешифраторов, двух счетчиков, блока сравнения, четырех формирователей импульсов, генератора

146

феа

1462320

импульсов, блока синхронизации, элементов НЕ, ИЛИ обеспечивается вьщеле- ние из поступшощих кодограмм бит, запоминание логических значений этих бит и периодическое чтение и стимулирование этих значений для многократно повторяемых кодограмм, сравнение полученньт: сумм с заданным пороговым значением. Положительный эффект достигается введением новых элементов и взаимосвязей и определяется в возможно-сти исключения влияния случайных сбоев на результат контроля. 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема информации | 1986 |

|

SU1336074A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для управления вводом информации | 1988 |

|

SU1566337A1 |

| Многоканальное устройство для сравнения кодов | 1990 |

|

SU1795446A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

Изобретение относится к вычислительной технике и может быть использовано для контроля передачи данных. Цель изобрете1шя - повышение достоверности работы устройства. Устройство содержит генератор I импульсов, блок 2 синхронизации, формирователь 3 импульсов, регистр 4, дешифратор 5, 29 30 « (Л 4 а 1чЭ 00 ьо

10

.1

- Изобретение относится к вычислительной технике и может быть использовано для контроля передачи данньк.

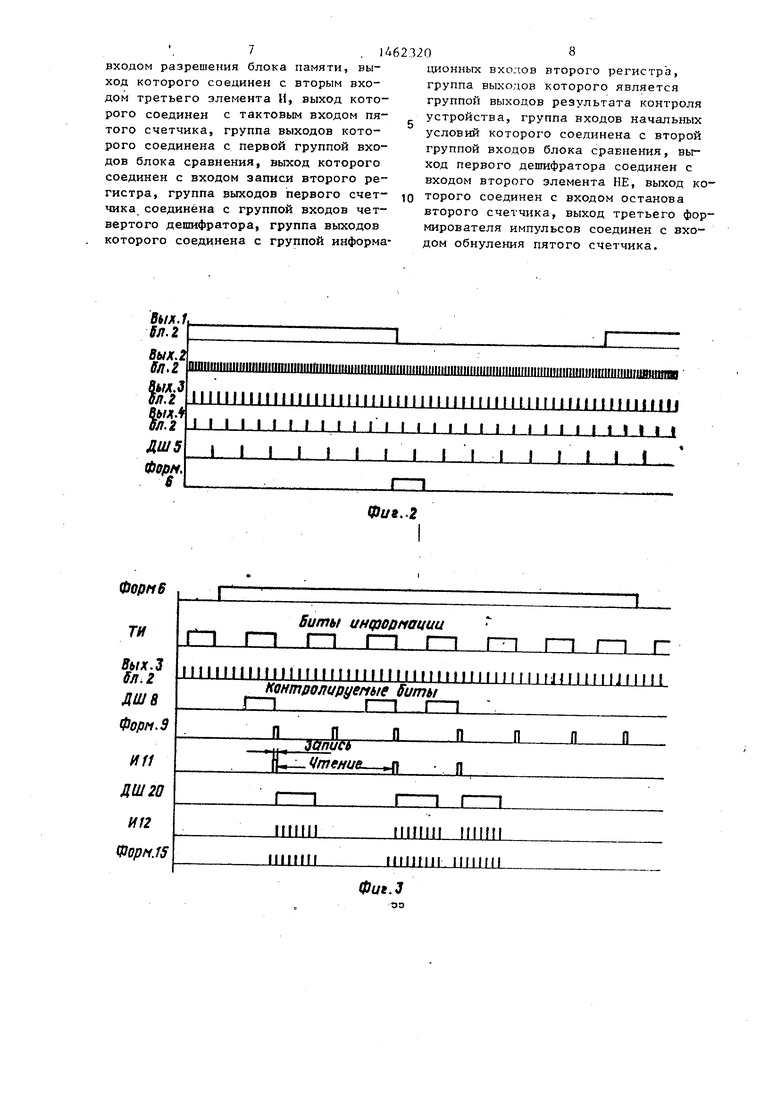

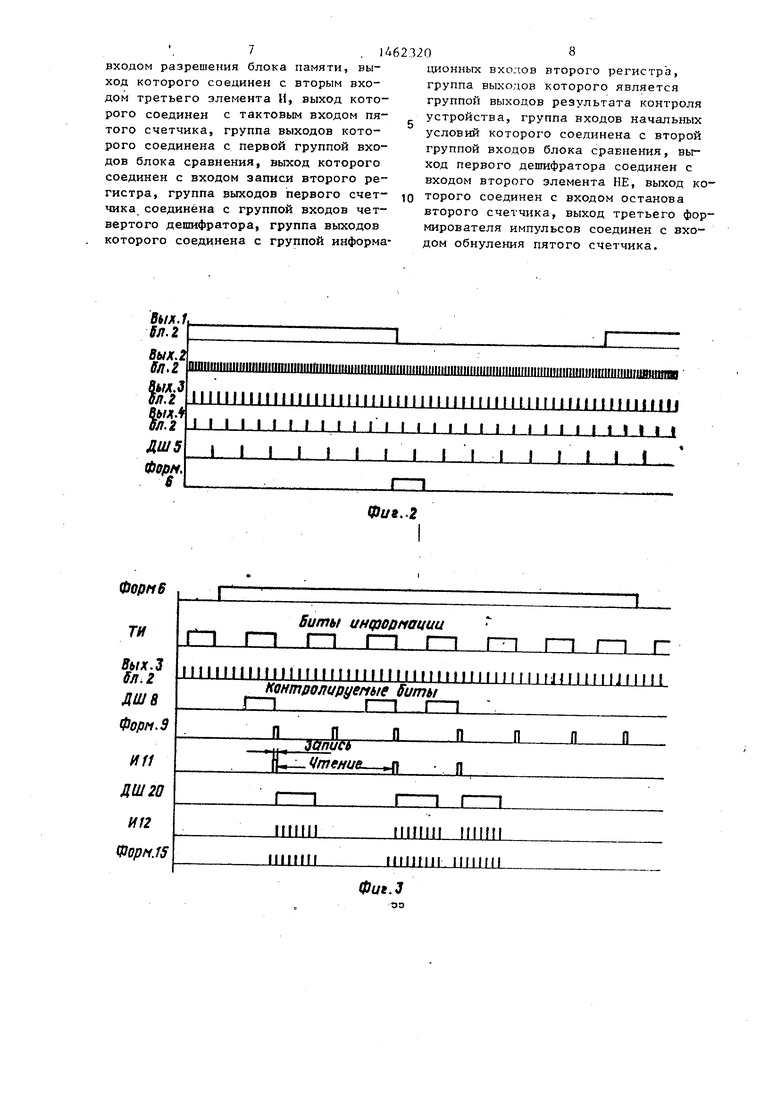

Целью изобретения является повьше- ние достоверности работы устройства. На фиг.1 изображена функциональная схема предлагаемого устройства; на фиш.2 и 3 - временные диаграммы работы устройства.

Устройство (фиг.1) содержит генератор 1 импульсов, блок 2 синхронизации., формирователь 3 импульсов, регистр 4, дешифратор 5, формирователь. 6 импульсов, счетчик 7, дешифратор 8,55 Формирователь 9 импульсов, элемент ИЛИ 10, элементы И И и 12, элемент НЕ 13, формирователи 14 и 15 импульсов, элемент ИЛИ 16, счетчики 17 и 18, элемент НЕ 19, дешифратор 20, счетчик 21, регистр 22, дешифратор 23, коммутатор 24, блок 25 памяти, блок 26 сравнения, счетчик 27, элемент И 28, вход 29 синхронизации, информационный вход 30, группу 3i входов начальных условий, выход 32 сигнала отсутствия контролируемой информации, группу 33 выходов результата контроля.

Устройство работает следующим об- ЗО разом.

Контролируемая информация в после- овательном коде подается байтами на информационный вход устройства в вие идентичных кодограмм, следующих одна за другой, Первый байт в каждой кодограмме представляет собой код

20

25

35

10

55

О

20

25

5

маркера, которьй в других информа- . ционных байтах не повторяется и свидетельствует о начале кодограммы. В каждом информационном байте из всех его бит заранее определяются биты, логические значения которых необходимо контролировать, чтобы отделить случайные сбои от систематических ошибок. Местоположение этих бит в информационных байтах задается заранее. Логические значения этих бит определяются источниками, которые эти биты формируют.

После запуска генератора I импульсов включается блок 2 синхронизации, на выходах 1-4 которого формируются управляющие импульсы, показанные на Фиг. 2. Импульсы на выходе 1 выбираются исходя из времени, в течение которого вероятно изменение значений исполнительных бит кодограмм, и подаются на вход разрешения запуска формирователя 6. Биты кодограмм последовательно поступают на информационный вход сдвигающего регистра 4 и D-вход блока 25 памяти. На тактовьй вход сдвигающего регистра 4 подаются тактовые импульсы сопрововдения бит информации. Дешифратор 5 декодирует код маркера кодограммы после его накопления в регистра 4 и выдает сигнал маркера, которьй обнуляет счетчик 7 общего числа бит и счетчик 21 контролируемых бит, тем самым обеспечивается начало отсчета поступающих бит кодограммы. Кроме того, сигнш

10

№

20

маркера периодически устанавливает формирователь 3 и поступает на вход запуска формирователя 6. Формирователь 6 может быть выполнен на счетчике, который подсчитывает два импульса маркера с выхода дешифратора 5 во время отрицательного полупериода управляющего сигнала с выхода 1 блока 2 синхронизации и останавливается в этом состоянии (фиг.2). Таким образом, на выходе формирователя 6 формируется импульс, длительность которого равна длительности одной кодограммы (от одного маркера до следующего) и который подается на первый вход элемента И И. В процессе поступления бит кодограммы счетчик 7 подсчитывает их число и формирует на своих выходах коды номеров бит, которые декодируются депшфратором 8. Дешифра тор 8 выполнен так, что он декодирует только номера заданных бит кодограммы, достоверность приема которых должна быть высокой. Сигналы, соот- ветствукицие этим контролируемым битам, с выходов дешифратора 8 через элемент ИЛИ 10 подаются на второй вход элемента И 11, который открывается импульсами с выхода формирователя 9. Формирователь 9 формирует узкие импульсы по срезу тактовых импульсов, длительность одного импульса достаточна для записи одного бита информации в блок 25 памяти. Импульс с выхода элемента И 11 задает на входе режима работы блока 25 памятк режим записи информации (фиг.З) обнуляет счетчик 18 обзора кодограмм, выходы коммутатора 24 подключают к выходам счетчика 17 управляющими сигналами с выходов элементов И 1I и НЕ 19. Счетчик 2 работает от фронта выходного импульса элемента И 11 и фиксирует число контролируемых бит, 45 выделяемых дешифратором 8.. Одновременно импульс с элемента И 11 через элемент ИЛИ 16 подается на формирователь 15, импульс с выхода которого поступает на управляющий вход выбора блока 25 памяти и происходит запись данного бита в блок 25 памяти. Таким же образом происходит запись других контролируемых бит, выделяемых из кодограммы дешифратором 8./

Во время закрывания элемента И 1I на его выходе формируется низкий уровень напряжения. При этом счетчик 18 включа ется на счет импульсов, посту25

4Q

30

35

50

55

10

№

20

45 пающих с выхода 3 блока 2, входы коммутатора 2А переключаются с выходов счетчика 17 на выходы счетчика 18, на входе режима работы блока 25 памяти задан режим чтения информации. Счетчик 18 считает до числа, определяемого дешифратором 20, причем это число соответствует количеству кодограмм, подсчитываемых счетчиком 17, т.е. равно емкости счетчика 17. Счетчик 21 в это время установлен по адресу текущего исполнительного бита. Импульсы высокой частоты с выхода 3 блока 2 поступают через элемент И 2, открытый сигналами с выходов элемента НЕ 19 и дешифратора 20, и через элемент ИЛИ 16 поступают на вход формирователя 15, который формирует импульсы .обращения к блоку 25. Таким образом, по адресу данного бита просматриваются все значения этого бита во всех кодограммах, поступивбшх к данному моменту. Выход блока 25

25 памяти через элемент И 28 стробирует- ся импульсами с второго выхода блока 2. Количество считанных единиц на выходе блока 25 памяти подсчитывается счетчиком 27. Это число с выходов счетчика 27 сравнивается с заранее заданным пороговым числом (критерием определения ошибки) с помощью блока 26 сравнения. В случае превышения порогового числа сигнал с выхода блока 26 сравнения подается на вход записи регистра 22. На информационные входы регистра 22 подаются сигналы, соответствующие вьщеляемым исполнит тельным битам с выходов дешифратора

4Q 23, который декодирует состояние счетчика 21 иcпoJy итeльныx бит. С выходов регистра 22 соответствующие сигналы выдаются на выход 33 устройства.

Таким образом, в регистре 22 фиксируются биты, логические значения которых действительно ошибочны. Биты, логические значения которых изменились из-за случайных сбоев в регистр 22 не за писываются. .В случае, если в устройство после его включения вообще не поступает информация, формирователь 3 выдает сигнал отсутствия контролируемой информации на выход 32.

В предлагаемом устройстве за счет введения коммутатора, двух регистров, трех дешифраторов, двух счетчиков, блока сравнения, четырех формирователей импульсов, генератора, хронизато30

35

50

55

pa, элементов HE, ИЛИ обеспечивается выделение из поступаювдх кодограмм бит, предназначенных для дoвeдem я к исполнительным элементам запоминание логических значений этих бит и периодическое чтение и суммирование этих значений для многократно повторяемых кодограмм, сравнение полученных сумм с заданным пороговым значением и в зависимости от результата сравнения вьздача информации на исполнительные элементы. Это повышает достоверность принимаемой информации от внешнего источника кодограмм, позволяет исключить прием бита, изменивших свое значение под действием помех, случайных сбоев и т.п., снижает аварийность срабатывания исполнительных элементов, обеспечивает надежность и безопасность их работы.

146

Формула изобрет

е н и я

j Устройство для фиксации сбоев, со- I держащее, первьгй, второй и третий эле- ; менты И, первьй, второй и третий . ; счетчики, блок памяти, первый форми- рователь импульсов, первый дешифратор, первый элемент ИЛИ, причем груп- па .информационных выходов первого счетчика соединена с первой группой адресных входов памяти, группа информационных выходов второго счетчика соединена с группой входов первого дешифратора, инверсный выход которого соединен с первым входом первого элемента И, выход первого элемента ИЛИ соединен с первым входом- второго элемента И, отличающееся тем, что, с целью повьшения достоверности работы, в устройство введены генератор импульсов, блок синхрошг- зации, два регистра, с второго по пятьй формирователи импульсов, блок. сравнения, коммутатор, первый и второй элементы НЕ, второй элемент ИЛИ, четвертый и пятый счетчики, второй, третий и четвертый дешифраторы, причем- выход генератора импульсов соединен с входом запуска блока синхронизации, первый выход которого соединен с входом разрешения запуска второго формирователя импульсов, выход которого соединен с вторым входом второго элемента И и с тактовым . входом третьего счетчика, группа информационных выходов которого соединена с первой группой информационных

1462320

входов коммутатора, группа выходов которого соединена с второй группой адресных входов блока памяти, инфор- g мационный вход которого соединен с информационным входом первого регистра и является информационным входом устройства, вход синхронизации которого соединен с -входом сдвига перво- Q го регистра, о тактовым входом четвертого счетчика и с входом разрешения запуска первого формирователя., вход запус ка которого соединен с входами запуска третьего и четвертого 15 формирователей, первым входом третьего элемента И подключен к второму вы- . ходу блока синхронизации, третий выход которого соединен с вторым входом первого элемента И и с тактовым 20 входом второго счетчика, группа информационных выходов которого соединена с второй группой информационных входов коммутатора, первый управляющий вход которого соединен с третьим 25 входом первого элемента И и подключен к выходу первого элемента НЕ, вход которого, соединен с вторым управляющим входом коммутатора, с входом разрешения запуска третьего фор- 0 мирователя импульсов, с входом обнуления второго счетчика, с тактовым входом первого счетчика, с входом режима работы блока памяти, с первым входом второго элемента ШШ и подклю- ц чен к выходу второго элемента И, третий вход которого соединен с выходом первого формирователя импульсов, четвертый выход блока синхронизации соединен с входом запуска пятого форми- Q рователя импульсов, выход которого является выходом сигнала отсутствия контролируемой информации устройства, группа выходов первого регистра соединена с группой входов второго де- 5 шифратора, выход которого соединен с входами обнуления первого и четвертого счетчиков, с входом запуска и с входом разрешения запуска соответственно второго и пятого формировате- g лей импульсов, группа выходов четвертого счетчика соединена с группой входов третьего дешифратора, группа выходов которого соединена с группой входов первого элемента ШШ, выход g первого элемента И соединен с вторым входом второго элемента ШШ, вькод которого соединен с входом разрешения запуска четвертого формирователя импульсов, выход.которого соединен с

/

входом разрешения блока памяти, выход которого соединен с вторым входом третьего элемента И, выход которого соединен с тактовым входом пятого счетчика, группа выходов которого соединена с первой группой входов блока сравнения, вьпсод которого соединен с входом записи второго регистра, группа выходов первого счетчика соединена с группой входов четвертого дешифратора, группа выходов которого соединена с группой информа

8

LwoHHbrx ВХОДОВ второго регистра, группа выходов которого является группой выходов результата контроля устройства, группа входов начальных условий которого соединена с второй группой входов блока сравнения, выход первого дешифратора соединен с входом второго элемента НЕ, выход которого соединен с входом останова второго счетчика, выход третьего формирователя импульсов соединен с входом обнуления пятого счетчика.

ф|/е..2

| Устройство для фиксации сбоев | 1979 |

|

SU860074A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для регистрации сигналов неисправности | 1982 |

|

SU1132291A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

Авторы

Даты

1989-02-28—Публикация

1987-06-22—Подача