Изобретение относится к области вычислительной техники и может быть использовано для контроля информации методом сигнатурного анализа.

Цель изобретения - повышение быстродействия анализатора.

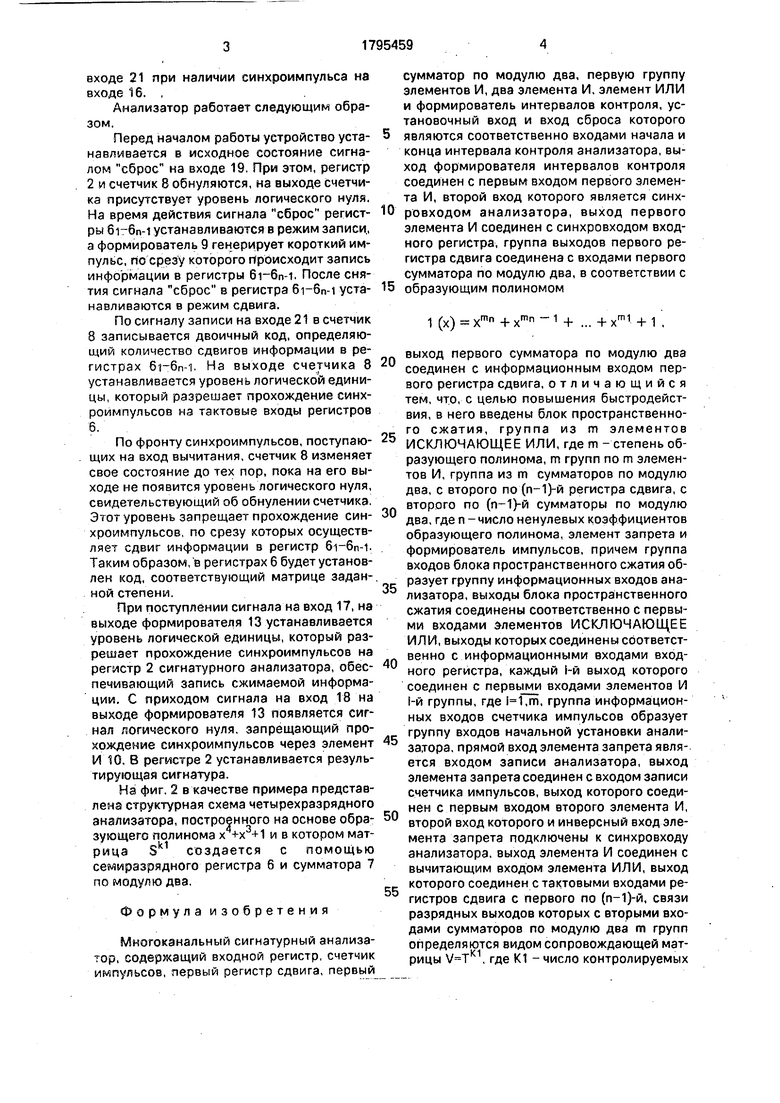

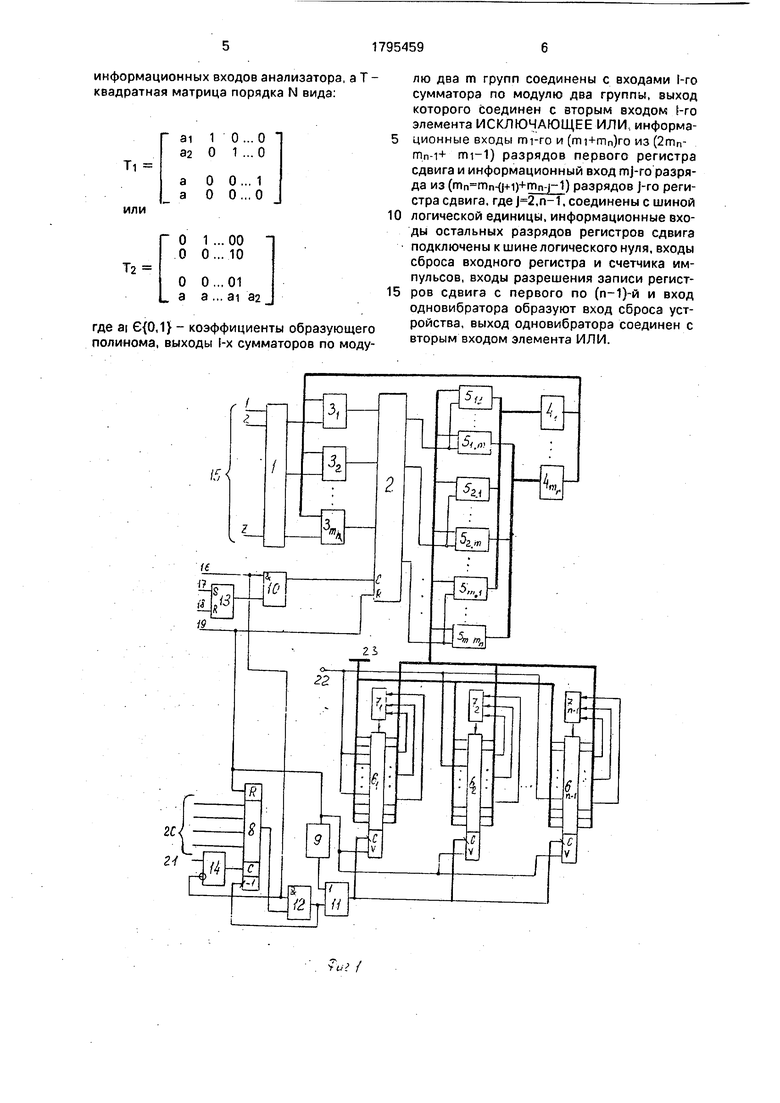

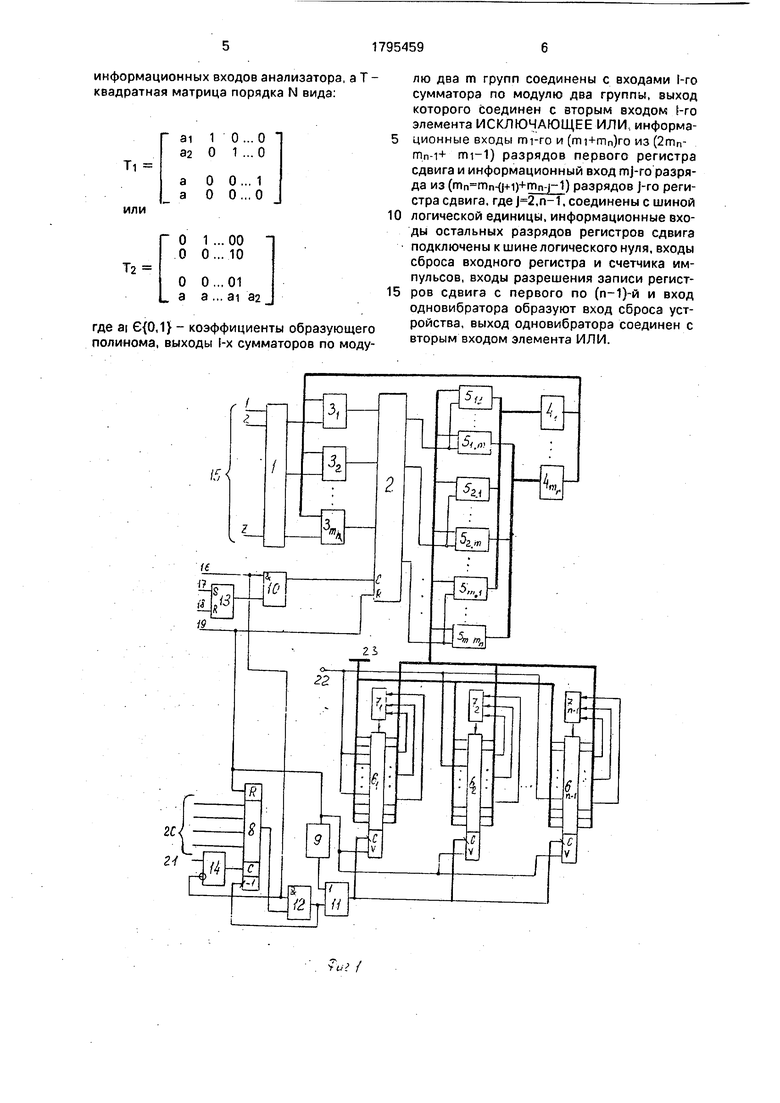

На фиг. 1 представлена функциональная схема анализатора: на фиг. 2 - пример его реализации.

Анализатор (фиг. 1) содержит блок 1 пространственного сжатия, входной регистр 2, группу из m элементов. Исключающее ИЛИ 3, группу из m сумматоров 4 по модулю два, m групп по m элементов И 5, (п-1) регистров 6 сдвига, (п-1) сумматоров 7 по модулю два, счетчик 8 импульсов, формирователь 9 импульсов, элемент И 10, элемент ИЛИ 11, элемент И 12, формирователь 13 интервалов контроля, элемент запрета 14, группу 15 информационных входов, син- хровход 16, вход начала 17 и вход 18 конца интервала контроля, вход 19.сброса, группу

20 входов начальной установки и вход 21 записи.

На фиг. 1 показаны также шина 22 логической единицы и шина 23 логического нуля.

Блок 1 предназначен для сжатия очередной вводимой группы разрядов кода, результат которого суммируется по модулю два с помощью элементов Исключающее ИЛИ 3 с результатом умножения сигнатуры, полученной на предыдущем такте, на матрицу Sz, где z - число задействованных входов анализатора. Умножение осуществляется с помощью элементов 5 И и сумматоров 4.

Промежуточная сигнатура хранится в регистре 2, а сигналы, соответствующие элементам матрицы Sz, устанавливаются на входах элементов И 5 с помощью регистров б, Элементы матрицы формируются в регистрах 6 с помощью сумматоров 7, счетчика 8 и элементов ИЛИ 11, И 12,

Логический элемент 14 предназначен для запрета прохождения сигнала записи на

ел

с

XI Ю

ел

ел

Ю

входе 21 при наличии синхроимпульса на входе 16. ,

Анализатор работает следующим образом.

Перед началом работы устройство устанавливается в исходное состояние сигналом сброс на входе 19. При этом, регистр 2 и счетчик 8 обнуляются, на выходе счетчика присутствует уровень логического нуля. На время действия сигнала сброс регистры устанавливаются в режим записи,, а формирователь 9 генерирует короткий импульс, по срезу которого Происходит запись информации в регистры 6i-6n-t. После снятия сигнала сброс в регистра 6i-6n-i устанавливаются в режим сдвига.

По сигналу записи на входе 21 в счетчик 8 записывается двоичный код, определяющий количество сдвигов информации в регистрах 6i-6n-i. На выходе счетчика 8 устанавливается уровень логической единицы, который разрешает прохождение синхроимпульсов на тактовые входы регистров 6.

По фронту синхроимпульсов, поступающих на вход вычитания, счетчик 8 изменяет свое состояние до тех пор, пока на его выходе не появится уровень логического нуля, свидетельствующий об обнулении счетчика. Этот уровень запрещает прохождение синхроимпульсов, по срезу которых осуществляет сдвиг информации в регистр 6i-6n-L Таким образом, в регистрах 6 будет установлен код, соответствующий матрице задан-, ной степени.

При поступлении сигнала на вход 17, на выходе формирователя 13 устанавливается уровень логической единицы, который разрешает прохождение синхроимпульсов на регистр 2 сигнатурного анализатора, обеспечивающий запись сжимаемой информации. С приходом сигнала на вход 18 на выходе формирователя 13 появляется сигнал логического нуля, запрещающий прохождение синхроимпульсов через элемент И 10. В регистре 2 устанавливается результирующая сигнатура.

На фиг. 2 в качестве примера представлена структурная схема четырехразрядного анализатора, построенного на основе образующего полинома х +х +1 и в котором матрица Sk1 создается с помощью семиразрядного регистра 6 и сумматора 7 по модулю два.

Формула изобретения

Многоканальный сигнатурный анализатор, содержащий входной регистр, счетчик импульсов, первый регистр сдвига, первый

сумматор по модулю два, первую группу элементов И, два элемента И, элемент ИЛИ и формирователь интервалов контроля, установочный вход и вход сброса которого

являются соответственно входами начала и конца интервала контроля анализатора, выход формирователя интервалов контроля соединен с первым входом первого элемента И, второй вход которого является синхровходом анализатора, выход первого элемента И соединен с синхровходом входного регистра, группа выходов первого регистра сдвига соединена с входами первого сумматора по модулю два, в соответствии с

образующим полиномом

1 (х) Xmn + xmn 1 + ... +xm1 +1

0

5

5

0

выход первого сумматора по модулю два

соединен с информационным входом первого регистра сдвига, отличающийся тем, что, с целью повышения быстродействия, в него введены блок пространственного сжатия, группа из m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, где m - степень образующего полинома, m групп по m элементов И, группа из m сумматоров по модулю два, с второго по (п-1)-й регистра сдвига, с

- второго по (п-1)-й сумматоры по модулю два, где п - число ненулевых коэффициентов образующего полинома, элемент запрета и формирователь импульсов, причем группа входов блока пространственного сжатия об разует группу информационных входов анализатора, выходы блока пространственного сжатия соединены соответственно с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены сбответст- п венно с информационными входами входного регистра, каждый i-й выход которого соединен с первыми входами элементов И 1-й группы, где ,т, группа информационных входов счетчика импульсов образует группу входов начальной установки анализатора, прямой вход элемента запрета является входом записи анализатора, выход элемента запрета соединен с входом записи счетчика импульсов, выход которого соединен с первым входом второго элемента И, второй вход которого и инверсный вход элемента запрета подключены к синхровходу анализатора, выход элемента И соединен с вычитающим входом элемента ИЛИ, выход

которого соединен с тактовыми входами регистров сдвига с первого по (п-1)-й, связи разрядных выходов которых с вторыми входами сумматоров по модулю два m групп определяются видом сопровождающей матрицы , где К1 - число контролируемых

информационных входов анализатора, а Т - квадратная матрица порядка N вида:

Ti

или

О1 ... 00

О0 ...10

О0... 01

аа ... ai aa

где ai G{0,1} - коэффициенты образующего полинома, выходы 1-х сумматоров по модулю два m групп соединены с входами 1-го сумматора по модулю два группы, выход которого соединен с вторым входом 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ., информационные входы mi-re и (mi+mn)ro из (2mn- mn-i+ гтц-1) разрядов первого регистра сдвига и информационный вход mj-ro разряда из ()+mn-rl) разрядов J-ro регистра сдвига, где ,n-1. соединены с шиной

логической единицы, информационные входы остальных разрядов регистров сдвига подключены к шине логического нуля, входы сброса входного регистра и счетчика импульсов, входы разрешения записи регистров сдвига с первого по (п-1)-й и вход одновибратора образуют вход сброса устройства, выход одновибратора соединен с вторым входом элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1987 |

|

SU1427370A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Сигнатурный анализатор | 1989 |

|

SU1624455A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1430956A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1336010A1 |

| Сигнатурный анализатор | 1986 |

|

SU1383360A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1797118A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Сигнатурный анализатор | 1989 |

|

SU1737452A2 |

| Сигнатурный анализатор | 1986 |

|

SU1383358A1 |

Изобретение относится к области вычислительной техники и может быть использовано для контроля информации методом сигнатурного анализа. Цель изобретения - повышение быстродействия анализатора. Поставленная цель достигается за счет того, что сигнатура, полученная на очередном такте, определяется суммированием по модулю два вновь вводимой информации и промежуточной сигнатуры, умноженной на матрицу S , значения элементов которой устанавливаются в процессе начальной установки анализатора. 2 ил.

. W /

Фиг. 2

| Анализатор сигнатур параллельного потока данных | 1983 |

|

SU1403065A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сигнатурный анализатор | 1983 |

|

SU1180896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-15—Публикация

1990-09-21—Подача