Изобретение относится к-вычислительной технике и может быть использовано в устройствах контроля правильности выполнения программ вычислительных систем.

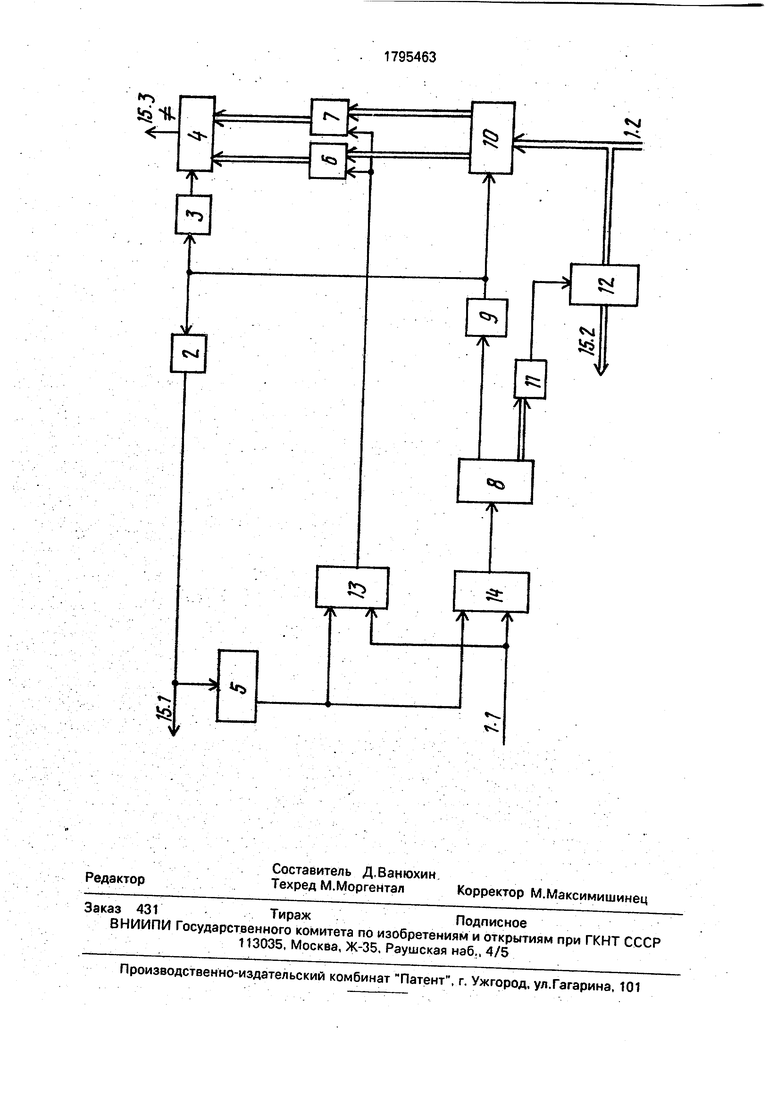

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения двухкратного повторения контролируемой последовательности команд. . ; . . /.... . ;. - .-./ v-:.-:..- /; ./ .Схема устройства показана на чертеже.

Устройство содержит вход импульса чтения команды 1.1, вход адреса счетчика команд 1.2, формирователи импульсов 2.3, схему сравнения 4, элемент задержки 5, накапливающие сумматоры 6,7, счетчик 8, Т- триггер 9, коммутатор 10, элемент ИЛИ-НЕ С первым инверсным входом 11, регистр 12, элементы ИЛИ 13, 14, выходы 15.1, 15.2, 15.3/ .;...; ....; , . .:/./ : Устройство работает следующим образом.

В исходном состоянии счетчик 8, триггер 9, регистр 12 и накапливающие сумматоры 6, 7 находятся в нулевом состоянии. Коммутатор 10 подключает вход 1.2 к информационному входу накапливающему сумматору 6.

На вход 1.1 поступают импульсы чтения команды и, проходя через элементы ИЛИ 14, увеличивают состояние счётчика 8 на единицу, а также, Проходя через элемент ИЛИ 13, поступают на управляющие входы накапливающих сумматоров и разрешают накопление (сложение) кодов адреса счетчика команд, поступающих на вход 1.2,-в сумматоре 6. Содержимое сумматора 7 в данном случае не изменено (прибавляется код 000...0). При состоянии счетчика 8000...01 открывается элемент ИЛИ-НЕ с первым инверсным входом и разрешает запись очередного (первого в рассматриваемой последовательности) коды адреса счетчика команд в регистре 12. В счетчике 8 в любой момент времени содержится число выполненных команд в контролируемой последовательности (емкость счетчика выбиХ4

N0

OI

4 О

СА)

рается из условий оптимизации вычислительного процесса по быстродействию с учетом интенсивности необнаруживаемых системой контроля сбоев), а в одном из накапливающих сумматоров - суммарный код адресов выполненных команд.

При переполнении счетчика 8 импульс появляется на выходе переполнения этого счетчика и, поступая на Т-триггер 9, переводит его в единичное состояние. В этот момент времени в регистре 12 записан код адреса первой команды из контролируемой последовательности, а в сумматоре 6 - суммарный код исполненных команд контролируемой последовательности.

По перепаду потенциала в выходе Т- триггера с низкого на высокий коммутатор 10 подключает вход 1.2 к накапливающему сумматору 7, формирователь 2 вырабатывает импульс, который поступает на выход 15.1 останова вычислений. По этому сигналу на счетчик адреса команд ЭВМ записывается содержимое регистра 12 и передается управление блоку микропрограммного управления для выполнения требуемой операции. Элемент задержки 5 срабатывает после устойчивой переписи кода из регистра 12 на счетчик адреса команд ЭВМ. Импульс, Задержанный в элементе 5, поступает через элемент ИЛИ 14 на вход счетчика 8, а также через элемент ИЛИ 13 на управляющие входы накапливающих сумматоров 6 и 7.

Таким образом, контролируемая последовательность команд повторяется в ЭВМ, а коды адресов, выполняемых команд накапливаются в сумматоре 7. При переполнении счетчика 8 импульс переполнения с этого элемента поступает на Т-триггер 9, переводя его в нулевое состояние. Формирователь импульсов 3 вырабатывает импульс по периоду потенциала с высокого на низкий. Этот импульс поступает на вход управления схемы 4, в которой производится сравнение содержимого сумматоров 6 и 7. Если коды в элементах б и 7 равны, то устройство продолжает контроль очередной последовательности команд программы аналогичным образом. Иначе импульс появляется на выходе 15.3 устройства, сигнализируя об ошибке в контролируемой последовательности команд.

Следует заметить, что в элементах б, 7 может произойти переполнение (потеря

единицы старшего разряда). Однако, в этом случае работоспособность устройства не нарушается, так как в элементах б, 7 происходят аналогичные процессы.

Формул а изобретения

Устройство для контроля правильности выполнения последовательности команд в

программе, содержащее Т-триггер, коммутатор, регистр, схему сравнения, первый формирователь импульсов, элемент задержки, дешифратор, причем выход Т-триггера соединен с управляющим входом

коммутатора и через первый формирователь импульсов с входом элемента задержки, выход регистра является информационным выходом устройства, от - личающее с я тем, что, с целью расширения функциональных возможностей за счет обеспечения двукратного повторения контролируемой последовательности-команд, оно содержит второй формирователь импульсов, два элемента ИЛИ. счетчик, два

накапливающих сумматора, причем вход чтения команды устройства подключен к первым входам элементов ИЛИ, выход первого элемента ИЛИ подключен к управляющим входам накапливающих сумматоров,

информационные входы которых подключены соответственно к первому и второму вы- ходам коммутатора, информационный вход которого и информационный вход регистра подключены к адресному входу устройства,

информационный выход счетчика подключен к входу дешифратора, выход которого подключен к входу управления записью регистра, выход переполнения счетчика подключен к входу Т-триггера, выход которого

подключен к входу второго формирователя импульсов, выход которого подключен к управляющему входу схемы сравнения, выход первого формирователя импульсов является выходом останова устройства, выход элемента задержки подключен к вторым входам элементов ИЛИ, первый и второй информационные входы схемы сравнения подключены к выходам соответствующих накапливающих сумматоров, выход второго

элемента ИЛИ подключен к счетному входу счетчика, выход неравенства схемы сравнения является выходом ошибки устройства.

55

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации неисправностей | 1986 |

|

SU1429116A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1985 |

|

SU1288751A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Устройство для измерения параметров частотных датчиков | 1989 |

|

SU1705757A1 |

| Устройство для контроля хода программ ЭВМ | 1987 |

|

SU1430960A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| Устройство для передачи информации | 1989 |

|

SU1736001A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах рбработки данных для контроля правильности выполнения программ. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения двухкратного повторения контролируемой последовательности команд. Поставленная цель достигается введением в состав устройства двух формирователей импульсов, схемы сравнения, элемента ИЛИ, двух накапливающих сумматоров, коммутатора, регистра, Т-триггера, элемента ИЛИ-НЕ с первым инверсным входом и соответствующих связей. 1 ил.

| Устройство для контроля времени выполнения программы | 1985 |

|

SU1298753A1 |

| Устройство для контроля программ | 1988 |

|

SU1552189A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-02-15—Публикация

1990-03-20—Подача