ел

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1989 |

|

SU1742823A1 |

| Устройство для управления обменом процессора с памятью | 1988 |

|

SU1667087A1 |

| Устройство для управления обменом информацией процессора с памятью | 1988 |

|

SU1587525A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

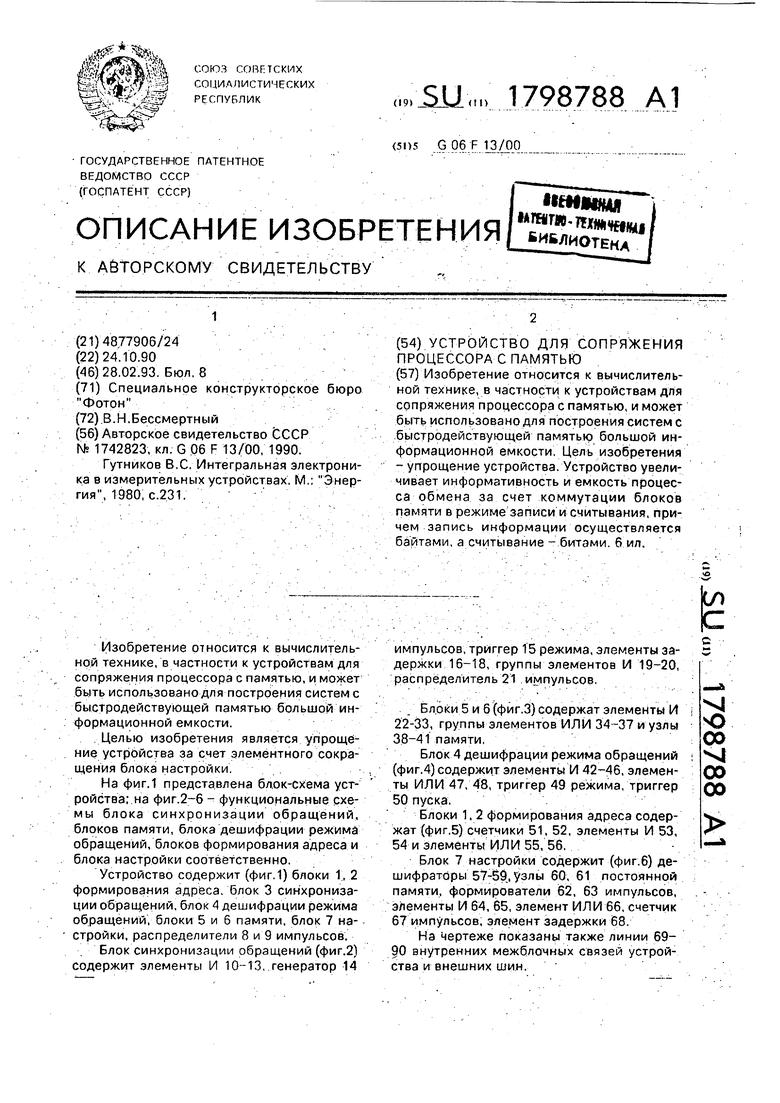

Изобретение относится к вычислительной технике, в частности к устройствам для сопряжения процессора с памятью, и может быть использовано для построения систем с .быстродействующей памятью большой информационной емкости. Цель изобретения - упрощение устройства. Устройство увеличивает информативность и емкость процесса обмена за счет коммутации блоков памяти в режиме записи и считывания, причем запись информации осуществляется байтами, а считывание -битами. 6 ил.

Изобретение относится к вычислительной технике, в частности к устройствам для сопряжения процессора с памятью, и может быть использовано для построения систем с быстродействующей памятью большой информационной емкости.

.Целью изобретения является упрощение устройства за счет элементного сокращения блока настройки..

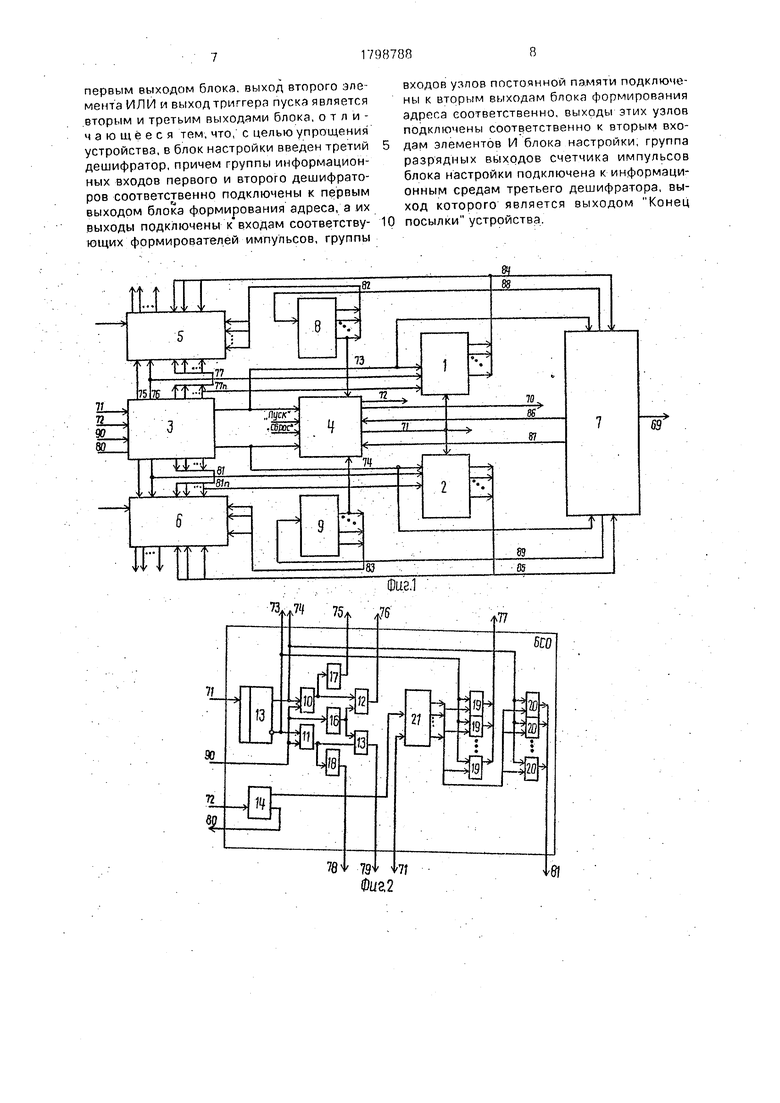

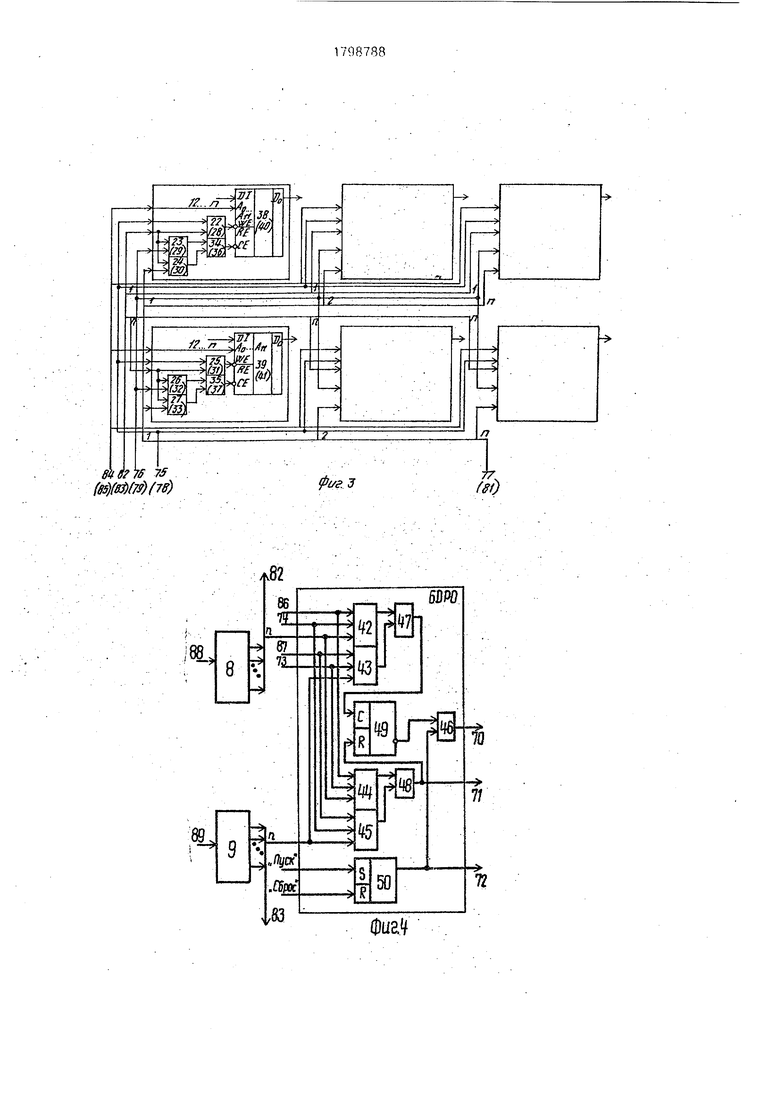

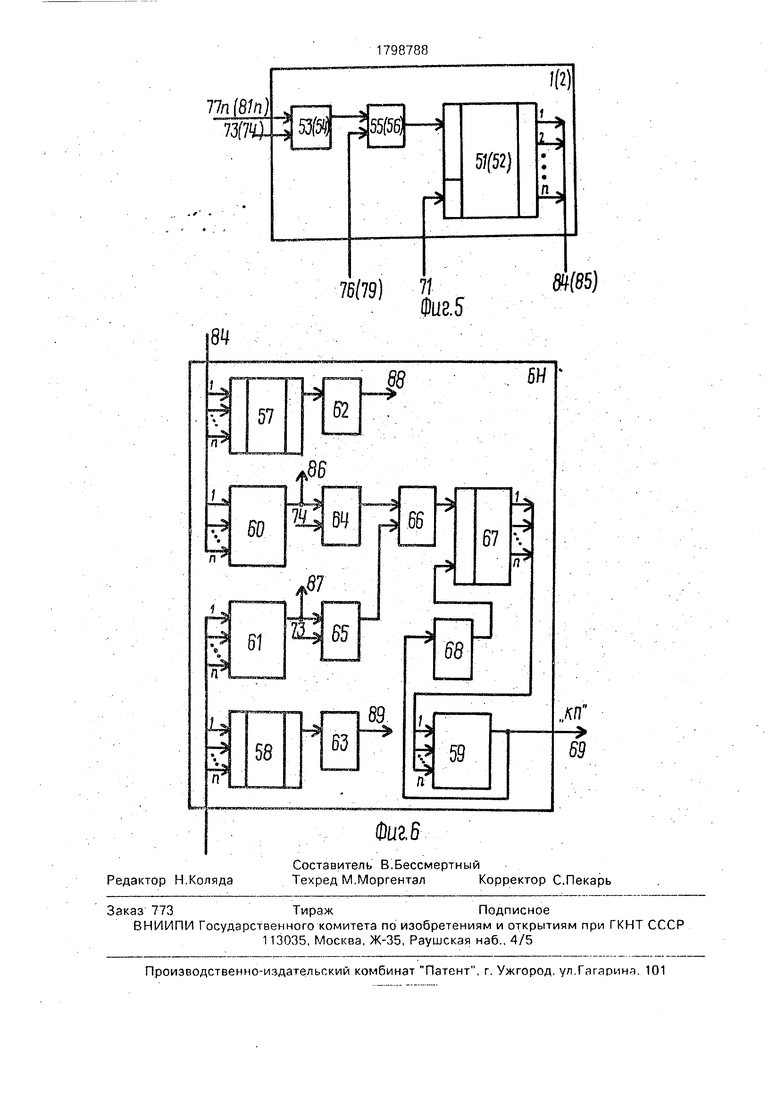

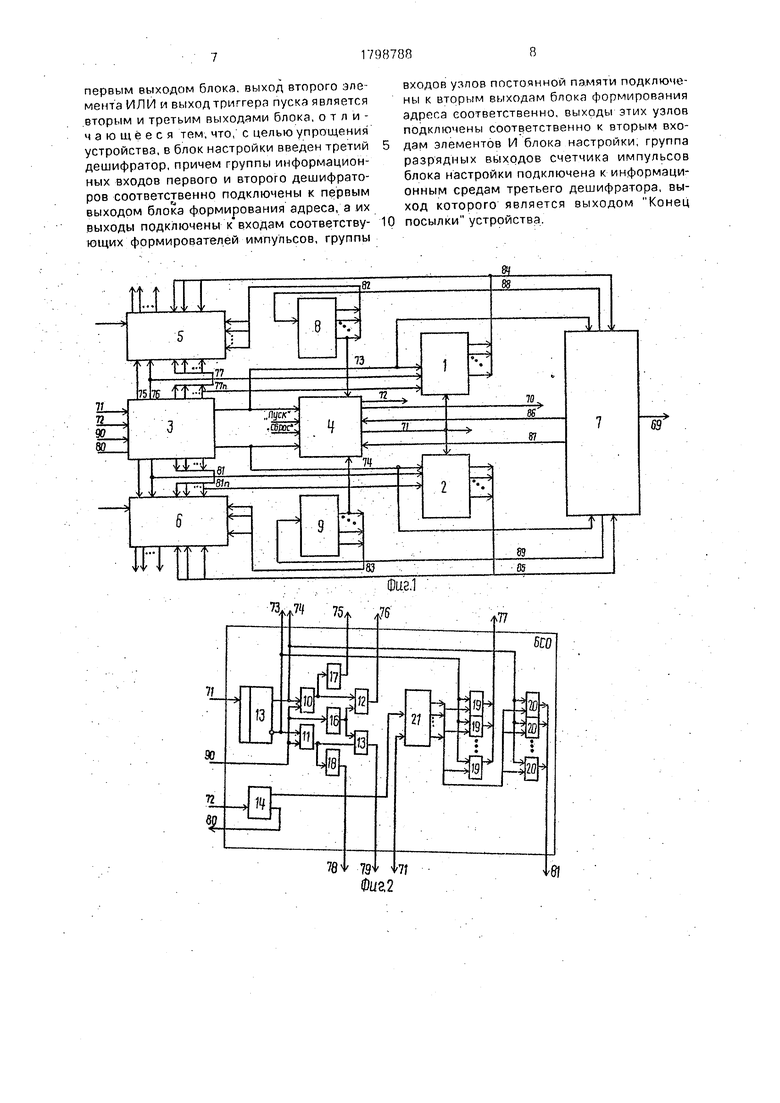

На фиг.1 представлена блок-схема устройства; на фиг.2-6 - функциональные схемы блока синхронизации обращений, блоков памяти, блока дешифрации режима обращений, блоков формирования адреса и блока настройки соответственно.

Устройство содержит (фиг.1) блоки 1, 2 формирования адреса, блок 3 синхронизации обращений, блок 4 дешифрации режима обращений, блоки 5 и 6 памяти, блок 7 настройки, распределители 8 и 9 импульсов.

Блок синхронизации обращений (фиг.2) содержит элементы И 10-13,.генератор 14

импульсов, триггер 15 режима, элементы задержки 16-18, группы элементов И 19-20, распределитель 21 .импульсов.

, Блоки 5 и 6 (фиг.3) содержат элементы И 22-33, группы элементов ИЛИ 34-37 и узлы 38-41 памяти,

Блок 4 дешифрации режима обращений (фиг.4) содержит элементы И 42-46, элементы ИЛИ 47, 48, триггер 49 режима, триггер 50 пуска.

Блоки 1, 2 формирования адреса содержат (фиг.5) счетчики 51, 52, элементы И 53, 54 и элементы ИЛ И 55, 56,Блок 7 настройки содержит (фиг.6) дешифраторы 57-59, УЗЛЫ 60, 61 постоянной памяти, формирователи 62, 63 импульсов, элементы И 64, 65, элемент ИЛИ 66, счетчик 67 импульсов, элемент задержки 68.

На чертеже показаны также линии 69- 90 внутренних межблочных связей устройства и внешних шин,

VI ю

00 VI 00 00

Устройство работает следующим образом.

Исходно счетчики сброшены, триггер 49 установлен в нулевое положение, например, в момент подачи питания (не показано), триггер 15 может быть установлен & любое положение, например, в единичное.

Сигнал Пуск устанавливает триггер 50 в единичное положение, при этом открыва-. ется элемент И 46, на выход которого поступает сигнал с выхода триггера 49 в качестве сигнала ЗАН, указывающего на начало обмена, при этом также запускается генера тор 14, который вырабатывает импульсы синхронизации задатчика (СХЗ), поступающие в процессор.

Ответной реакцией процессора на.импульсы СХЗ является вырабатывание импульсов синхронизации источника (СХИ), которые являются импульсами частоты записи в блоки памяти информации, поступающий к ним по шине данных.Шина данных поразрядно подключена к входам Д1 узлов 38, 39 первого и узлов 40, 41 второго блоков памяти. Т.о. информация, подлежащая записи в блоки памяти, находится во взаимосвязи с импульсами СХИ, а запись производится параллельно по всем входам блоков памяти, например, байтами.

Единичное положение триггера соответствует режиму записи в первом 38 и втором 39 узлах памяти первого блока памяти, коммутируемые поочередно распределителем 8 через элементы И 22, 23 и И 25, 26 соответственно, а также режиму считывания для первого 40 и второго 41 узлов памяти второго блока памяти, коммутируемых распределителем 9 через элементы И 30 и 33 соответственно, при этом считывание информации происходит по битам за счет сигналов управления, поступающих с выхода распределителя 21 через элементы И узла 20, с помощью которых разворачивается по-, следовательное обращение к блокам памяти.

Т.о., в режиме считывания информации из блоков памяти выбирается последовательно по битам из записанных ранее байтов.

Смена адреса обращения в блоках памяти в режиме считывания происходит с помощью соответствующего счетчика 51 или 52, управляемого через соответствующий элемент ИЛИ 55 или 56 по импульсам в последнем разряде распределителя 21, которые появляются в линии 77 (для счетчика 51) или в линии 81 (для счетчика 52).

В режиме записи, например, в узлы 38 или 39 первого блока памяти импульсы частоты СХИ поступают на элемент 16 задержки и далее через открытый элемент И 10 на элемент 17 задержки и далее на открытые элементы И 22, 23, при этом на вход Е/РЕ узла 38 первого блока памяти импульс СХИ

проходит раньше, чем на СЕ, т.к. время срабатывания элемента 17 задержки меньше, чем время срабатывания элемента 16 задержки.:

Окончание импульсов СХИ по входам

Е/РЕ и СЕ блока памяти происходит одновременно, так как по окончании импульсов СХИ элемент 16 задержки отключается при закрывании элемента И 12,а время срабатывания элемента 17 задержки равно времени

срабатывания элемента И 12 и единичного элемента И 23 при равенстве времени срабатывания единичных элементов И, а также ИЛИ 22 и 36 соответственно.

Смена адреса обращения в блоках памяти в режиме записи происходит с помощью соответствующего счетчика 51 или 52 через соответствующий элемент ИЛИ 55 или 56 по окончанию импульсов СХИ в линиях 76 или 79 соответственно. Код формата

посылки хранится в перестраиваемых постоянных запоминающих устройствах ПЗУ 60 и 61. Код на выходах блоков формирователей адреса (БФА1 и БФА2) управляет состоянием выходов ПЗУ 60 и 61. ПЗУ

0 программируется на длительность формата посылки, например, если формат посылки (длительность строки изображения в единицах разложения (линий) мм) равен 800, то код формата посылки будет кратным этому

5 числу: 800, 1600, 2400 и т.д., т.о. в ПЗУ задан текущий адрес конца формата посылки: Количество сигналов с выходов ПЗУ через элементы 64, 65, 66 формируется счетчиком 67, выходы этого счетчика подключены к де0 шифратору 59, настроенный на код длительности посылки и, когда на выходе счетчика 67 достигнет этого значения, то дешифратор 59 выдает сигнал в шину КП, свидетельствующий об окончании посылки, т.е. об окон5 чании процесса обмена памяти и процессора. . .

Дешифраторы 57, 58 настроены на кодовое состояние счетчиков 1, 2, соответственно, состояние которых указывает на

0 невозможность дальнейшего участия блоков памяти в приеме информации в связи с тем, что их объем исчерпан. Сигналы с выхода дешифраторов 57 и 58 через соответствующие формирователи 62. 63 воздействуют

5 на распределители 8. 9 для подключения, очередных блоков по указанной выше схеме их подключения.

Процесс записи информации происходит быстрее считывания, поэтому имеет смысл после заполнения объема блоков памяти при записи информации освободить общую тину процессора. Освобождение общей шины процессора осуществляется снятием сигнала ЗАН при опрокидывании триггера 49 в единичное состояние. Это происходит в режиме записи, когда распределители 8 и 9 выбирают последний узел блоков памяти (сигналы в линиях 82 и 83) и в момент совпадения кода адреса обращения с кодом формата посылки ПЗУ 60, 61. Такое состояние фиксируется элементами 42 или 43 через элемент ИЛИ 47.

Возврат триггера 49 в нулевое состояние осуществляется теми же сигналами, только в режиме.считывания для блоков па- мяти, и фиксируется элементами И 44 или 45 через элемент ИЛИ 48.

Устройство выгодно отличается от указанного прототипа тем, что с его помощью можно программно задавать адрес в блоке памяти, в котором хранится информация, соответствующая концу формата посылки (концу строки изображения), при значительно меньших материальных затратах на со- здание блока настройки.

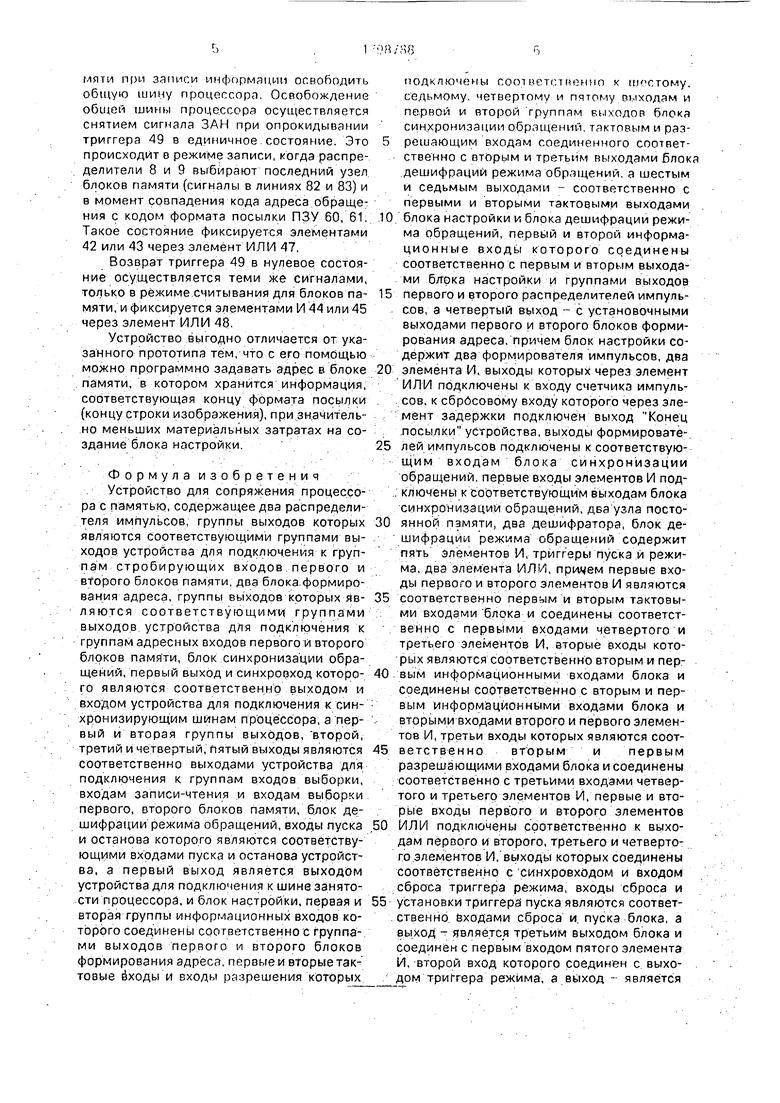

Формула изобретения . Устройство для сопряжения процессора с памятью, содержащее два распределителя импульсов, группы выходов которых являются соответствующими группами выходов устройства для подключения к группам стробирующих входов.первого и второго блоков памяти, два блока.формирования адреса, группы выходов которых яв- ляются соответствующим группами выходов устройства для подключения к группам адресных входов первого и второго блоков памя ти, блок синхронизации обращений, первый выход и синхровход которо- го являются соответственно выходом и входом устройства для подключения к син- хронизирующим шинам процессора, а пер- вый и вторая группы выходов, второй, третий и четвертый, пятый выходы являются соответственно выходами устройства для подключения к группам входов выборки, входам записи-чтения и входам выборки первого, второго блоков памяти, б.лок дешифрации режима обращений, входы пуска и останова которого являются соответствующими входами пуска и останова устройства, а первый выход является выходим устройства для подключения к шине занятости процессора, и блок настройки, первая и вторая группы информационных входов которого соединены соответственное группами выходов первого и второго блоков формирования адреса, первые и вторые так- товые входы и входы разрешения которых

подключены соот ветстненно к шестому, седьмому, четвертому и пятому выходам и первой и второй группам выходов блока синхронизации обращений, тактовым и разрешающим входам соединенного соответственно с вторым и третьим выходами блок дешифраций режима обращений, а шестым и седьмым выходами - соответственно с первыми и вторыми тактовыми выходами блока настройки и блока дешифрации режима обра-щений, первый и второй информационные входы которого соединены соответственно с первым и вторым выходами бярка настройки и группами выходов первого и второго распределителей импульсов, а четвертый выход с установочными выходами первого и второго блоков формирования адреса, причем блок настройки содержит два формирователя импульсов, два элемента И, выходы которых через элемент

ИЛИ подключены к входу счетчика импульсов, к сбросовому входу которого через эле: мент задержки подключен выход Конец .посылки устройства, выходы формирователей импульсов подключены к соответствующим входам блока синхронизации обращений, первые входы элементов И под; ключёны к соответствующим выходам блока синхронизации обращений, два узла постоянной памяти, два дешифратора, блок дешифрации режима обращений содержит пять элементов И, триггеры пуека и режима, два элемента ), причем первые входы первого и второго элементов И являются соответственно первым и вторым тактовыми входами блока и соединены соответственно с первыми входами четвертого и третьего элементов И, вторые входы которых являются соответственно вторым и пер.вым информационными входами блока и соединены соответственно с вторым и первым информационными входами блока и вторыми входами второго и первого элементов И, третьи входы которых являются соответственно вторым и первым разрешающими входами блока и соединены соответственно с третьими входами четвертого и третьего элементов И, первые и вторые входы первого и второго элементов ИЛИ подключены соответственно к выходам первого и второго, третьего и четвертого .элементов И, выходы которых соединены соответственно с синхровходом и входом сброса триггера режима, входы сброса и установки триггера пуска являются соответственно, входами сброса и. пуска блока, а выход - является третьим выходом блока и соединен с первым входом пятого элемента И, второй вход которого соединен с выходом триггера режима, а выход - является

первым выходом блока, выход второго элемента ИЛИ и выход триггера пуска является .вторым и третьим выходами блока, отличающееся тем, что, с целью упрощения устройства, в блок настройки введен третий дешифратор, причем группы информационных входов первого и второго дешифраторов соответственно подключены к первым выходом блока формирования адреса, а их .выходы подключены к входам соответствующих формирователей импульсов, группы

0

входов узлов постоянной памяти подключены к вторым выходам блока формирования адреса соответственно, выходы этих узлов подключены соответственно к вторым входам элементов И блока настройки, группа разрядных выходов счетчика импульсов блока настройки подключена к информационным средам третьего дешифратора, выход которого является выходом Конец посылки устройства.

Фиг,1 ..

| Устройство для сопряжения процессора с памятью | 1989 |

|

SU1742823A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гутников B.C | |||

| Интегральная электроника в измерительных устройствах | |||

| М.: Энергия, 1980;с.231. | |||

Авторы

Даты

1993-02-28—Публикация

1990-10-24—Подача