Изобретение относится к вычислительной технике, в частности к устройствам для сопряжения с памятью, и может быть использовано для построения систем с быстродействующей памятью большой информационной емкости.

Цель изобретения является повышение достоверности работы устройства при передаче документов (в случае изменения формата посылки) за счет обнаружения текущего адреса границ формата в адресном поле блока памяти.

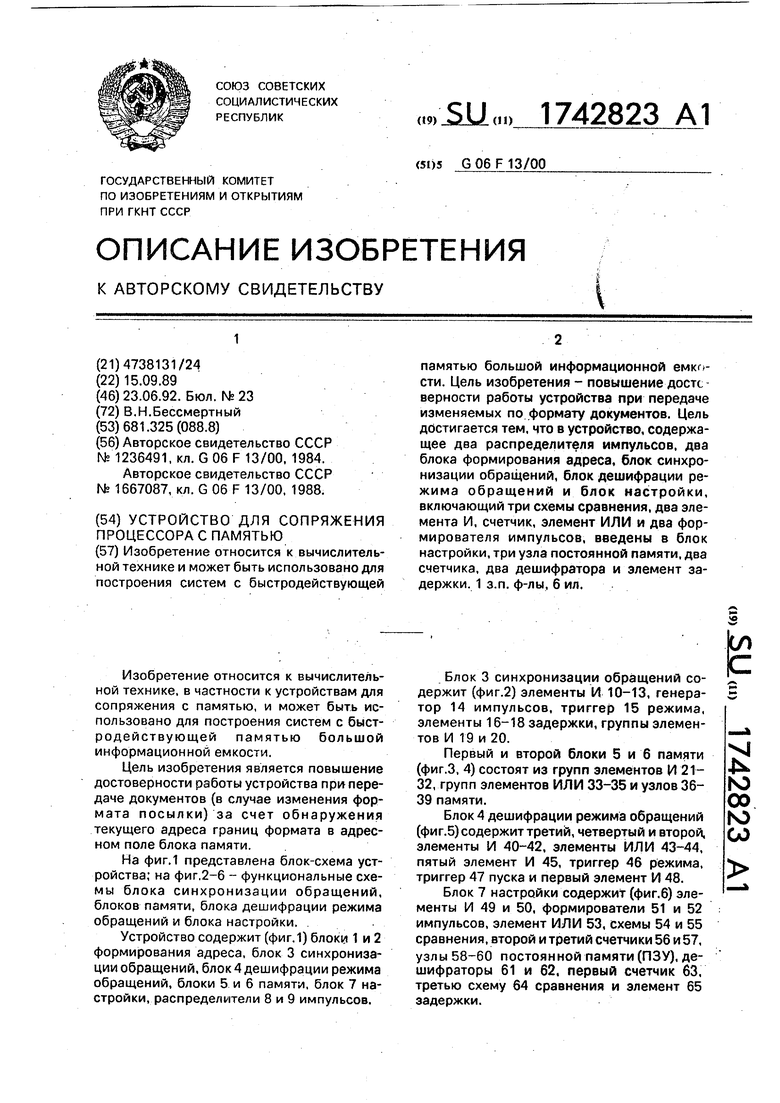

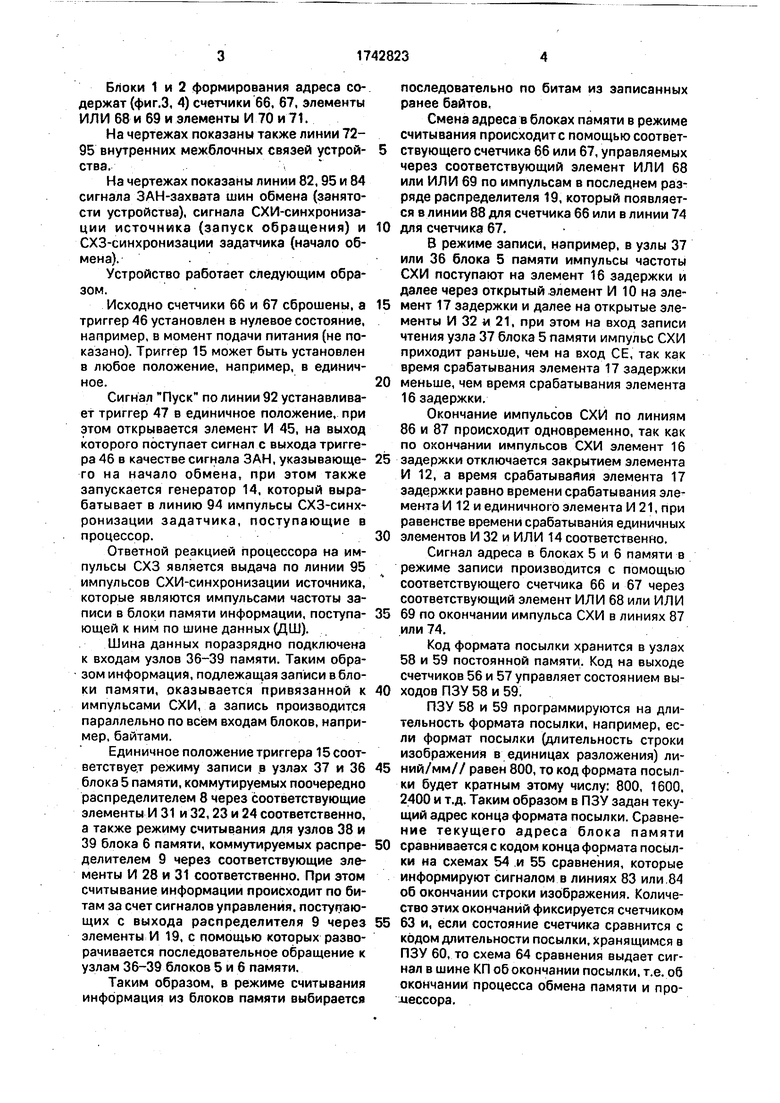

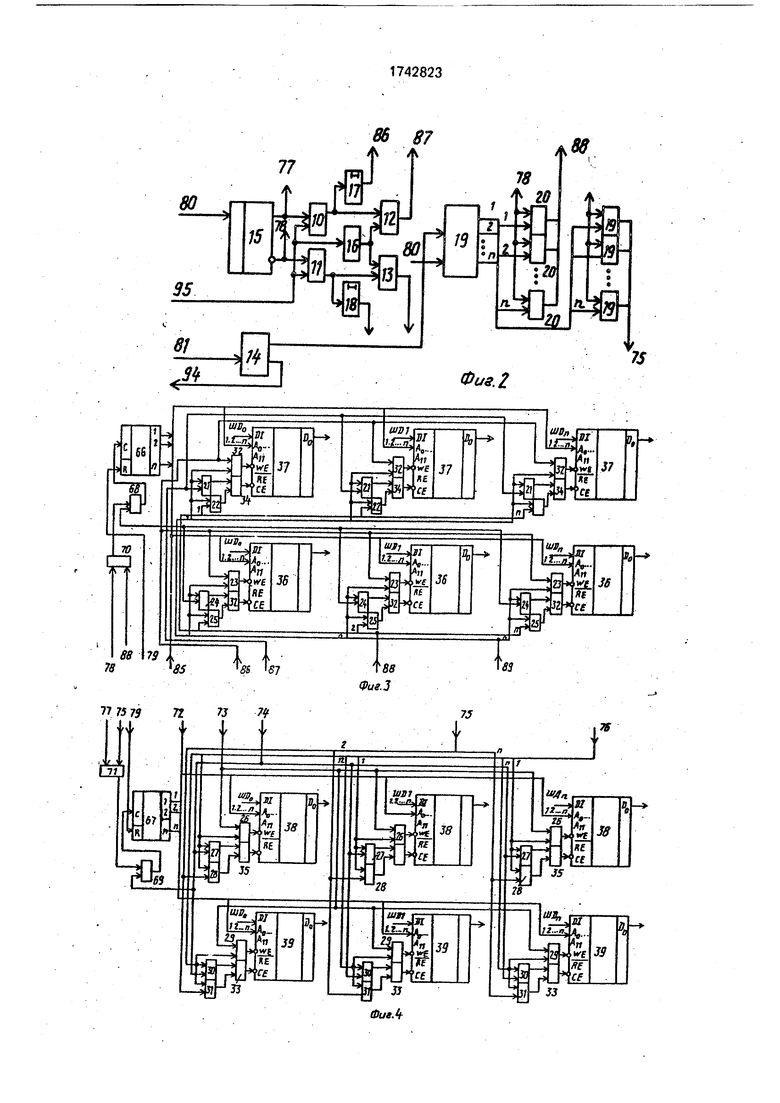

На фиг.1 представлена блок-схема устройства; на фиг,2-6 - функциональные схемы блока синхронизации обращений, блоков памяти, блока дешифрации режима обращений и блока настройки.

Устройство содержит (фиг.1) блоки 1 и 2 формирования адреса, блок 3 синхронизации обращений, блок 4 дешифрации режима обращений, блоки 5 и 6 памяти, блок 7 настройки, распределители 8 и 9 импульсов.

Блок 3 синхронизации обращений содержит (фиг.2) элементы И 10-13, генератор 14 импульсов, триггер 15 режима, элементы 16-18 задержки, группы элементов И 19 и 20.

Первый и второй блоки 5 и 6 памяти (фиг.З, 4) состоят из групп элементов И 21- 32, групп элементов ИЛИ 33-35 и узлов 36- 39 памяти.

Блок 4 дешифрации режима обращений (фиг.5) содержит третий, четвертый и второй, элементы И 40-42, элементы ИЛИ 43-44, пятый элемент И 45, триггер 46 режима, триггер 47 пуска и первый элемент И 48.

Блок 7 настройки содержит (фиг.6) элементы И 49 и 50, формирователи 51 и 52 импульсов, элемент ИЛИ 53, схемы 54 и 55 сравнения, второй и третий счетчики 56 и 57, узлы 58-60 постоянной памяти (ПЗУ), дешифраторы 61 и 62, первый счетчик 63, третью схему 64 сравнения и элемент 65 задержки.

&

fe

si

ГО 00 N СО

Блоки 1 и 2 формирования адреса содержат (фиг.З, 4) счетчики 66, 67, элементы ИЛИ 68 и 69 и элементы И 70 и 71.

На чертежах показаны также линии 72- 95 внутренних межблочных связей устройства.

На чертежах показаны линии 82,95 и 84 сигнала ЗАН-захвата шин обмена (занятости устройства), сигнала СХИ-синхрониза- ции источника (запуск обращения) и СХЗ-синхронизации задатчика (начало обмена)..

Устройство работает следующим образом.

Исходно счетчики 66 и 67 сброшены, а триггер 46 установлен в нулевое состояние, например, в момент подачи питания (не показано). Триггер 15 может быть установлен в любое положение, например, в единичное.

Сигнал Пуск по линии 92 устанавливает триггер 47 в единичное положение, при этом открывается элемент И 45, на выход которого поступает сигнал с выхода триггера 46 в качестве сигнала ЗАН, указывающего на начало обмена, при этом также запускается генератор 14, который вырабатывает в линию 94 импульсы СХЗ-синхронизации задатчика, поступающие в процессор.

Ответной реакцией процессора на импульсы СХЗ является выдача по линии 95 импульсов СХИ-синхронизации источника, которые являются импульсами частоты записи в блоки памяти информации, поступающей к ним по шине данных (ДШ).

Шина данных поразрядно подключена к входам узлов 36-39 памяти. Таким образом информация, подлежащая записи в блоки памяти, оказывается привязанной к импульсами СХИ, а запись производится параллельно по всём входам блоков, например, байтами.

Единичное положение триггера 15 соответствует режиму записи в узлах 37 и 36 блока 5 памяти, коммутируемых поочередно распределителем 8 через соответствующие элементы И 31 и 32,23 и 24 соответственно, а также режиму считывания для узлов 38 и 39 блока 6 памяти, коммутируемых распределителем 9 через соответствующие элементы И 28 и 31 соответственно. При этом считывание информации происходит по битам за счет сигналов управления, поступающих с выхода распределителя 9 через элементы И 19, с помощью которых разворачивается последовательное обращение к узлам 36-39 блоков 5 и 6 памяти.

Таким образом, в режиме считывания информация из блоков памяти выбирается

последовательно по битам из записанных ранее байтов,

Смена адреса в блоках памяти в режиме считывания происходит с помощью соответствующего счетчика 66 или 67, управляемых через соответствующий элемент ИЛИ 68 или ИЛИ 69 по импульсам в последнем разряде распределителя 19, который появляется в линии 88 для счетчика 66 или в линии 74

0 для счетчика 67.

В режиме записи, например, в узлы 37 или 36 блока 5 памяти импульсы частоты СХИ поступают на элемент 16 задержки и далее через открытый элемент И 10 на эле5 мент 17 задержки и далее на открытые элементы И 32 « 21, при этом на вход записи чтения узла 37 блока 5 памяти импульс СХИ приходит раньше, чем на вход СЕ, так как время срабатывания элемента 17 задержки

0 меньше, чем время срабатывания элемента 16 задержки.

Окончание импульсов СХИ по линиям 86 и 87 происходит одновременно, так как по окончании импульсов СХИ элемент 16

5 задержки отключается закрытием элемента И 12, а время срабатывания элемента 17 задержки равно времени срабатывания элемента И 12 и единичного элемента И 21, при равенстве времени срабатывания единичных

0 элементов И 32 и ИЛИ 14 соответственно.

Сигнал адреса в блоках 5 и 6 памяти в режиме записи производится с помощью соответствующего счетчика 66 и 67 через соответствующий элемент ИЛИ 68 или ИЛИ

5 69 по окончании импульса СХИ в линиях 87 или 74.

Код формата посылки хранится в узлах 58 и 59 постоянной памяти. Код на выходе счетчиков 56 и 57 управляет состоянием вы0 ходов ПЗУ 58 и 59.

ПЗУ 58 и 59 программируются на длительность формата посылки, например, если формат посылки (длительность строки изображения в единицах разложения) ли5 ний/мм// равен 800, то код формата посылки будет кратным этому числу: 800, 1600. 2400 и т.д. Таким образом в ПЗУ задан текущий адрес конца формата посылки. Сравнение текущего адреса блока памяти

0 сравнивается с кодом конца формата посылки на схемах 54 и 55 сравнения, которые информируют сигналом в линиях 83 или.84 об окончании строки изображения. Количество этих окончаний фиксируется счетчиком

5 63 и, если состояние счетчика сравнится с кодом длительности посылки, хранящимся в ПЗУ 60, то схема 64 сравнения выдает сигнал в шине КП об окончании посылки, т.е. об окончании процесса обмена памяти и процессора.

Дешифраторы 61 и 62 контролируют состояние счетчиков 56 и 57. При невозможности дальнейшего участия блоков памяти в приеме информации (в связи с тем, что их объем исчерпан) сигнал с выхода дешифраторов 61 и 62 через соответствующий формирователь 51 и 52 воздействует на распределители 8 и 9 для подключения очередных блоков памяти.

Процесс записи инормации происходит быстрее считывания, поэтому имеет смысл по окончании объема блоков памяти при записи информации освободить общую шину процессора. Освобождение общей шины процессора осуществляется снятием сигнала ЗАН при опрокидывании триггера 46 в единичное состояние. Это происходит в режиме записи тогда, когда распределители 8 или 9 выбирают последний узел памяти (сигнал в линиях 89 или 76) и в момент совпадения кодов формата посылки ПЗУ 58 или 59 (сигнал в линиях 83 или 84).

Такое состояние фиксируется элементами И 48 или 41 через элемент ИЛИ 43.

Возврат триггера 46 в нулевое состояние осуществляется теми же сигналами только в режиме считывания для блоков памяти и фиксируется элементами И 40 или 42 через элемент ИЛИ 44.

Формула изобретения 1. Устройство для сопряжения процессора с памятью, содержащее два распределителя импульсов, группы выходов которых являются соответствующими группами выходов устройства для подключения к группам стробирующих входов первого и второго блоков памяти, два блока формирования адреса, группы выходов которых являются соответствующими группами выходов для подключения к группам адресных входов первого и второго блоков памяти, блок синхронизации обращений, первый выход и синхровход которого являются соответственно выходом и входом устройствам для подключения к синхронизирующим шинам процессора, первая и вторая группы выходов, второй, третий и четвертый, пятый выходы являются соответственно выходами устройства для подключения к группам входов выборки, входам записи-чтения и входам выборки первого и второго блоков памяти, блок дешифрации режима обращений, входы пуска и останова которого являются соответствующими входами пуска и останова устройства, а первый выход является выходом устройства для подключения к шине занятости процессора, и блок настройки, первая и вторая группы информационных входов которого соединены

соответственно с группами выходов первого и второго блоков формирования адреса, первые и вторые тактовые входы и входы разрешения которых подключены соответственно к шестому, седьмому, четвертому и пятому выходам и первой и второй группам выходов блока синхронизации обращений, тактовым и разрешающим входами соединенного соответственно с вторым и третьим

0 выходами блока дешифрации режима обращений, а шестым и седьмым выходами - соответственно с первыми и вторыми тактовыми выходами блока настройки и блока дешифрации режима обращений, первый и

5 второй разрешающие входы и первый и второй информационные входы которого соединены соответственно с первым и вторым выходами блока настройки и группами выходов первого и второго распределителей

0 импульсов, а четвертый выход-с установочными входами первого и второго блоков формирования адреса, причем блок настройки содержит три схемы сравнения, два формирователя импульсов, два элемента И,

5 первые входы которых соединены соответственно с выходами первой и второй схем сравнения и первым и вторым выходами блока настройки, перв,ый счетчик, группой выходов подключенный к первой группе

0 входов третьей схемы сравнения, и элемент ИЛИ, выход которого соединен со счетным входом первого счетчика, причем первые и вторые входы элементов И и первые группы информационных входов первой и второй

5 схем сравнения являются соответственно вторым и первым тактовыми входами и первой и второй группами информационных входов блока настройки, отличающее- с я тем, что, с целью повышения достовер0 ности работы устройства, третий и четвертый выходы блока настройки подключены соответственно к входам первого и второго распределителей импульсов, а в блок настройки введены два счетчика, два дешиф5 ратора, элемент задержки и три узла постоянной памяти, причем в блоке настройки выходы первой и второй схем сравнения соединены соответственно со, счетными входами второго и третьего счет0 чиков, группы выходов которых соединены соответственно с группами входов первого и второго дешифраторов, и через первый и второй узлы постоянной памяти-с вторыми группами входов первой и второй схем срав5 нения, выходы первого и второго дешифраторов подключены соответственно через первый и второй формирователи импульсов к входам сброса второго и третьего счетчиков и третьим и четвертым выходам блока настройки.

2. Устройство по п.1,отличающее с я тем, что блок дешифрации режима обращений содержит пять элементов И, триггеры пуска и режима и два элемента ИЛИ, причем первые входы первого и второго элементов И являются соответственно первым и вторым тактовыми входами блока и соединены соответственно с первыми входами четвертого и третьего элементов И, вторые входы которых являются соответственно вторым и первым информационными входами блока и соединены соответственно с вторыми входами второго и первого элементов И, третьи входы которых являются соответственно вторым и первым разрешающими входами блока и соединены соответственно

с третьими входами четвертого и третьего элементов И, первые и вторые входы первого и второго элементов ИЛИ подключены соответственно к выходам первого и второго, третьего и четвертого элементов ИЛИ, выходы которых соединены соответственно с синхровходом и входом сброса триггера режима, входы сброса и установки триггера пуска являются соответственно входами

сброса и пуска блока, а выход является третьим выходом блока и соединен с первым входом пятого элемента И, второй вход которого соединен с выходом триггера режима, а выход является первым выходом

блока, выход второго элемента ИЛИ является вторым и четвертым выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обменом процессора с памятью | 1988 |

|

SU1667087A1 |

| Устройство для сопряжения процессора с памятью | 1990 |

|

SU1798788A1 |

| Устройство для управления обменом информацией процессора с памятью | 1988 |

|

SU1587525A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для управления обменом процессора с памятью | 1989 |

|

SU1603393A2 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для обмена информацией | 1980 |

|

SU898414A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения систем с быстродействующей памятью большой информационной емкости. Цель изобретения - повышение достс верности работы устройства при передаче изменяемых по формату документов. Цель достигается тем, что в устройство, содержащее два распределителя импульсов, два блока формирования адреса, блок синхронизации обращений, блок дешифрации режима обращений и блок настройки, включающий три схемы сравнения, два элемента И, счетчик, элемент ИЛИ и два формирователя импульсов, введены в блок настройки, три узла постоянной памяти, два счетчика, два дешифратора и элемент задержки. 1 з.п. ф-лы, 6 ил.

0U/

со

CN

со

CN

т гI

| Устройство для сопряжения источника и приемника информации | 1984 |

|

SU1236491A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для управления обменом процессора с памятью | 1988 |

|

SU1667087A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-23—Публикация

1989-09-15—Подача