ОЭ

до

Изобретение относится к вычислительной технике и может быть использовано при создании многопроцессорных вычислительных систем.

Цель изобретения повышение надежности систем за счет сокращения объема оборудования.

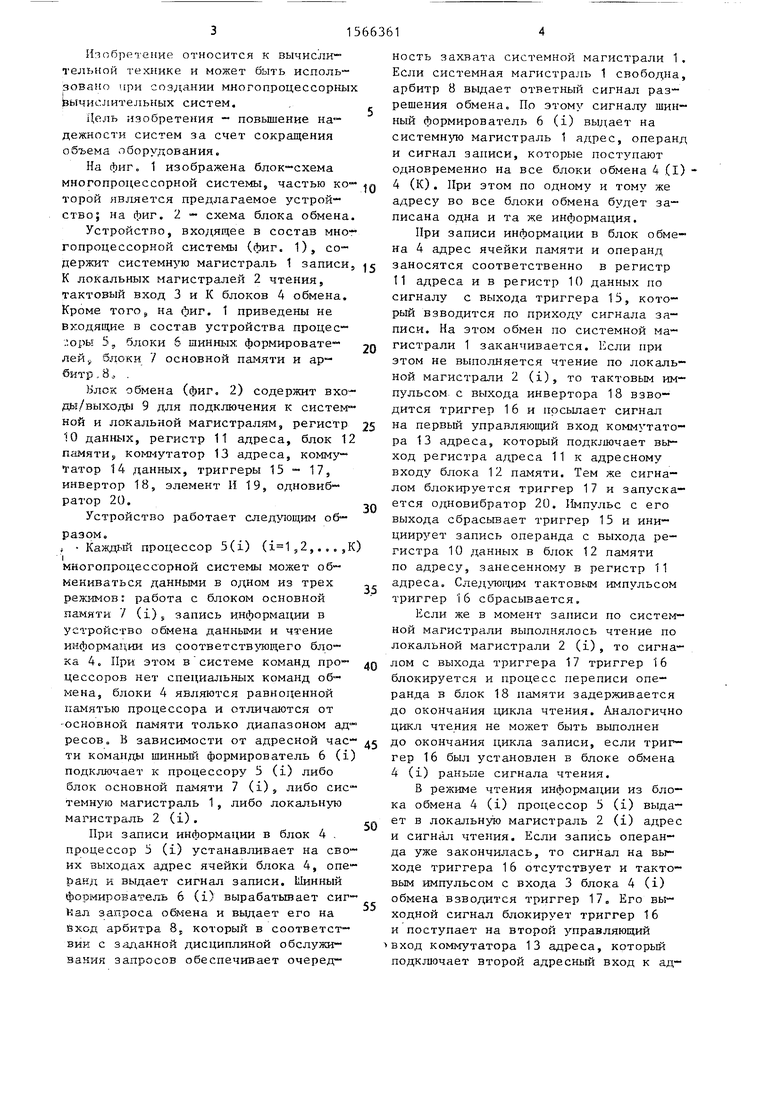

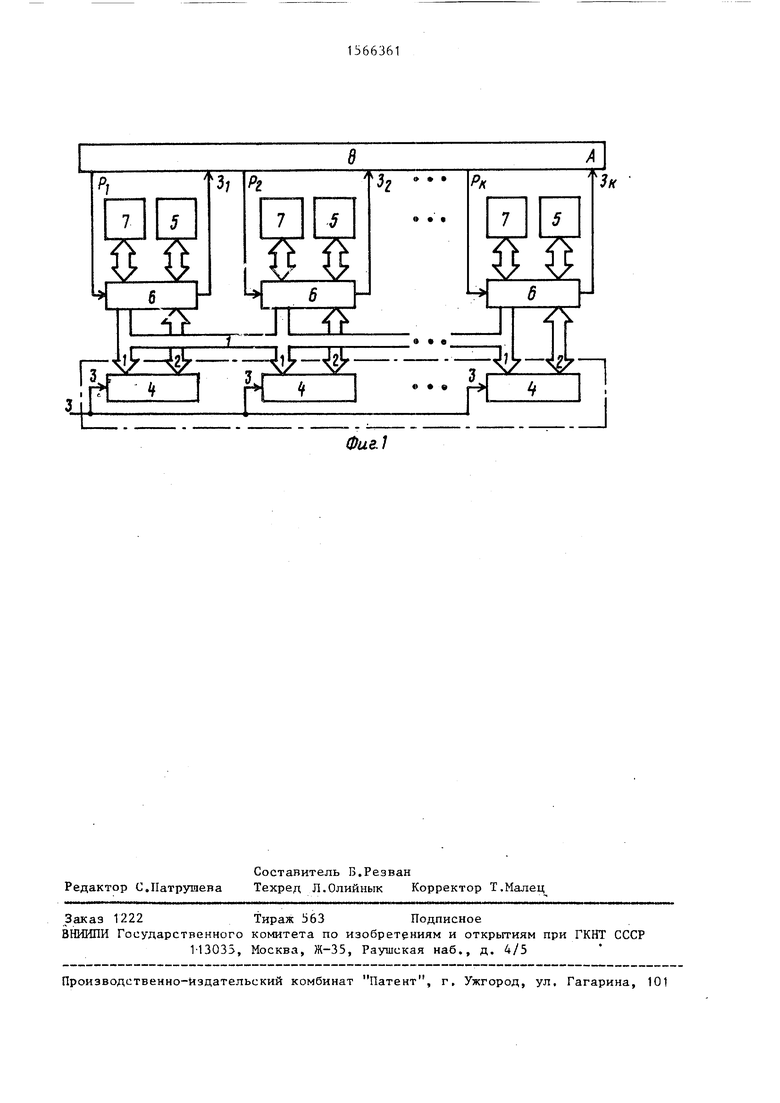

На фиг„ 1 изображена блок-схема многопроцессорной системы, частью ко- торой является предлагаемое устройство; на фиг. 2 - схема блока обмена.

Устройство, входящее в состав многопроцессорной системы (фиг. 1), содержит системную магистраль 1 записи, К локальных магистралей 2 чтения, тактовый вход 3 и К блоков 4 обмена. Кроме того, на фиг. 1 приведены не Входящие в состав устройства процессоры 5, блоки 6 шинных формировате- лейу блоки 7 основной памяти и арбитр , 8, .

Блок обмена (фиг. 2) содержит входы/выходы 9 для подключения к системной и локальной магистралям, регистр 10 данных, регистр 11 адреса, блок 12 памяти,, коммутатор 13 адреса, коммутатор 14 данных, триггеры 15 - 17, инвертор 18, элемент И 19, одновиб- ратор 20.

Устройство работает следующим образом. Каждый процессор 5(1) (,2,...,К

многопроцессорной системы может обмениваться данными в одном из трех режимов: работа с блоком основной памяти 7 (i)s запись информации в устройство обмена данными и чтение информации из соответствующего блока 4. При этом в системе команд про™ цессоров нет специальных команд обмена, блоки 4 являются равноценной памятью процессора и отличаются от основной памяти только диапазоном адресов, В зависимости от адресной час- ти команды шинный формирователь 6 (i) подключает к процессору 5 (i) либо блок основной памяти 7 (i), либо системную магистраль 1, либо локальную магистраль 2 (i).

При записи информации в блок 4 . процессор 5 (i) устанавливает на своих выходах адрес ячейки блока 4, one- &акд и выдает сигнал записи. Шинный формирователь 6 (i) вырабатывает сигнал запроса обмена и выдает его на вход арбитра 8t который в соответствии с заданной дисциплиной обслуживания запросов обеспечивает очеред

о 5

0

5

ность захвата системной магистрали 1. Если системная магистраль 1 свободна, арбитр 8 выдает ответный сигнал разрешения обмена. По этому сигналу шинный формирователь 6 (i) выдает на системную магистраль 1 адрес, операнд и сигнал записи, которые поступают одновременно на все блоки обмена 4 (I) 4 (К). При этом по одному и тому же адресу во все блоки обмена будет записана одна и та же информация.

При записи информации в блок обмена 4 адрес ячейки памяти и операнд заносятся соответственно в регистр 11 адреса и в регистр 10 данных по сигналу с выхода триггера 15, который взводится по приходу сигнала записи. На этом обмен по системной магистрали 1 заканчивается. Если при этом не выполняется чтение по локальной магистрали 2 (i), то тактовым импульсом с выхода инвертора 18 взводится триггер 16 и посылает сигнал на первый управляющий вход коммутатора 1 3 адреса, который подключает выход регистра адреса 11 к адресному входу блока 12 памяти. Тем же сигналом блокируется триггер 17 и запускается одновибратор 20. Импульс с его выхода сбрасывает триггер 15 и инициирует запись операнда с выхода регистра 10 данных в блок 12 памяти по адресу, занесенному в регистр 11 адреса. Следующим тактовым импульсом триггер 16 сбрасывается.

Если же в момент записи по системной магистрали выполнялось чтение по локальной магистрали 2 (i), то сигналом с выхода триггера 17 триггер 16 блокируется и процесс переписи операнда в блок 18 памяти задерживается до окончания цикла чтения. Аналогично цикл чтения не может быть выполнен до окончания цикла записи, если триггер 16 был установлен в блоке обмена 4 (i) раньше сигнала чтения.

В режиме чтения информации из блока обмена 4 (i) процессор 5 (i) выдает в локальную магистраль 2 (i) адрес и сигнал чтения. Если запись операнда уже закончилась, то сигнал на выходе триггера 16 отсутствует и тактовым импульсом с входа 3 блока 4 (i) обмена взводится триггер 17„ Его выходной сигнал блокирует триггер 16 и поступает на второй управляющий вхо,ц коммутатора 13 адреса, который подключает второй адресный вход к ад-

51

ресному входу (шока 12 памяти. Этот же сигнал проходит через элемент И 19 открывает коммутатор 14 данных и поступает на выход разрешения чтения Операнд из выбранной ячейки памяти блока 12 памяти поступает через коммутатор 14 данных на информационный выход блока 4 (i) обмена и далее в локальную магистраль 2 (i) чтения. По- еле приема операнда процессор 5 (i) сбрасывает сигнал чтения. При этом снимается сигнал разрешения чтения и очередным тактовым импульсов сбрасывается триггер 17.

Формула изобретения

Устройство для обмена данными между процессорами, содержащее К блоков обмена, причем первые адресные входы и вход признака чтения i-го (,..., К) блока обмена являются одноименными i-ми входами устройства, выход данных и выход разрешения чтения 1-го блока обмена является одноименными i-ми выходами устройства, отличающееся тем, что, с целью повышения надежности за счет сокращения объема оборудования, второй адресный вход, вход данных, вход при- знака записи всех блоков обмена через системную магистраль соединены между собой и являются одноименными входами устройства для подключения процессоров, тактовые входы всех блоков обмена соединены между собой и подключены к тактовому входу устройства, а каждый блок обмена содержит регистр данных, регистр адреса, блок памяти, коммутатор адреса, коммута- тор данных, три триггера, инвертор, элемент И и одновибратор, выход которого подключен к входу сброса первого

616

триггера и к входу записи блока памя-

i ти, адресный вход которого подключен

к выходу коммутатора адреса, первый и второй информационный входы которо го подключены соответственно к выходу регистра адреса и первому адресному входу блока обмена, второй адресный вход которого подключен к информационному входу регистра адреса, вход записи которого подключен к входу записи регистра данных, к выходу первого триггера и к информационному входу второго триггера, выход которого подключен к входу одновибратора, к входу сброса третьего триггера и к первому управляющему входу коммутатора адреса, второй управляющий вход которого подключен к входу сброса второго триггера, к выходу третьего триггера, и к первому входу элемента И, выход которого подключен к входу управления коммутатора данных и является выходом разрешения чтения блока обмена, вход чтения которого подключен к второму входу элемента Ник информационному входу третьего триггера, тактовый вход которого подключен к тактовому входу блока обмена и к входу инвертора, выход которого подключен к тактовому входу второго триггера, информационней вход блока обмена подключен к информационному входу регистра данных, выход которого подключен к информационному входу блока памяти, выход которого подключен к информационному входу коммутатора данных, выход которого является информационным выходом блока обмена, вход записи которого подключен к тактовому входу первого триггера, информационный вход которого подключен к уровню логической единицы.

U

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

| Устройство для обмена данными между процессорами | 1985 |

|

SU1277127A1 |

| Устройство для обмена данными между процессором и периферийными устройствами | 1987 |

|

SU1501078A1 |

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Вычислительная система | 1989 |

|

SU1633417A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство для сопряжения магистралей | 1990 |

|

SU1737460A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании многопроцессорных вычислительных систем. Целью изобретения является повышение надежности системы за счет сокращения объема оборудования. Поставленная цель достигается тем, что в устройстве, содержащем K блоков обмена, каждый блок обмена содержит регистр данных, регистр адреса, блок памяти, коммутатор адреса, коммутатор данных, три триггера, инвертор, элемент И 19 и одновибратор 20. 2 ил.

Фиг.1

| Валях Е | |||

| Последовательно-парал- -лельные вычисления | |||

| М.: Мир, 1985, с | |||

| Халат для профессиональных целей | 1918 |

|

SU134A1 |

| Способ закалки пил | 1915 |

|

SU140A1 |

| Устройство для обмена данными между процессорами | 1985 |

|

SU1277127A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-13—Подача