Изобретение относится к вычислительной технике и предназначено для использования в информационно-измерительных системах, системах полунатурного моделирования и системах управления различными объектами для сопряжения специализированных вычислительных машин (СВМ) интегрирующего типа с датчиками.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности формирования инкрементных приращений в показательной системе кодирования.

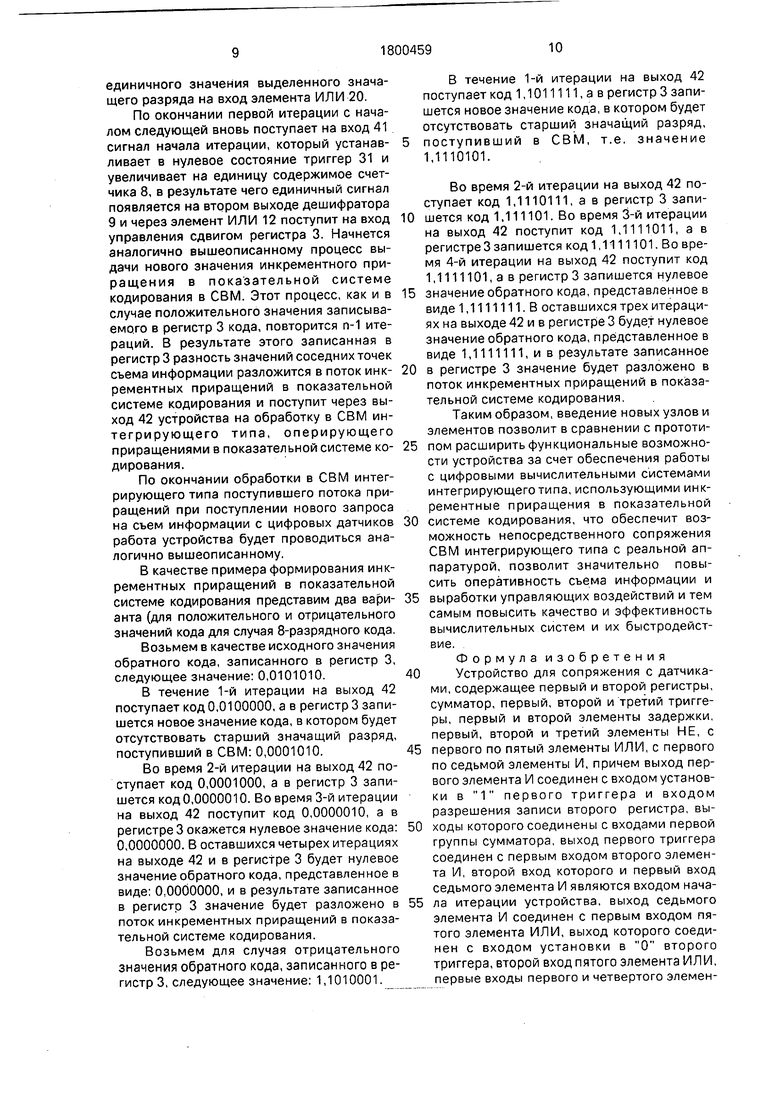

Структурная схема устройства для со- . пряжения с датчиками представлена на чертеже .

В состав устройства для сопряжения с датчиками входят группа элементов И1, сумматор 2, первый регистр 3, второй регистр 4, первый элемент И5, первый триггер 6, второй элемент И 7, счетчик 8, дешифратор 9, первый элемент ИЛИ 10, третий элемент И 11, второй элемент ИЛИ 12, первый элемент задержки 13, первый элемент НЕ 14, второй элемент НЕ 15, восьмой элемент И

16, одиннадцатый элемент И 17, шестой элемент И 18, седьмой элемент И 19, седьмой элемент ИЛИ 20, третий элемент НЕ 21, четвертый элемент ИЛИ 22, пятый элемент ИЛИ 23, четвертый элемент НЕ 24, второй триггер 25, четвертый элемент И 26, девятый элемент И 27, десятый элемент И 28, шестой элемент ИЛИ 29, второй элемент задержки 30, третий триггер 31, пятый элемент И 32, третий элемент ИЛИ 33, двенадцатый элемент И 34.

Цифрой 35 обозначен вход конца итерации устройства, цифрой 36 - тактовый вход устройства, цифрой 37 обозначена группа информационных входов устройства, цифрой 38 обозначен вход разрешения работы устройства, цифрой 39 - вход запроса съема информации устройства, цифрой 40 - вход сброса устройства в исходное состояние, цифрой 41 - вход начала итераций устройства, цифрой 42 - выход устройства.

Выходы группы элементов И 1 соединены с входами второй группы сумматора 2, выходы которого подключены к входам предустановки первого регистра сдвига 3, а входы первой группы сумматора 2 соединеСО

с

оо

О

о

J

СП

о

ны с выходами второго регистра 4, выход первого элемента И 5 соединен с вторыми входами элементов И 1 группы, входом разрешения записи первого регистра 3 и входом установки в нуль первого триггера 6, прямой выход которого соединен с первым входом второго элемента И 7, выход которого подключен к счетному входу счетчика 8, выходы которого соединены с входами дешифратора 9, выход первого элемента ИЛИ

10 соединен с входом установки в нуль первого триггера 6 и входом сброса счетчика 8, выход первого регистра 3 подключен к первому входу третьего элемента И 11, второй вход которого соединен с выходом второго элемента ИЛИ 12 и входом сдвига первого регистра 3, выходы дешифратора 9 соединены с входами второго элемента ИЛИ 12, второй вход первого элемента ИЛИ 10 соединен с выходом первого элемента задержки 13, выход третьего элемента И 11 соединен с входом первого элемента НЕ 14 и первыми входами восьмого элемента И 16, одиннадцатого элемента И 17, шестого элемента И 18, второй вход одиннадцатого элемента И 17 соединен с выходом второго элемента НЕ 15, выход первого элемента НЕ 14-с вторым входом седьмого элемента И 19, выход восьмого элемента И 16 - с вторым входом седьмого элемента ИЛИ 20, выход которого соединен с информационным входом первого регистра 3, выход пятого элемента И 17 подключен к входу третьего элемента HE 21, а выход седьмого элемента И 19 соединен с первым входом пятого элемента ИЛИ 23, выход четвертого элемента НЕ 24 соединен с вторым входом восьмого элемента И 16, выход шестого элемента И 18 - с входом установки в единицу второго триггера 25, вход установки в нуль которого подключен к выходу пятого элемента ИЛИ 23, выход третьего элемента И

11 соединен также с первым входом четвертого элемента И 26, инверсный выход второго триггера 25 - с третьим входом девятого элемента И 27, а прямой выход второго триггера 25 подключен к третьему входу десятого элемента И 28, выход девятого элемента И 27 соединен с входом четвертого элемента НЕ 24 и вторым входом шестого элемента ИЛ И 29, выход четвертого элемента НЕ 24- с вторым входом восьмого элемента И 16, выход десятого элемента И 28 - с первыми входами седьмого элемента ИЛИ 20 и шестого элемента ИЛИ 29, выход которого подключен к входу второго элемента задержки 30, выход которого соединен с входом установки в единицу третьего триггера 31, вход установки в нуль третьего триггера 31 соединен с выходом четвертого элемента ИЛИ

22, инверсный выход третьего триггера 31 подключен к второму входу четвертого эле: мента И 26 и вторым входам девятого и десятого элементов И 27 и И 28, прямой выход третьего триггера 31 подключен к первому входу пятого элемента И 32, выход которого соединен с вторым входом третьего элемента ИЛИ 38, первый вход которого подключен к выходу четвертого элемента И

26, выход третьего элемента НЕ 21 соединен с первым входом десятого элемента И 28, прямой выход второго триггера 25 соединен также с вторым входом пятого элемента И 32, выход одиннадцатого элемента

И 17 соединен также с первым входом девятого элемента И 27, выход старшего разряда дешифратора 9 подключен также к первому входу двенадцатого элемента И 34, выход которого соединен с входом первого элемента задержки 13, второй вход двенадцатого элемента И 34 соединен с входом 35 конца итерации устройства, входы синхронизации первого регистра 3 и второго регистра 4 подключены к тактовому входу 36

устройства, первые входы элементов И 1 группы соединены с группой информационных входов 37 устройства, первый вход первого элемента И 5 соединен с входом 38 разрешения работы устройства, второй

вход первого элемента И 5 - с входом 39 запроса съема информации устройства, входы сброса первого регистра 3 и второго регистра 4, а также первый вход первого элемента ИЛИ 10, второй вход пятого элемента ИЛИ 23 и первый вход четвертого элемента ИЛИ 22 подключены к входу 40 сброса устройства; вторые входы второго элемента И 7, шестого элемента И 18, четвертого элемента ИЛИ 22, первый вход

седьмого элемента И 19 и вход второго элемента НЕ 15 соединены с входом 41 начала итерации устройства, выход третьего элемента ИЛИ 33 соединен с выходом устройства 42,

Перед началом работы устройство устанавливается в исходное состояние. При этом на вход 40 устройства приходит сигнал сброса, который устанавливает в нулевое состояние регистры3,4 и, пройдя через элементы ИЛИ 10, 22 и 23, устанавливает в нуль триггеры 6, 25 и 31 и счетчик 8. Затем подачей на вход 38 сигнала разрешения работы устройства разрешается выполнение операций по съему и преобразованию информации с цифровых датчиков для передачи на обработку в СВМ интегрирующего типа. Осуществляется это следующим образом. По сигналу запроса на съем информации, поступающего из СВМ интегрирующего типа через вход 39 устройства и через открытый элемент И 5 на входы разрешения параллельной записи регистров 3, 4 и вторые входы элементов И 1 группы, производится съем информации, представленной в параллельном обратном коде, с цифрового датчи- ка через информационные входы 37 устройства и запись ее по тактовому импульсу, поступающему на вход 36 устройства, в регистр 4 и через сумматор 2 без изменения (так как регистр 4 установлен перед началом работы в нулевое состояние) в регистр 3. Одновременно сигнал с выхода элемента И 5 поступает на вход установки в единицу триггера 6 и устанавливает его в единичное состояние. Сигнал с прямого выхода триггера 6 является разрешающим для элемента И 7. Сигнал начала итерации, поступающий на вход 41 с СВМ интегрирующего типа для синхронизации момента выдачи информации из устройства с нача- лом очередной итерации, проходит через элемент И 7 на счетный вход счетчика 8, и в счетчик записывается единица. При этом на первом выходе дешифратора 9 появится единичный сигнал, который поступает через элемент ИЛИ 12 на вход управления сдвигом регистра 3, разрешая тем самым сдвиг информации в этом регистре по тактовым импульсам, поступающим на вход 36 устройства. Кроме того, единичный сигнал с выхода элемента ИЛИ 12 открывает элемент И 11. При этом последовательный код первой точки съема информации поступает с выхода регистра 3 через открытый элемент И 11 старшими разрядами вперед/на- чиная со знакового, на входы элементов И 16, 17, 18 и через элемент НЕ 14 - на вход элемента И 19. На другие входы элементов И 18 и 19 поступает в каждой итерации сигнал начала итерации, который выделяет из последовательного кода знаковый разряд и записывает его в триггер 25. А в инверсном виде с выхода элемента НЕ 15 сигнал начала итерации поступит на вход элемента И 17 и обеспечит тем самым на выходе элемента получение последовательного кода без знака, который поступит на вход элемента И 27 и через элемент НЕ 21 на вход элемента И 28. Далее процесс функционирования зависит от записанного в триггер 25 знака последовательного кода. В случае положительного значения знака последовательного кода на третий вход элемента И 27 будет поступать с инверсного выхода триггера 25 единичный сигнал, а так как триггер 31 установлен перед началом работы в нулевое состояние, то и с его инверсного выхода на второй вход элемента И 27 тоже будет поступать единичный сигнал. В результате элемент И 27 будет открыт и

первая же единица в одном из старших разрядов поступающего на вход элемента И 27 кода без знака пройдет через этот элемент И, элемент ИЛ И 29 и, задержавшись на один такт на элементе задержки 30, перебросит в единичное состояние триггер 31, закрыв тем самым элементы И 27, 28 и 26.

В результате прохождения последовательного кода первой точки съема информации старшими разрядами вперед с выхода элемента И 11 через элемент И 26 и элемент ИЛ И 33 на выход 42 устройства для обработки в СВМ интегрирующего типа в качестве приращения первой точки съема информации с цифрового датчика будет выдан последовательный обратный код с единичным значением в одном значащем разряде, т.е. код в показательной системе кодирования. В то же время в регистр 3 запишется новое значение кода, в котором единичное значение значащего разряда, поступившее в СВМ, будет отсутствовать. Исключение данного разряда производится посредством подачи с выхода элемента И 27 через элемент НЕ 24 инверсного значения выделенного значащего разряда на вход элемента И 16.

По окончании первой итерации с началом второй итерации вновь поступает на вход 41 сигнал начала итерации, который устанавливает в нуль триггер 31 и увеличивает на единицу содержимое счетчика 8, в результате чего исчезает единичный сигнал на первом выходе дешифратора 9, появляется единичный сигнал на втором его выходе, и этот сигнал через элемент ИЛИ 12 поступит на вход управления сдвигом регистра 3. Начинается процесс выдачи нового значения инкрементного приращения в показательной системе кодирования в СВМ.

Последовательный код с информационного выхода регистра 3 через открытый эле- мент И 11 вно.вь поступает на вход элементов И 26, 16, 17, 18 и через элемент НЕ 14 - на вход элемента И 19. Повторится процесс, описанный выше. На выход элемента И 26 пройдет последовательный код до очередного старшего значащего разряда, после чего элемент И 26 вновь закроется за счет установки триггера 31 в единичное состояние, а в регистр 3 запишется новое значение кода, отличающееся от предыдущего исключением единицы из очередного значащего разряда, имевшего единичное значение, и поступившее в СВМ в качестве инкрементного приращения в показательной системе кодирования.

Процесс повторится п-1 итераций (п - количество разрядов в коде входной информации поступающей с датчиков), в результате чего записанное в регистр 3 значение первой точки съема информации полностью разложится в поток инкрементных приращений в показательной системе кодирования и поступит через выход 42 устройства на обработку в СВМ интегрирующего типа, оперирующего с приращениями в показательной системе кодирования.

По окончании n-1-й итерации сигнал конца итерации поступающий на вход 35 устройства, пройдет через элемент И 34, открытый в n-1-ой итерации единичным сигналом с n-1-ro выхода дешифратора 9, и, задержавшись на 1 /2 такта на элементе задержки 13, поступит через элемент ИЛИ 10 на входы установки в нуль триггера 6 и счетчика 8 и установит их в нулевое состояние. В результате устройство подготовится к выполнению новой операции по съему информации с цифровых датчиков.

По окончании обработки в СВМ интегрирующего типа приращений первой точки съема информации из СВМ поступает новый запрос на съем информации, который пройдет через вход 39 устройства и через откры- тый элемент И 5 на вход разрешения параллельной записи регистров 3, 4 и на вторые входы элементов И 1 группы, разрешая прохождение через эти элементы с цифрового датчика параллельного обратного кода второй точки съема информации, который поступит на информационные входы регистра 4 и вторые входы сумматора 2, на первые входы которого поступает параллельный код первой точки съема, а так как поступающая информация представлена в обратном коде, то на выходах сумматора 2, обеспечивающего суммирование обратных кодов, получится разность между кодами второй и первой точек съема информации, которая поступит на информационные входы регистра 3 и по тактовому импульсу, поступающему через вход 36 устройства на тактовый вход регистров 3 и 4, запишется в регистр 3, а в регистр 4 одновременно запи- шется значение второй точки съема информации.

Одновременно сигнал с выхода элемента И 5 поступит на вход установки в единицу триггера б и установит его в единичное со- стояние.

В результате при поступлении на вход 41 устройства из СВМ сигнала начала итерации этот сигнал пройдет через элемент И 7, и в счетчик 8 запишется единица, а далее процесс функционирования аналогичен вышеописанному, за исключением не рассмот- ренного еще случая, когда значение полученного на выходах сумматора параллельного обратного кода будет иметь отрицательный знак. В этом случае при поступлении этого кода в последовательном виде с выхода регистра 3 через открытый элемент И 11 по сигналу начала итерации, поступающему на входы элементов И 18 и 19, произойдут выделение из этого кода знакового разряда и запись его в триггер 25. А по инверсному значению сигнала начала итерации, поступающему с выхода элемента НЕ 15 на вход элемента И 17, будет осуществлено получение последовательного кода без знака, который поступит на вход элемента И 27 и через элемент НЕ 21 на вход элемента И 28. А поскольку в триггер 25,фиксирующий знак поступающего кода, будет в этом случае записана единица, на второй вход элемента И 28 будет поступать с прямого выхода этого триггера единичный сигнал, а так как триггер 31 перед началом работы и в начале каждой итерации устанавливается в нулевое состояние, то и с его инверсного выхода на третий вход элемента И 28 тоже будет поступать единичный сигнал, В результате элемент И 28 будет открыт, и первое же нулевое значение в одном из старшим значащих разрядов отрицательного обратного кода без знакового разряда, проинвертировавшись на элементе НЕ 21, пройдет через элемент И 28 в виде единичного сигнала и,пройдя далее через элемент ИЛИ 29 и задержавшись на один такт на элементе задержек 30, перебросит в единичное состояние триггер 31, закрыв тем самым элементы И 27, 28 и 26. В результате прохождение последовательного отрицательного кода старшими разрядами вперед с выхода элемента И 11 через элемент И 26 и элемент ИЛИ 33 будет прекращено, и в остальных разрядах этого кода, поступающего на выход 42 устройства, будет поступать через другой вход элемента ИЛИ 33. С выхода элемента И 32, управляемого знаком с выхода триггера 25 и единичным значением с выхода триггера 31, будут поступать единичные значения, а на выход 42 устройства в результате будет выдан для обработки в СВМ интегрирующего типа в качестве приращения очередной точки съема информации последовательный отрицательный обратный код с нулевым значением в одном значащем разряде, т.е. отрицательный код в показательной системе кодирования. В то же время в регистр 3 запишется новое значение кода, в котором соответствующее значение значащего разряда, поступившее в СВМ, будет отсутствовать. Исключение данного разряда, т.е. устранение в данном случае нуля в этом разряде, производится посредством подачи с выхода элемента И 28

единичного значения выделенного значащего разряда на вход элемента ИЛИ 20.

По окончании первой итерации с началом следующей вновь поступает на вход 41 сигнал начала итерации, который устанавливает в нулевое состояние триггер 31 и увеличивает на единицу содержимое счетчика 8, в результате чего единичный сигнал появляется на втором выходе дешифратора 9 и через элемент ИЛИ 12 поступит на вход управления сдвигом регистра 3. Начнется аналогично вышеописанному процесс выдачи нового значения инкрементного приращения в показательной системе кодирования в СВМ. Этот процесс, как и в случае положительного значения записываемого в регистр 3 кода, повторится п-1 итераций. В результате этого записанная в регистр 3 разность значений соседних точек съема информации разложится в поток инк- рементных приращений в показательной системе кодирования и поступит через выход 42 устройства на обработку в СВМ интегрирующего типа, оперирующего приращениями в показательной системе кодирования.

По окончании обработки в СВМ интегрирующего типа поступившего потока приращений при поступлении нового запроса на съем информации с цифровых датчиков работа устройства будет проводиться аналогично вышеописанному.

В качестве примера формирования инк- рементных приращений в показательной системе кодирования представим два варианта (для положительного и отрицательного значений кода для случая 8-разрядного кода.

Возьмем в качестве исходного значения обратного кода, записанного в регистр 3, следующее значение: 0,0101010.

В течение 1-й итерации на выход 42 поступает код 0,0100000, а в регистр 3 запишется новое значение кода, в котором будет отсутствовать старший значащий разряд, поступивший в СВМ: 0,0001010.

Во время 2-й итерации на выход 42 поступает код 0,0001000, а в регистр 3 запишется код 0,0000010. Во время 3-й итерации на выход 42 поступит код 0,0000010, а в регистре 3 окажется нулевое значение кода: 0,0000000. В оставшихся четырех итерациях на выходе 42 и в pernctpe 3 будет нулевое значение обратного кода, представленное в виде: 0,0000000, и в результате записанное в регистр 3 значение будет разложено в поток инкрементных приращений в показательной системе кодирования.

Возьмем для случая отрицательного значения обратного кода, записанного в регистр 3, следующее значение: 1,1010001.

В течение 1-й итерации на выход 42 поступает код 1,1011111,ав регистр 3 запишется новое значение кода, в котором будет отсутствовать старший значащий разряд, поступивший в СВМ, т.е. значение 1,1110101.

Во время 2-й итерации на выход 42 поступает код 1,1110111, а в регистр 3 запишется код 1,111101. Во время 3-й итерации на выход 42 поступит код 1,1111011, а в регистре 3 запишется код 1,1111101. Во время 4-й итерации на выход 42 поступит код 1,1111101, а в регистр 3 запишется нулевое

значение обратного кода, представленное в виде 1,1111111. В оставшихся трех итерациях на выходе 42 и в регистре 3 будет нулевое значение обратного кода, представленное в виде 1,1111111, и в результате записанное

в регистре 3 значение будет разложено в поток инкрементных приращений в показательной системе кодирования,

Таким образом, введение новых узлов и элементов позволит в сравнении с прототипом расширить функциональные возможности устройства за счет обеспечения работы с цифровыми вычислительными системами интегрирующего типа, использующими инк- рементные приращения в показательной

системе кодирования, что обеспечит возможность непосредственного сопряжения СВМ интегрирующего типа с реальной аппаратурой, позволит значительно повысить оперативность съема информации и

выработки управляющих воздействий и тем самым повысить качество и эффективность вычислительных систем и их быстродействие.

Формула изобретения

Устройство для сопряжения с датчиками, содержащее первый и второй регистры, сумматор, первый, второй и третий триггеры, первый и второй элементы задержки, первый, второй и третий элементы НЕ, с

первого по пятый элементы ИЛИ, с первого по седьмой элементы И, причем выход первого элемента И соединен с входом установки в 1 первого триггера и входом разрешения записи второго регистра, выходы которого соединены с входами первой группы сумматора, выход первого триггера соединен с первым входом второго элемента И, второй вход которого и первый вход седьмого элемента И являются входом начала итерации устройства, выход седьмого элемента И соединен с первым входом пятого элемента ИЛИ, выход которого соединен с входом установки в О второго триггера, второй вход пятого элемента ИЛИ, первые входы первого и четвертого элементов ИЛИ и входы сброса первого и второго регистров являются входом сброса устройства, выход первого элемента ИЛИ соединен с входом установки в О первого триггера, выход первого элемента задержки соединен с вторым входом первого элемента ИЛИ, выход четвертого элемента ИЛИ соединен с входом установки в О третьего триггера, выход первого регистра соединен с первым входом третьего элемента И, вы- ход которого соединен с первым входом четвертого элемента И и входом первого элемента НЕ, выход четвертого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход третьего элемента ИЛИ соединен с выходом пятого элемента И, первый вход первого элемента И является входом разрешения работы устройства, второй вход первого элемента И является входом запроса съема информации устройства, вхо- ды синхронизации регистров являются тактовым входом устройства, отличающее с я тем, что, с целью расширения функциональных возможностей устройства путем обеспечения формирования инкрементных приращений в показательной системе кодирования, в устройство введены счетчик, дешифратор, шестой и седьмой элементы ИЛИ, с восьмого по двенадцатый элементы И, четвертый элемент НЕ, группа элементов И, первые входы которых являются инфор-1 мационными входами устройства, выходы элементов И группы соединены р входами второй группы сумматора и информационными входами второго регистра, выходы сумматора соединены с входами предуста- новки первого регистра, выход первого элемента И соединен с вторыми входами элементов И группы и входом разрешения записи первого регистра, выход второго элемента И соединен со счетным входом счетчика, выходы которого соединены с входами дешифратора, выходы которого соединены с входами второго элемента ИЛИ, выход которого соединен с входом сдвига первого регистра и вторым входом третьего

элемента И, выход которого соединен с первыми входами восьмого, одиннадцатого и шестого элементов И, выход старшего разряда дешифратора соединен с первым входом двенадцатого элемента И, второй вход которого является входом конца итерации устройства, выход двенадцатого элемента И соединен с входом первого элемента задержки, выход первого элемента ИЛ И соединен с входом сброса счетчика, вторые входы шестого элемента И и четвертого элемента ИЛИ и вход второго элемента НЕ являются входом начала итерации устройства, выход второго элемента НЕ соединен с вторым входом одиннадцатого элемента И, выход которого соединен с первым входом девятого элемента И и входом третьего элемента НЕ, выход которого соединен с первым входом десятого элемента И, выход которого соединен с первыми входами шестого и седьмого элементов ИЛИ, выход седьмого элемента ИЛИ соединен с информационным входом первого регистра, выход шестого элемента ИЛИ через второй элемент задержки соединен с входом установки в 1 третьего триггера, прямой выход которого соединен с первым входом пятого элемента И, инверсный выход третьего триггера соединен с вторыми входами четвертого, девятого и десятого элементов И, выход девятого элемента И соединен с вторым входом шестого элемента ИЛИ и входом четвертого элемента НЕ, выход которого соединен с вторым входом восьмого элемента И, выход которого соединен с вторым входом седьмого элемента ИЛИ, выход шестого элемента И соединен с входом установки 1 второго триггера, прямой выход которого соединен с третьим входом десятого элемента И и вторым входом пятого элемента И, инверсный выход второго триггера соединен с третьим входом девятого элемента И, выход третьего элемента ИЛИ является выходом устройства, выход первого элемента НЕ соединен с вторым входом седьмого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения с датчиками | 1985 |

|

SU1290338A1 |

| УСТРОЙСТВО для АППРОКСИМАЦИИ КОДА ПРИРАЩЕНИЯ | 1973 |

|

SU374634A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1985 |

|

SU1252792A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU900300A1 |

| Вычислительный узел цифровой сетки | 1987 |

|

SU1501053A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Устройство для вычисления скользящего спектра | 1981 |

|

SU1027733A1 |

| Устройство для решения систем линейных дифференциальных уравнений | 1988 |

|

SU1525714A2 |

Использование: в информационно-измерительных системах, системах полунатурного моделирования и системах управления объектами для сопряжения специализированных вычислительных машин интегрирующего типа с датчиками. Сущность: устройство содержит группу элементов И, сумматор, два регистра, счетчик, дешифратор, семь элементов ИЛИ, 12 элементов И, четыре элемента НЕ, два элемента задержки. 1 ил.

| Адсорбционная установка | 1980 |

|

SU946617A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения с датчиками | 1985 |

|

SU1290338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-03-07—Публикация

1991-02-04—Подача