Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации.

Целью изобретений является повышение быстродействия преобразователя.

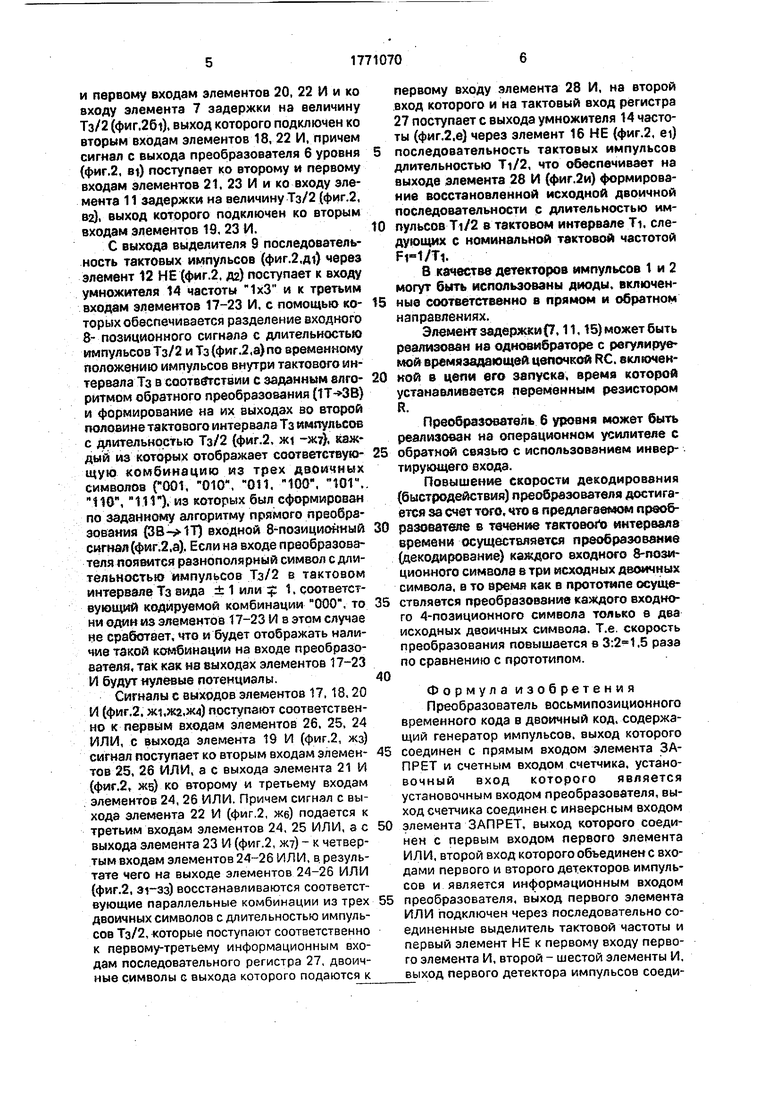

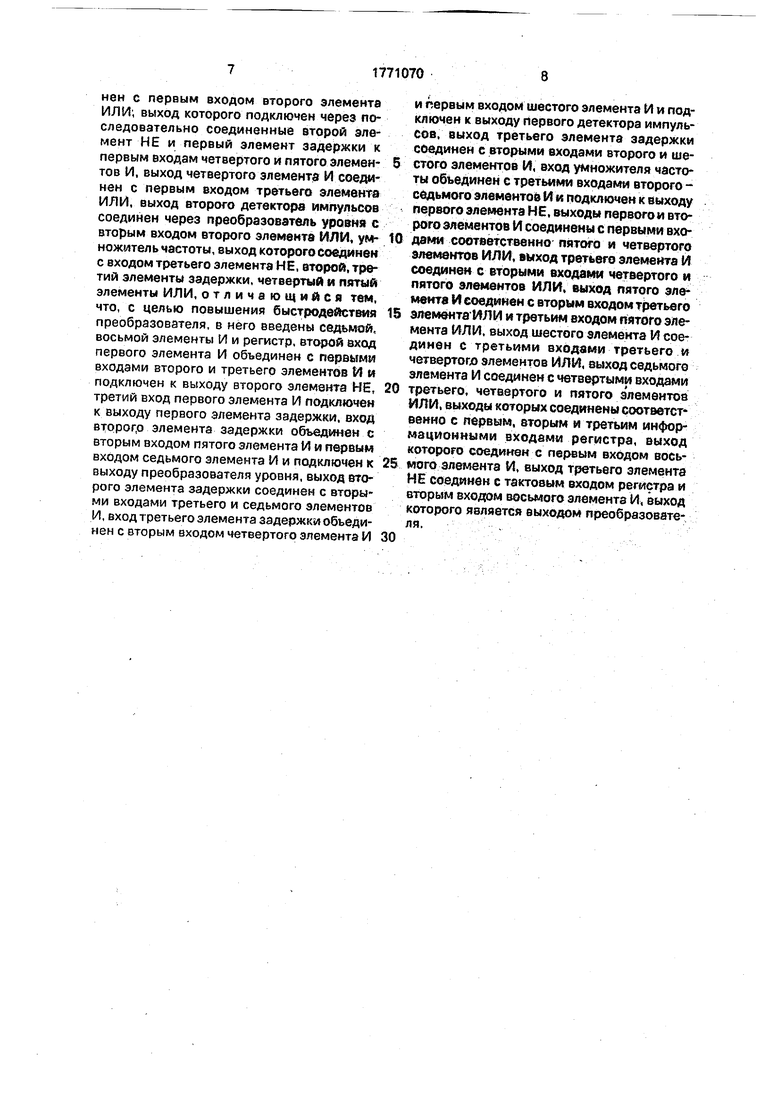

На фиг.1 и 2 представлены соответственно функциональная схема преобразователя и временные диаграммы сигналов, поясняющие его работу.

Преобразователь содержит (фиг.1) пер- вый, второй детектору 1,2 импульсов, генератор 3 импульсов, счетчик А импульсов, первый элемент 5 ИЛИ, преобразователь 6 уровня, третий элемент 1 задержки, элемент 3 запрет, выделитель 9 тактовой часто- ты, второй элемент 10 ИЛИ, второй элемент 11 задержки, первый, второй элементы 12, 13 НЕ, умножитель 14 частоты, первый элемент 15 задержки, третий элемент 16 НЕ, первый - седьмой элементы 17-23 А, третий

-пятый элементы 24 - 26 ИЛИ, последовательный регистр 27 и восьмой элемент 28 И.

Преобразователь работает следующим образом.

После включения электропитания пре- образователя сигнал начального сброса, вы- работанный внешним устройством, устанавливает двоичный счетчик 4 в исходное состояние. При этом с выхода генератора 3 импульсов через последовательно соединенные открытый элемент 8 запрет и элемент 5 ИЛИ на вход выделителя 9 тактовой частоты, реализованного согласно з.с. СССР № 1480140, поступает последовательность тактовых импульсов с длительностью Тз/2 в тактовом интербале Тз, следующих с номинальной тактовой частотой Рз 1/Тз {фиг.д которая обеспечивает запуск и синхронизацию выделителя 9.

, ,,С выхода генератора 3 последовательность тактовых импульсов поступает одновременно на вход счетчика 4, который после окончания установленного счета импульсов переполняется и единичным потенциалом со своего выхода закрывает элемент 8 запрет, что предотвращает прохождение через него импульсов с выхода генератора 3 и

обеспечивает работу выделителя 9 в автономном режиме.

Перед началом приема информационного массива на вход устройства поступает синхросигнал тактовой частоты с длительностью импульсов Тз/2 (меандр), передние фронты импульсов в котором совпадают с началом тактового интервала Тз, что обеспечивает работу выделителя 9 в режиме синхронизации входной последовательностью импульсов, поступающей на вход устройства.

При этом разнополярный 8-позицион- ный сигнал с длительностью импульсов Тз/2 в тактовом интервале , следующих с номинальной тактовой частотой Рз, сформи- ровамный по заданному алгоритму (3В - IT) из исходной двоичной последовательности с длительностью импульсов Ti/2 в тактовом интервале Tt, передние фронты импульсов в котором совпадают с началом или с серединой тактового интервала Тз (фиг.2,а). поступает на входы детекторов 1 и 2, с помощью которых разделяется соответственно на последовательности положительных (фиг.2,6), и отрицательных (фиг.2,в) импульсов, а также поступает через элемент 5 ИЛИ на вход выделителя 9 тактовой частоты и обеспечивает его работу в режиме синхронизации входной последовательностью.

Затем последовательность положительных импульсов с выхода детектора 1 (фиг.2,6) непосредственно, а последовательность отрицательных импульсов с выхода детектора 2 - через преобразователь 6 уровня, обеспечивающий преобразование отрицательных импульсов (фиг.2,в) в положительные (фиг.2,в1), поступает ко входам элемента 10 ИЛИ, сформированный одно- полярный сигнал с выхода которого (фиг.2,г) через элемент 13 НЕ (фиг.2,п) подается к первым входам элементов 17-Т9 И и к входу элемента 15 задержки на величину Тз/2 . (фиг.2,га), выход которого подключен ко второму входу элемента 17 И и к первым входам элементов 20, 21 И. С выхода детектора 1 (фиг.2,6) сигнал поступает ко второму

и первому входам элементов 20, 22 И и ко входу элемента 7 задержки на величину Тз/2 (фиг.2б1), выход которого подключен ко вторым входам элементов 18, 22 И, причем сигнал с выхода преобразователя 6 уровня (фиг.2, BI) поступает ко второму и первому входам элементов 21, 23 И и ко входу элемента 11 задержки на величину Тз/2 (фиг.2, В2), выход которого подключен ко вторым входам элементов 19, 23 И.

С выхода выделителя 9 последовательность тактовых импульсов (фиг.2,д1) через элемент 12 НЕ (фиг.2, дг) поступает к входу умножителя 14 частоты 1x3 и к третьим входам элементов 17-23 И, с помощью ко- торых обеспечивается разделение входного 8- позиционного сигнала с длительностью импульсов Тз/2 и Тз {фиг.2,а) по временному положению импульсов внутри тактового интервала Тз в соответствии с заданным елго- ритмом обратного преобразования () и формирование на их выходах во второй половине тактового интервала Тз импульсов с длительностью Тз/2 {фиг.2, Ж1 , каждый из которых отображает соответствую- щую комбинацию из трех двоичных символов (001, 010, 011, 100, ЮГ. 110, 111). из которых был сформирован по заданному алгоритму прямого преобразования () входной 8-позициойный сигнал (фиг.2 .а). Если на входе преобразователя появится разнополярный символ с длительностью импульсов Тз/2 в тактовом интервале Тз вида ± 1 или +, 1. соответствующий кодируемой комбинации 000, то ни один из элементов 17-23 И в этом случае не сработает, что и будет отображать наличие такой комбинации на входе преобразователя, так как на выходах элементов 17-23 И будут иулевые потенциалы.

Сигналы с выходов элементов 17,18,20 И (фиг.2, Ж1.Ж2.Ж4) поступают соответственно к первым входам элементов 26, 25, 24 ИЛИ, с выхода элемента 19 И (фиг,2, жз) сигнал поступает ко вторым входам элемен- тов 25, 26 ИЛИ, а с выхода элемента 21 И (фиг.2, жд) ко второму и третьему входам элементов 24, 26 ИЛИ. Причем сигнал с выхода элемента 22 И (фиг.2, же) подается к третьим входам элементов 24, 25 ИЛИ, а с выхода элемента 23 И (фиг.2, ж) - к четвертым входам элементов 24-26 ИЛИ, в результате чего на выходе элементов 24-26 ИЛИ (фиг.2, ) восстанавливаются соответствующие параллельные комбинации из трех двоичных символов с длительностью импульсов Тз/2, которые поступают соответственно к первому-третьему информационным входам последовательного регистра 27, двоичные символы с выхода которого подаются к

первому входу элемента 28 И, на второй вход которого и на тактовый вход регистра 27 поступает с выхода умножителя 14 частоты (фиг.2,е) через элемент 16 НЕ (фиг.2, ei) последовательность тактовых импульсов длительностью Ti/2, что обеспечивает на выходе элемента 28 И (фиг.2и) формирование восстановленной исходной двоичной последовательности с длительностью импульсов Тi/2 в тактовом интервале TL следующих с номинальной тактовой частотой F1-1/T1.

В качестве детекторов импульсов 1 и 2 могут быть использованы диоды, включенные соответственно в прямом и обратном направлениях.

Элемент задержки (7,11,15) может быть реализован на одновибраторе с регулируемой времязадающей цепочкой RC. включенной в цели его запуска, время которой устанавливается переменным резистором R.

Преобразователь 6 уровня может быть реализован на операционном усилителе с обратной связью с использованием инвер- тирующего входа.

Повышение скорости декодирования (быстродействия) преобразователя достигается за счет того, что в предлагаемом преобразователе в течение тактового интервала времени осуществляется преобразование (декодирование) каждого входного 8-пози- ционного символа в три исходных двоичных символа, в то время как в прототипе осуществляется преобразование каждого входного 4-позиционного символа только в два исходных двоичных символа. Т.е. скорость преобразования повышается в ,5 раза по сравнению с прототипом.

Формула изобретения Преобразователь восьми позиционного временного кода в двоичный код. содержащий генератор импульсов, выход которого соединен с прямым входом элемента ЗАПРЕТ и счетным входом счетчика, установочный вход которого является установочным входом преобразователя, выход счетчика соединен с инверсным входом элемента ЗАПРЕТ, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого объединен с входами первого и второго детекторов импульсов и является информационным входом преобразователя, выход первого элемента ИЛИ подключен через последовательно соединенные выделитель тактовой частоты и первый элемент НЕ к первому входу первого элемента И, второй - шестой элементы И, выход первого детектора импульсов соединем с первым входом второго элементе ИЛИ; выход которого подключен через последовательно соединенные второй эле мент НЕ и первый элемент задержки к первым входам четвертого и пятого элементов И, выход четвертого элемента И соединен с первым входом третьего элемента ИЛИ, выход второго детектора импульсов соединен через преобразователь уровня с вторым входом второго элементе ИЛИ, умножитель частоты, выход которого соединен с входом третьего элемента НЕ, второй, третий элементы задержки, четвертый и пятый элементы ИЛИ, отличающийся тем, что, с мелью повышения быстродействия преобразователя, в него введены седьмой, восьмой элементы И и регистр, второй вход первого элемента И объединен с первыми входами второго и третьего элементов И и подключен к выходу второго элемента НЕ, третий вход первого элемента И подключен к выходу первого элемента задержки, вход второго элемента задержки объединен с вторым входом пятого элемента И и первым входом седьмого элемента И и подключен к выходу преобразователя уровня, выход второго элемента задержки соединен с вторыми входами третьего и седьмого элементов И, вход третьего элемента задержки объединен с вторым входом четвертого элемента И

и первым входом шестого элемента И и подключен к выходу первого детектора импульсов, выход третьего элемента задержки соединен с вторыми входами второго и шестого элементов И, вход умножителя частоты объединен с третьими входами второго - седьмого элементов И и подключен к выходу первого элемента НЕ, выходы первого и второго элементов И соединены с первыми входами соответственно- пятого и четвертого элементов ИЛИ, выход третьего элемента И соединен с вторыми входами четвертого и пятого элементов ИЛИ, выход пятого элемента И соединен с вторым входом третьего

элемента ИЛИ и третьим входом пятого элемента ИЛИ, выход шестого элемента И соединен с третьими входами третьего и четвертого элементов ИЛИ, выход седьмого элемента И соединен с четвертыми входами

третьего, четвертого и пятого элементов ИЛИ, выходы которых соединены соответственно с первым, вторым и третьим информационными входами регистра, выход которого соединен с первым входом восьмого элемента И, выход третьего элемента НЕ соединен с тактовым входом регистра и вторым входом восьмого элемента И, выход которого является выходом преобразователя.

tJ

4J-U-S O4J- J J- J4J-«J4J4J

Редактор

fi

ft t J4

г$

Составитель М.Никуленков Техред М.МоргенталКорректор М.Петрова

3 ма vo «а о «Г пс в «Г «j 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретной информации | 1990 |

|

SU1807579A1 |

| Устройство для уплотнения каналов связи | 1990 |

|

SU1809544A1 |

| Преобразователь четырехпозиционного временного кода в двоичный код | 1990 |

|

SU1797162A1 |

| Преобразователь двоичного кода в восьмипозиционный временной код | 1990 |

|

SU1730725A1 |

| Устройство для двухкратного уплотнения каналов связи | 1991 |

|

SU1775871A1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1646068A1 |

| Преобразователь двоичного кода в четырехпозиционный код | 1988 |

|

SU1594703A1 |

| Преобразователь двоичного кода в четырех-позиционный временной код | 1990 |

|

SU1757104A1 |

| Шифратор кодов | 1986 |

|

SU1319282A1 |

| Устройство для приема сигналов относительной фазовой телеграфии | 1983 |

|

SU1138954A1 |

Изобретение относится к электросвязи « может использоваться в системах передачи дискретной информации. Преобразователь осуществляет преобразование (декодирование) каждого входного восьми- поэиционного символа в три исходных двоичных символа, что повышает быстродейст

| Устройство для выделения тактовых сигналов из импульсных последовательностей с переменными параметрами | 1987 |

|

SU1480140A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Преобразователь четырехпозиционного временного кода в двоичный код | 1988 |

|

SU1599994A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-10-23—Публикация

1990-04-23—Подача