Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах передачи дискретной информации различного назначения.

Цель изобретения - расширение функциональных возможностей устройства лу- тем устранения флюктуации удельной скорости передачи в результате изменения алгоритмов кодирования-декодирования.

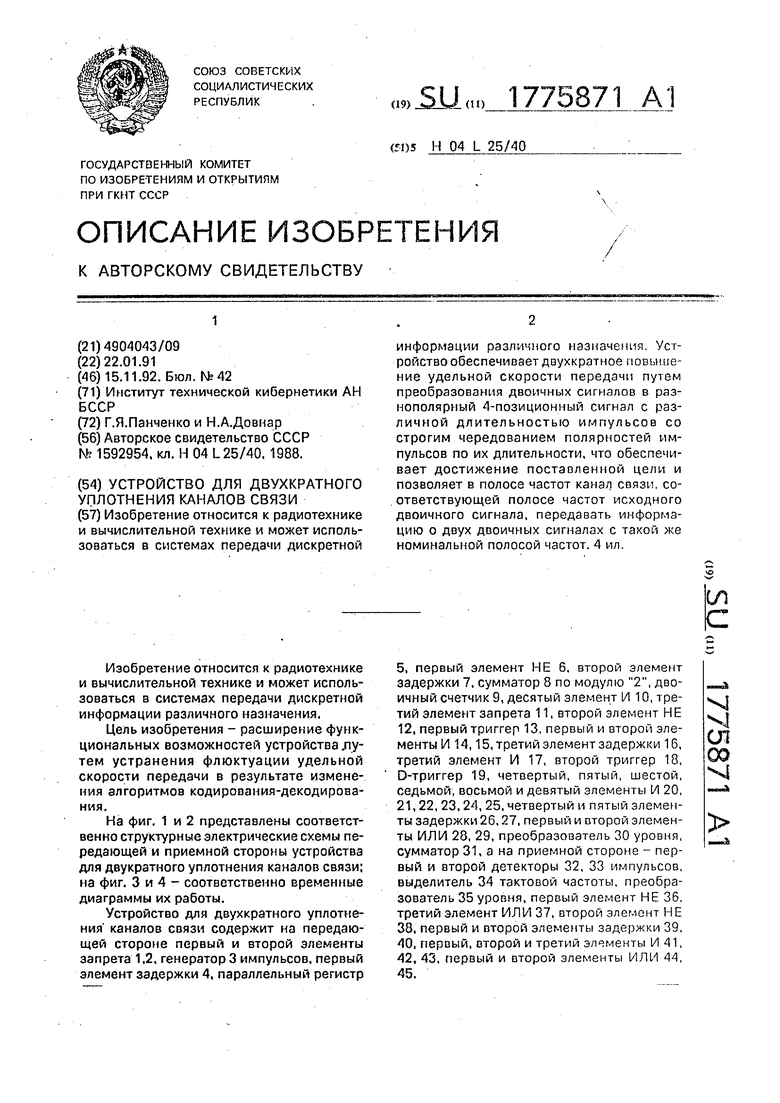

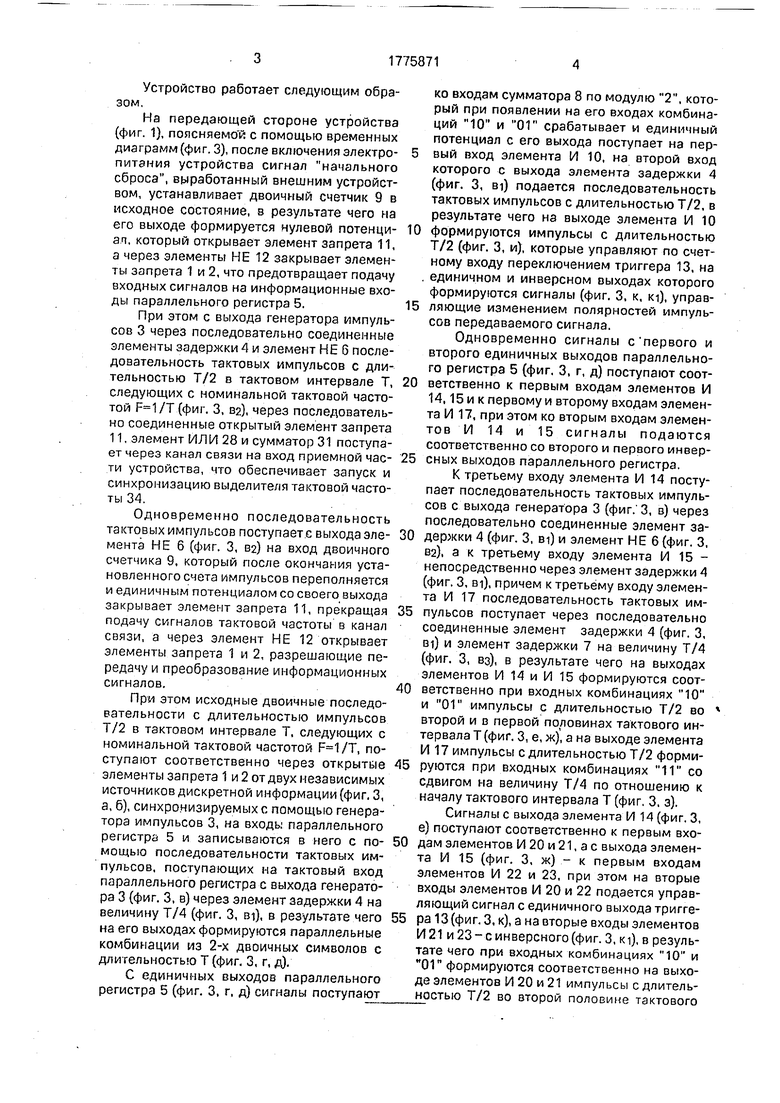

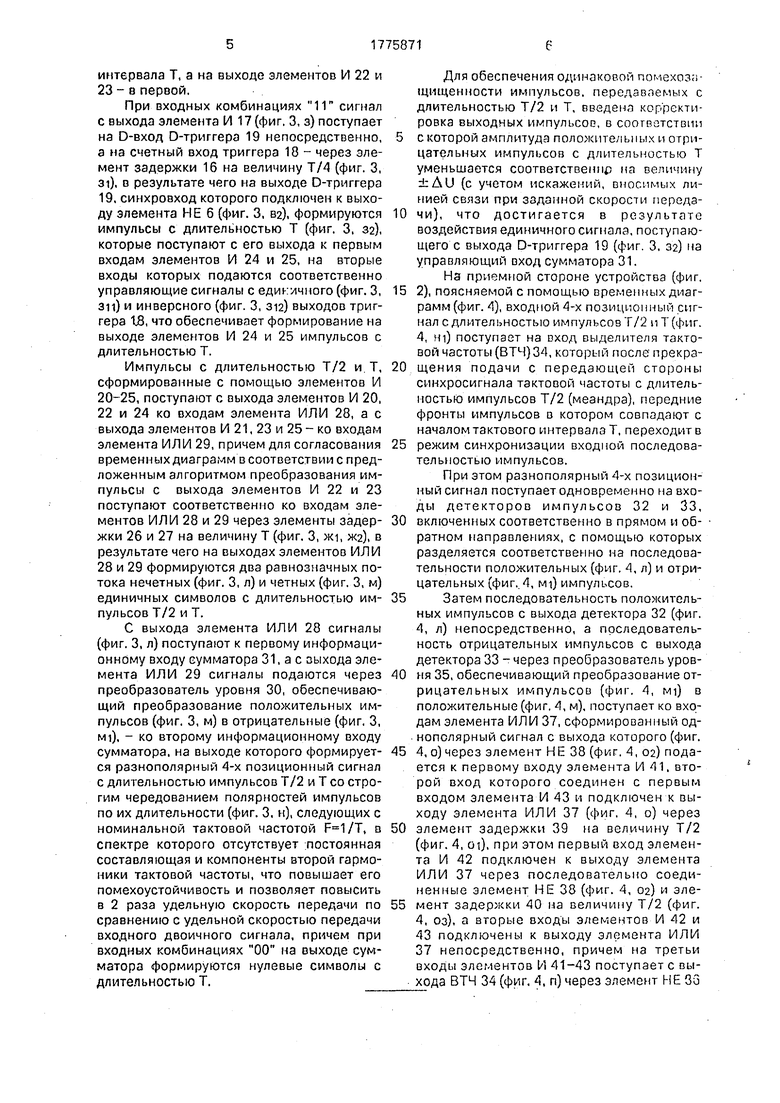

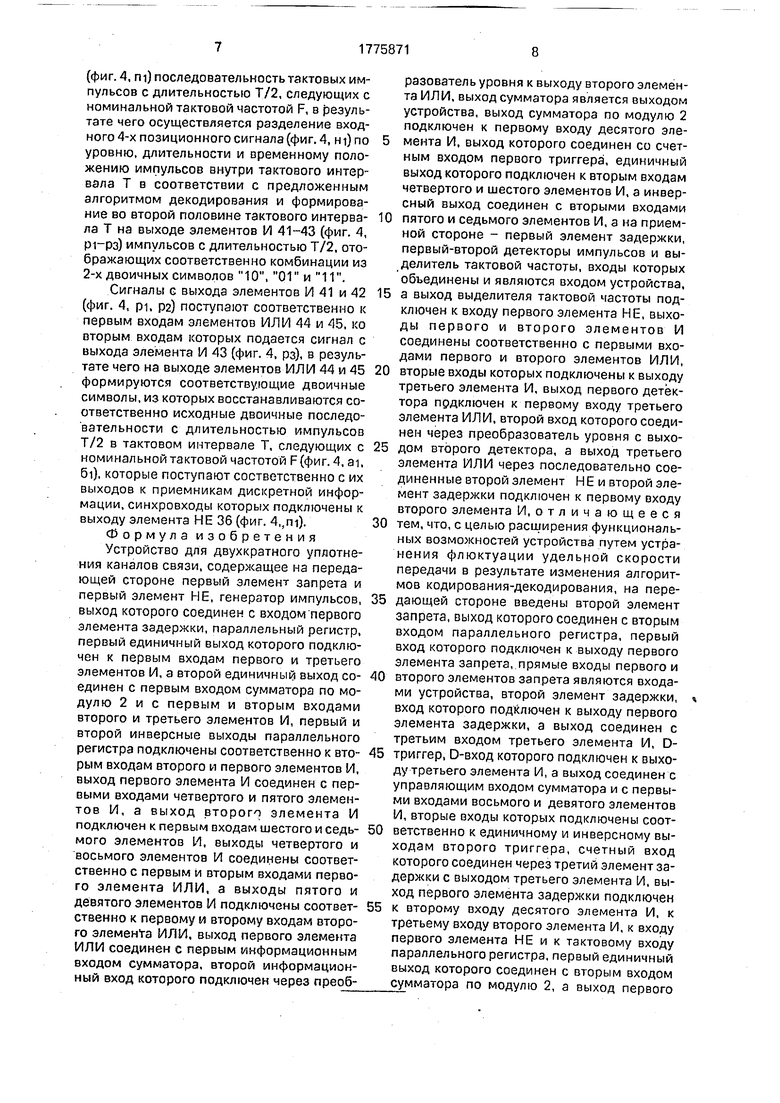

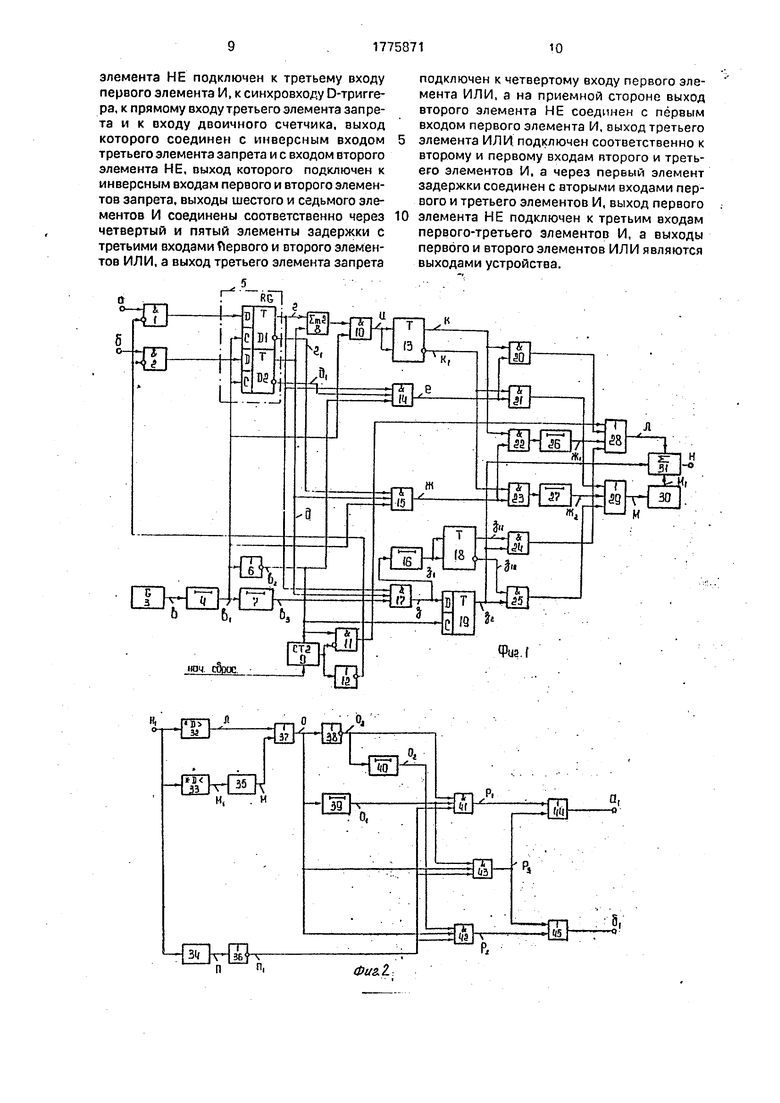

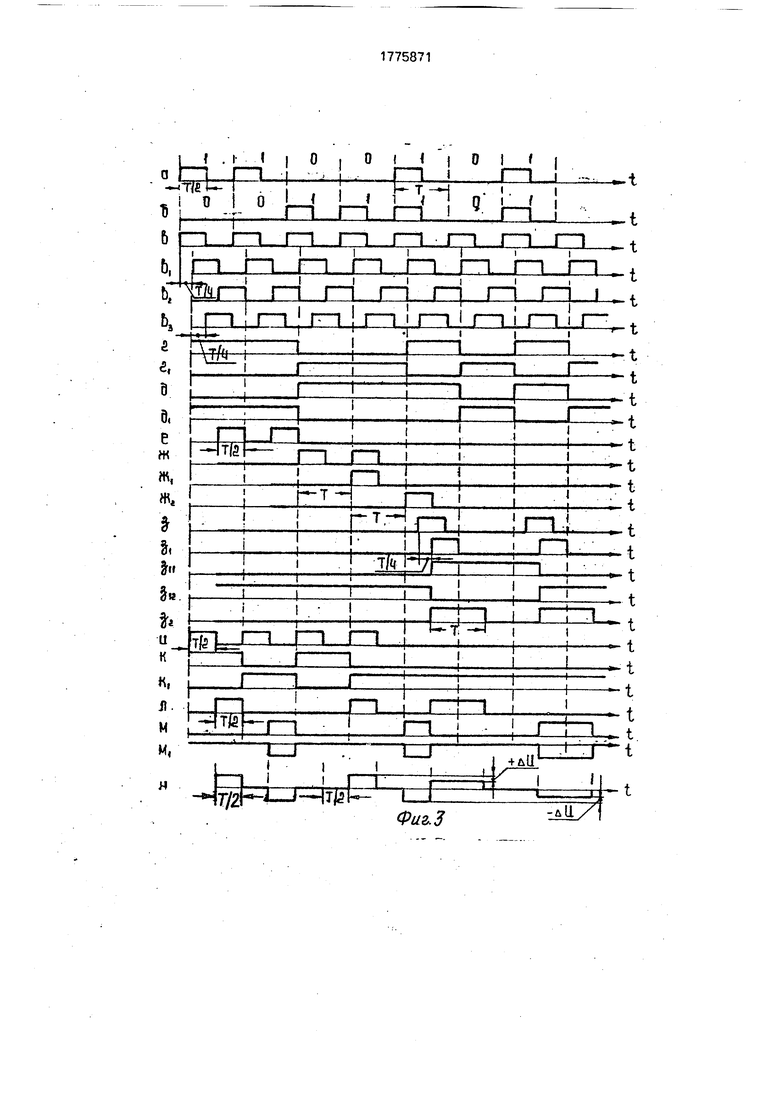

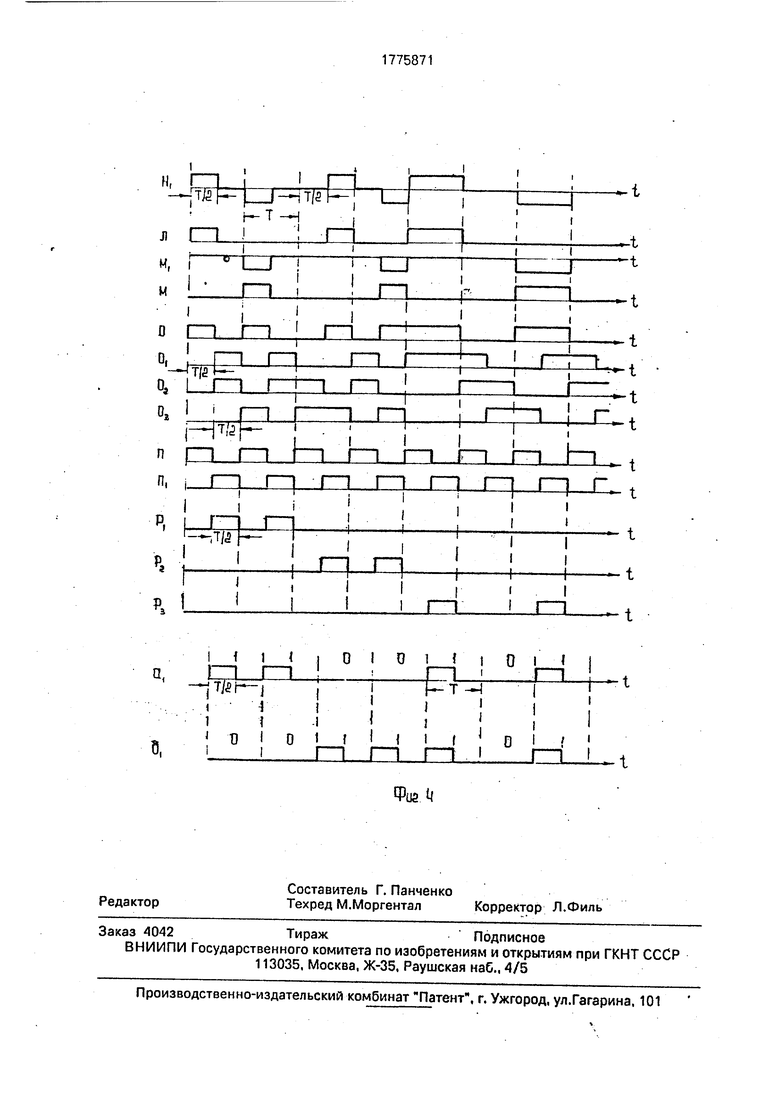

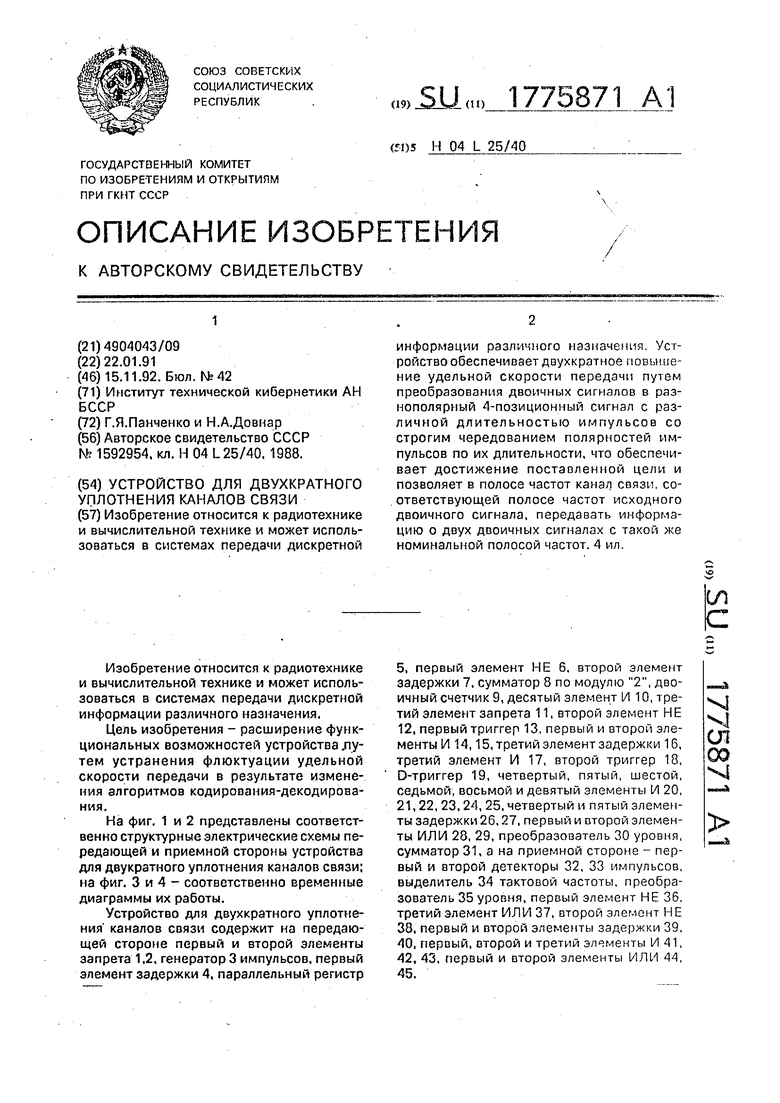

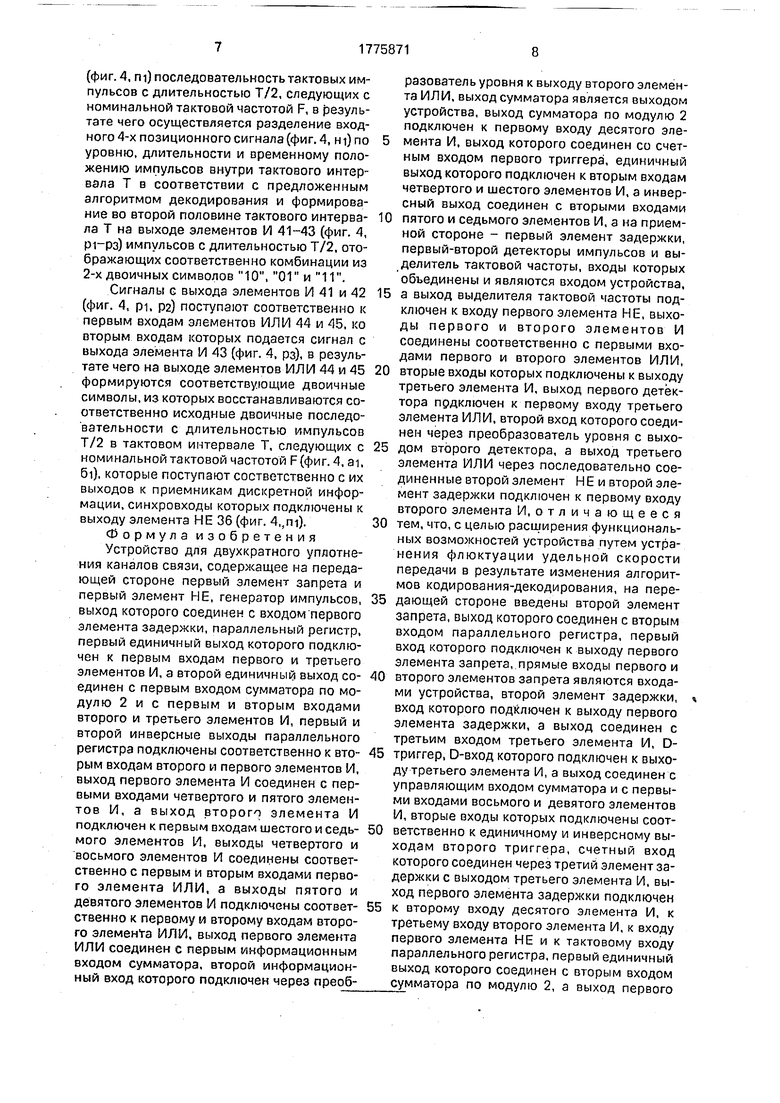

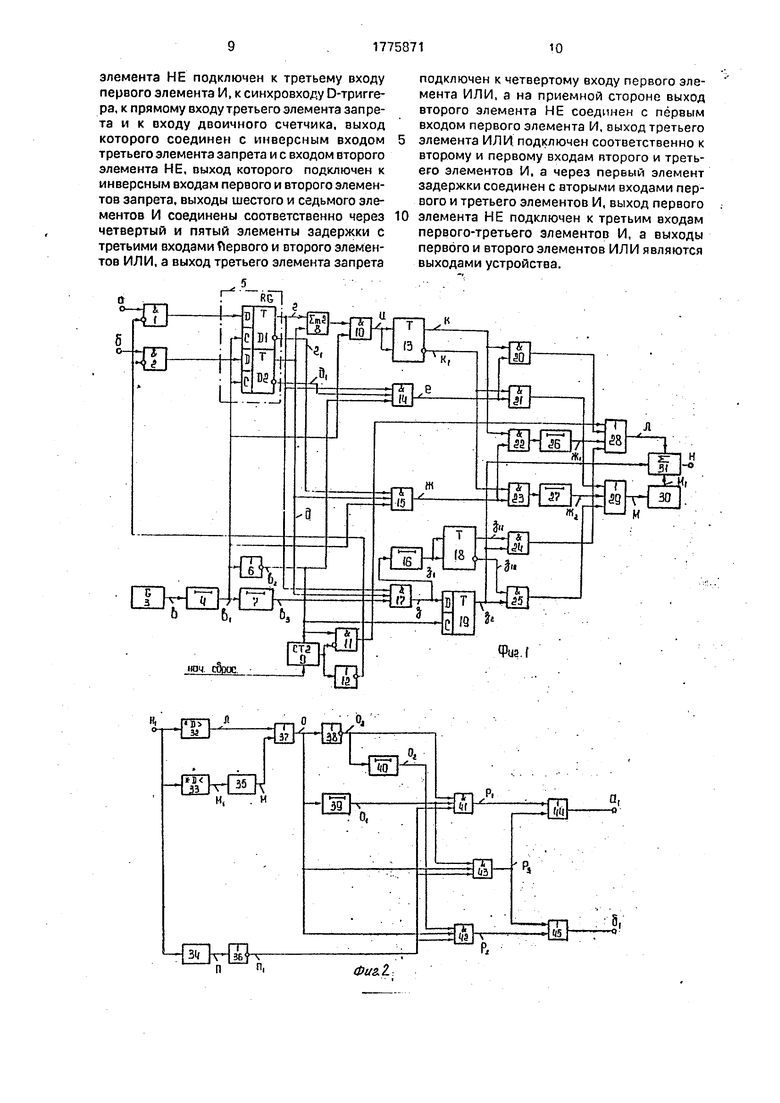

На фиг. 1 и 2 представлены соответственно структурные электрические схемы передающей и приемной стороны устройства для двукратного уплотнения каналов связи; на фиг. 3 и 4 - соответственно временные диаграммы их работы.

Устройство для двухкратного уплотнения каналов связи содержит на передающей стороне первый и второй элементы запрета 1,2. генератор 3 импульсов, первый элемент задержки 4, параллельный регистр

5, первый элемент НЕ 6, второй элемент задержки 7. сумматор 8 по модулю 2, двоичный счетчик 9, десятый элемент И 10, третий элемент запрета 11, второй элемент НЕ 12, первый триггер 13, первый и второй элементы И 14,15, третий элемент задержки 16, третий элемент И 17, второй триггер 18, D-триггер 19, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И 20, 21,22, 23,24, 25, четвертый и пятый элементы задержки 26,27, первый и пторой элементы ИЛИ 28, 29, преобразователь 30 уровня, сумматор 31, а на приемной стороне - первый и второй детекторы 32, 33 импульсов, выделитель 34 тактовой частоты, преобразователь 35 уровня, первый элемент НЕ 36. третий элемент ИЛИ 37, второй элемент НЕ 38, первый и второй элементы задержки 39, 40, первый, второй и третий элементы 1/141, 42, 43, первый и второй элементы ИЛИ 44, 45.

XI VI СЛ

V4

-л

Устройство работает следующим образом,

На передающей стороне устройства (фиг. 1), поясняемой с помощью временных диаграмм (фиг. 3), после включения электропитания устройства сигнал начального сброса, выработанный внешним устройством, устанавливает двоичный счетчик 9 в исходное состояние, в результате чего на его выходе формируется нулевой потенци- ат, который открывает элемент запрета 11, а через элементы НЕ 12 закрывает элементы запрета 1 и 2, что предотвращает подачу входных сигналов на информационные входы параллельного регистра 5.

При этом с выхода генератора импульсов 3 через последовательно соединенные элементы задержки 4 и элемент НЕ б последовательность тактовых импульсов с длительностью Т/2 в тактовом интервале Т, следующих с номинальной тактовой частотой (фиг. 3, в.), через последовательно соединенные открытый элемент запрета 11, элемент ИЛИ 28 и сумматор 31 поступает через канал связи на вход приемной части устройства, что обеспечивает запуск и синхронизацию выделителя тактовой частоты 34.

Одновременно последовательность тактовых импульсов поступаете выхода элемента НЕ 6 (фиг. 3, В2) на вход двоичного счетчика 9, который после окончания установленного счета импульсов переполняется и единичным потенциалом со своего выхода закрывает элемент запрета 11, прекращая подачу сигналов тактовой частоты в канал связи, а через элемент НЕ 12 открывает элементы запрета 1 и 2, разрешающие передачу и преобразование информационных сигналов.

При этом исходные двоичные последовательности с длительностью импульсов Т/2 в тактовом интервале Т, следующих с номинальной тактовой частотой , поступают соответственно через открытые элементы запрета 1 и 2 от двух независимых источников дискретной информации (фиг. 3, а, б), синхронизируемых с помощью генератора импульсов 3, на входы параллельного регистра 5 и записываются в него с помощью последовательности тактовых импульсов, поступающих на тактовый вход параллельного регистра с выхода генератора 3 (фиг. 3, в) через элемент задержки 4 на величину Т/4 (фиг. 3, BI), в результате чего на его выходах формируются параллельные комбинации из 2-х двоичных символов с длительностью Т (фиг. 3, г, д).

С единичных выходов параллельного регистра 5 (фиг. 3, г, д) сигналы поступают

ко входам сумматора 8 по модулю 2, который при появлении на его входах комбинаций 10 и 01 срабатывает и единичный потенциал с его выхода поступает на первый вход элемента И 10, на второй вход которого с выхода элемента задержки 4 (фиг. 3, BI) подается последовательность тактовых импульсов с длительностью Т/2, в результате чего на выходе элемента И 10

0 формируются импульсы с длительностью Т/2 (фиг. 3, и), которые управляют по счетному входу переключением триггера 13, на , единичном и инверсном выходах которого формируются сигналы (фиг. 3. к, KI), управ5 ляющие изменением полярностей импульсов передаваемого сигнала.

Одновременно сигналы с первого и второго единичных выходов параллельного регистра 5 (фиг. 3, г, д) поступают соот0 ветственно к первым входам элементов И 14,15 и к первому и второму входам элемента И 17, при этом ко вторым входам элементов И 14 и 15 сигналы подаются соответственно со второго и первого инвер5 сных выходов параллельного регистра.

К третьему входу элемента И 14 поступает последовательность тактовых импульсов с выхода генератора 3 (фиг. 3, в) через последовательно соединенные элемент за0 держки 4 (фиг. 3, BI) и элемент НЕ 6 (фиг. 3, В2), а к третьему входу элемента И 15 - непосредственно через элемент задержки 4 (фиг. 3, BI), причем к третьему входу элемента И 17 последовательность тактовых им5 пульсов поступает через последовательно соединенные элемент задержки 4 (фиг. 3, BI) и элемент задержки 7 на величину Т/4 (фиг. 3, вз), в результате чего на выходах элементов И 14 и И 15 формируются соот0 ветственно при входных комбинациях 10 и 01 импульсы с длительностью Т/2 во второй и в первой половинах тактового интервала Т (фиг. 3, е, ж), а на выходе элемента И 17 импульсы с длительностью Т/2 форми5 руются при входных комбинациях 11 со сдвигом на величину Т/4 по отношению к началу тактового интервала Т (фиг, 3. з).

Сигналы с выхода элемента И 14 (фиг. 3, е) поступают соответственно к первым вхо0 дам элементов И 20 и 21, а с выхода элемента И 15 (фиг. 3, ж) - к первым входам элементов И 22 и 23, при этом на вторые входы элементов И 20 и 22 подается управляющий сигнал с единичного выхода тригге5 ра 13(фиг. 3,к), а на вторые входы элементов И 21 и 23-с инверсного (фиг. 3, KI), в результате чего при входных комбинациях 10 и 01 формируются соответственно на выходе элементов И 20 и 21 импульсы с длительностью Т/2 во второй половине тактового

интервала Т, а на выходе элементов И 22 и 23 - в первой.

При входных комбинациях 11 сигнал с выхода элемента И 17 (фиг. 3, з) поступает на D-вход D-триггера 19 непосредственно, а на счетный вход триггера 18 - через элемент задержки 16 на величину Т/4 (фиг. 3, 3i), в результате чего на выходе D-триггера 19, синхровход которого подключен к выходу элемента НЕ 6 (фиг. 3, ва), формируются импульсы с длительностью Т (фиг. 3, 32), которые поступают с его выхода к первым входам элементов И 24 и 25, на вторые входы которых подаются соответственно управляющие сигналы с едикичного (фиг. 3, зц) и инверсного (фиг. 3, 312) выходов триггера 1Д что обеспечивает формирование на выходе элементов И 24 и 25 импульсов с длительностью Т.

Импульсы с длительностью Т/2 и Т, сформированные с помощью элементов И 20-25, поступают с выхода элементов И 20, 22 и 24 ко входам элемента ИЛИ 28, а с выхода элементов И 21, 23 и 25- ко входам элемента ИЛИ 29, причем для согласования временных диаграмм в соответствии с предложенным алгоритмом преобразования импульсы с выхода элементов И 22 и 23 поступают соответственно ко входам элементов ИЛИ 28 и 29 через элементы задер- жки 26 и 27 на величину Т (фиг. 3, Ж1, Ж2), в результате чего на выходах элементов ИЛИ 28 и 29 формируются два равнозначных потока нечетных (фиг. 3, л) и четных (фиг. 3, м) единичных символов с длительностью им- пульсов Т/2 и Т.

С выхода элемента ИЛИ 28 сигналы (фиг. 3, л) поступают к первому информационному входу сумматора 31, а с зыхода элемента ИЛИ 29 сигналы подаются через преобразователь уровня 30, обеспечивающий преобразование положительных импульсов (фиг. 3, м) в отрицательные (фиг. 3, MI), - ко второму информационному входу сумматора, на выходе которого формирует- ся разнополярный 4-х позиционный сигнал с длительностью импульсов Т/2 и Т со строгим чередованием полярностей импульсов по их длительности (фиг. 3, н), следующих с номинальной тактовой частотой , в спектре которого отсутствует постоянная составляющая и компоненты второй гармоники тактовой частоты, что повышает его помехоустойчивость и позволяет повысить в 2 раза удельную скорость передачи по сравнению с удельной скоростью передачи входного двоичного сигнала, причем при входных комбинациях 00 на выходе сумматора формируются нулевые символы с длительностью Т.

Для обеспечения одинаковой помехозащищенности импульсов, передаваемых с длительностью Т/2 и Т, введена корректировка выходных импульсов, в соответствии с которой амплитуда положительных и отрицательных импульсов с длительностью Т уменьшается соответственна на величину ±AU (с учетом искажений, сносимых линией связи при заданной скорости передачи), что достигается в результате воздействия единичного сигнала, поступающего с выхода D-триггера 19 (фиг. 3, 32) на управляющий вход сумматора 31.

На приемной стороне устройства (фиг. 2), поясняемой с помощью временных диаграмм (фиг. 4), входной 4-х позиционный сигнал с длительностью импульсов Т/2 и Т (фиг. 4, ч0 поступает на вход выделителя тактовой частоты (ВТЧ) 34, который после прекращения подачи с передающей стороны синхросигнала тактовой частоты с длительностью импульсов Т/2 (меандра), передние фронты импульсов в котором совпадают с началом тактового интервала Т, переходите режим синхронизации входной последовательностью импульсов.

При этом разнополярный 4-х позиционный сигнал поступает одновременно на входы детекторов импульсов 32 и 33, включенных соответственно в прямом и обратном направлениях, с помощью которых разделяется соответственно на последовательности положительных (фиг. 4, л) и отрицательных (фиг, 4, MI) импульсов.

Затем последовательность положительных импульсов с выхода детектора 32 (фиг. 4, л) непосредственно, а последовательность отрицательных импульсов с выхода детектора 33 - через преобразователь уровня 35, обеспечивающий преобразование от- рицательных импульсов (фиг. 4, MI) в положительные (фиг. 4, м), поступает ко входам элемента ИЛИ 37, сформированный од- нополярный сигнал с выхода которого (фиг. 4, о) через элемент НЕ 38 (фиг. 4, 02) подается к первому входу элемента И 41. второй вход которого соединен с первым входом элемента И 43 и подключен к выходу элемента ИЛИ 37 (фиг. 4, о) через элемент задержки 39 на величину Т/2 (фиг. 4, оt). при этом первый вход элемента И 42 подключен к выходу элемента ИЛИ 37 через последовательно соединенные элемент НЕ 38 (фиг. 4, 02) и элемент задержки 40 на величину Т/2 (фиг. 4, оз), а вторые входы элементов И 42 и 43 подключены к выходу элемента ИЛИ 37 непосредственно, причем на третьи входы элементов И 41-43 поступает с выхода ВТЧ 34 (фиг. А, п) через элемент НЕ Go

(фиг. 4, m) последовательность тактовых импульсов с длительностью Т/2, следующих с номинальной тактовой частотой F, в результате чего осуществляется разделение входного 4-х позиционного сигнала (фиг. 4, н i) по уровню, длительности и временному положению импульсов внутри тактового интервала Т в соответствии с предложенным алгоритмом декодирования и формирование во второй половине тактового интерва- ла Т на выходе элементов И 41-43 (фиг. 4, ) импульсов с длительностью Т/2, отображающих соответственно комбинации из 2-х двоичных символов 10, 01 и 11.

Сигналы с выхода элементов И 41 и 42 (фиг. 4, pi, P2) поступают соответственно к первым входам элементов ИЛИ 44 м 45, ко вторым входам которых подается сигнал с выхода элемента И 43 (фиг. 4, рз), в результате чего на выходе элементов ИЛИ 44 и 45 формируются соответствующие двоичные символы, из которых восстанавливаются соответственно исходные двоичные последовательности с длительностью импульсов Т/2 в тактовом интервале Т, следующих с номинальной тактовой частотой Р(фиг. 4, ai, 61), которые поступают соответственно с их выходов к приемникам дискретной информации, синхровходы которых подключены к выходу элемента НЕ 36 (фиг. 4,,щ).

Формула изобретения Устройство для двухкратного уплотнения каналов связи, содержащее на передающей стороне первый элемент запрета и первый элемент НЕ, генератор импульсов, выход которого соединен с входом первого элемента задержки, параллельный регистр, первый единичный выход которого подключен к первым входам первого и третьего элементов И, а второй единичный выход со- единен с первым входом сумматора по модулю 2 и с первым и вторым входами второго и третьего элементов И, первый и второй инверсные выходы параллельного регистра подключены соответственно к вто- рым входам второго и первого элементов И, выход первого элемента И соединен с первыми входами четвертого и пятого элементов И, а выход второго элемента И подключен к первым сходам шестого и седь- мого элементов И, выходы четвертого и восьмого элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, а выходы пятого и девятого элементов И подключены соответ- ственно к первому и второму входам второго элемента ИЛИ, выход первого элемента ИЛИ соединен с первым информационным входом сумматора, второй информационный вход которого подключен через преобразователь уровня к выходу второго элемента ИЛИ, выход сумматора является выходом устройства, выход сумматора по модулю 2 подключен к первому входу десятого элемента И, выход которого соединен со счетным входом первого триггера, единичный выход которого подключен к вторым входам четвертого и шестого элементов И, а инверсный выход соединен с вторыми входами пятого и седьмого элементов И, а на приемной стороне - первый элемент задержки, первый-второй детекторы импульсов и выделитель тактовой частоты, входы которых объединены и являются входом устройства, а выход выделителя тактовой частоты подключен к входу первого элемента НЕ, выходы первого и второго элементов И соединены соответственно с первыми входами первого и второго элементов ИЛИ, вторые входы которых подключены к выходу третьего элемента И, выход первого детектора подключен к первому входу третьего элемента ИЛИ, второй вход которого соединен через преобразователь уровня с выходом второго детектора, а выход третьего элемента ИЛИ через последовательно соединенные второй элемент НЕ и второй элемент задержки подключен к первому входу второго элемента И, отличающееся тем, что, с целью расширения функциональных возможностей устройства путем устранения флюктуации удельной скорости передачи в результате изменения алгоритмов кодирования-декодирования, на передающей стороне введены второй элемент запрета, выход которого соединен с вторым входом параллельного регистра, первый вход которого подключен к выходу первого элемента запрета, прямые входы первого и второго элементов запрета являются входами устройства, второй элемент задержки, вход которого подключен к выходу первого элемента задержки, а выход соединен с третьим входом третьего элемента И, D- триггер, D-вход которого подключен к выходу третьего элемента И, а выход соединен с управляющим входом сумматора и с первыми входами восьмого и девятого элементов И, вторые входы которых подключены соответственно к единичному и инверсному выходам второго триггера, счетный вход которого соединен через третий элемент задержки с выходом третьего элемента И, выход первого элемента задержки подключен к второму оходу десятого элемента И, к третьему входу второго элемента И, к входу первого элемента НЕ и к тактовому входу параллельного регистра, первый единичный выход которого соединен с вторым входом сумматора по модулю 2, а выход первого

элемента НЕ подключен к третьему входу первого элемента И, к синхровходу D-тригге- ра, к прямому входу третьего элемента запрета и к входу двоичного счетчика, выход которого соединен с инверсным входом третьего элемента запрета и с входом второго элемента НЕ, выход которого подключен к инверсным входам первого и второго элементов запрета, выходы шестого и седьмого элементов И соединены соответственно через четвертый и пятый элементы задержки с третьими входами Первого и второго элементов ИЛИ, а выход третьего элемента запрета

0

подключен к четвертому входу первого элемента ИЛИ, а на приемной стороне выход второго элемента НЕ соединен с первым входом первого элемента И, выход третьего элемента ИЛИ подключен соответственно к второму и первому входам второго и третьего элементов И, а через первый элемент задержки соединен с вторыми входами первого и третьего элементов И, выход первого элемента НЕ подключен к третьим входам первого-третьего элементов И, а выходы первого и второго элементов ИЛИ являются выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1646068A1 |

| Устройство для уплотнения каналов связи | 1990 |

|

SU1809544A1 |

| Устройство для передачи и приема дискретной информации | 1990 |

|

SU1807579A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Преобразователь четырехпозиционного временного кода в двоичный код | 1990 |

|

SU1797162A1 |

| Устройство для передачи и приема дискретной информации | 1988 |

|

SU1529459A1 |

| Устройство для передачи и приема дискретной информации | 1987 |

|

SU1443178A1 |

| Преобразователь восьмипозиционного временного кода в двоичный код | 1990 |

|

SU1771070A1 |

| ЦИФРОВОЙ АВТОМАТИЧЕСКИЙ КОРРЕКТОР СИГНАЛОВ | 1992 |

|

RU2106062C1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1184105A1 |

Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах передачи дискретной информации различного назначения Устройство обеспечивает двухкратное повышение удельной скорости передачи путем преобразования двоичных сигналов в раз- иополярный 4-позиционный сигнал с различной длительностью импульсов со строгим чередованием полярностей импульсов по их длительности, что обеспечивает достижение поставленной цели и позволяет в полосе частот канал связи, соответствующей полосе частот исходного двоичного сигнала, передавать информацию о двух двоичных сигналах с такой же номинальной полосой частот. 4 ил.

Фи&2.

f . I- I I 0

0 I 0 I f I1 I

| Авторское свидетельство СССР № 1592954 | |||

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1992-11-15—Публикация

1991-01-22—Подача