Фиг

Изобретение относится к радиотехнике и вычислительной технике и может использоваться в системах передачи дискретной информации различного назначения.

Известно устройство для преобразова- ния двоичного кода в троичный, содержащее 8 элементов И, 5 элементов НЕ и 4 элемента ИЛИ, которое обеспечивает преобразование комбинаций из трех двоичных символов (1;0) в комбинации из двух троич- ных символов (+1;0;-1) по заданному алгоритму (ЗВ- 2Т), в результате чего достигается повышение удельной скорости передачи в 1,5 раза.

Недостатком известного устройства яв- ляется то, что сформированный трричный сигнал является несбалансированным и в его спектре содержится постоянная составляющая, снижающая его помехоустойчивость. Кроме того, удельная скорость передачи троичного сигнала повышается незначительно (К 1,5).

Наиболее близким к предлагаемому является преобразователь двоичного кода в четырех позиционный временной код, со- держащий генератор импульсов, 4 элемента задержки, делитель частоты, последовательный и параллельный регистры, элемент НЕ, 9 элементов И, 3 элемента ИЛИ, триггер, преобразователь уровня и сумматор, который обеспечивает преобразование комбинаций из двух двоичных символов (1;0) в один троичный символ (+1;0;-1), в результате чего достигается повышение удельной скорости передачи в 2 раза. При этом четырехпозиционный сигнал, сформированный в соответствии с предлагаемым алгоритмом преобразования, является полностью сбалансированным.

Недостатком известного преобразова- теля является то, что он обеспечивает сравнительно небольшое повышение удельной скорости передачи (К 2).

Цель изобретения - повышение удельной скорости передачи преобразователя.

Для этого в преобразователь двоичного кода в восьмипозиционный временной код, содержащий последовательный регистр, информационный вход которого является входом преобразователя, выходы последо- вательного регистра соединены с одноименными информационными входами параллельного регистра, генератор импульсов, выход которого соединен через первый элемент задержки с тактовым входом по- следовательного регистра и входом делителя частоты, выход которого соединен через последовательно соединенные первый элемент НЕ и второй элемент задержки с тактовым входом параллельного регистра и

первыми входами первого, второго, третьего элементов И, четвертый-девятый элементы И, выходы четвертого и шестого элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым входом сумматора, выходы пятого и седьмого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен через преобразователь уровня с вторым входом сумматора, выход первого элемента И соединен через третий элемент задержки с пер- выми входами восьмого и девятого элементов И, триггер, прямой и инверсный выходы которого соединены с вторыми входами соответственно восьмого и девятого элементов И, выходы которых соединены с третьими входами соответственно первого и второго элементов ИЛИ, выход сумматора является выходом преобразователя, третий элемент ИЛИ и четвертый элемент задержки, введены дешифратор, второй элемент НЕ, пятый элемент задержки и четвертый элемент ИЛИ, первый и второй входы которого подключены к выходам соответственно шестого и седьмого элементов И. В ыход четвертого элемента ИЛИ соединен с третьим входом сумматора, вход и выход четвертого элемента задержки соединены соответственно с выходом девятого элемента И и четвертым входом первого элемента ИЛИ. Вход и выход пятого элемента задержки соединены соответственно с выходом восьмого элемента И и четвертым входом второго элемента ИЛИ. Выходы второго и третьего элементов И соединены с пятыми входами соответственно первого и второго элементов ИЛИ. Вход триггера подключен к выходу первого элемента И. Вход второго элемента НЕ объединен с первым входом третьего элемента ИЛИ и подключен к выходу второго элемента задержки. Выход второго элемента НЕ соединен с первыми входами четвертого, пятого элементов И и вторым входом третьего элемента ИЛИ, выход которого соединен с управляющими входами дешифратора и первыми входами шестого и седьмого элементов И. Выходы параллельного регистра соединены с одноименными информационными входами дешифратора, первый и третий-восьмой выходы которого соединены с вторыми входами соответственно первого-седьмого элементов И.

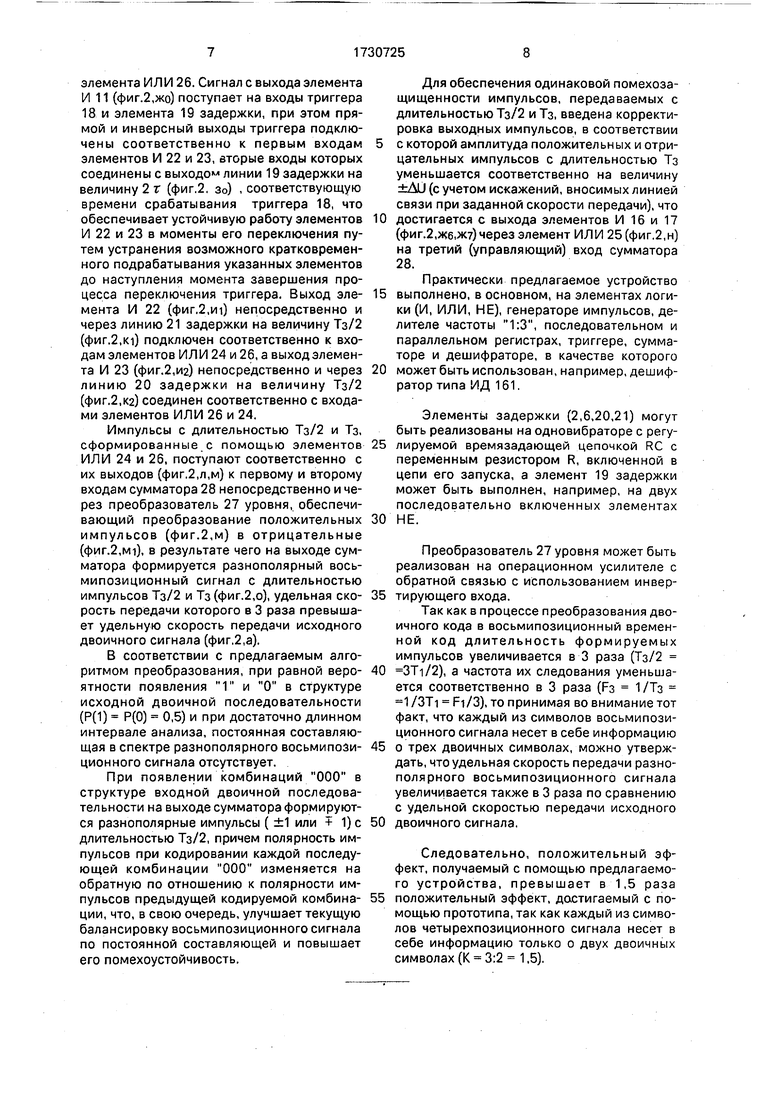

На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - временные диаграммы работы устройства.

Устройство (фиг.1) содержит генератор 1 импульсов, элемент 2 задержки, делитель 3 частоты, элемент НЕ 4, последовательный

регистр 5, элемент 6 задержки, параллельный регистр 7, элемент НЕ 8, элемент ИЛИ 9, дешифратор 10, элементы И 11-17, триггер 18, элементы 19-21 задержки, элементы И 22 и 23, элементы ИЛИ 24-26, преобразователь 27 уровня и сумматор 28.

Преобразователь двоичного кода в восьмипозиционный временной код работает следующим образом.

Исходная двоичная последовательность с длительностью импульсов Ti/2 в тактовом интервале Тч, следующих с номинальной тактовой частотой Fi 1/Ti, поступает от источника дискретной информации (фиг.2,а), синхронизируемого с помощью генератора 1 импульсов на информационный вход последовательного регистра 5 и записывается в него с помощью последовательности тактовых импульсов, поступающих с выхода генератора импульсов (фиг.2,б) через элемент 2 задержки на величину Ti/4 (фиг.2,6).

С одноименных выходов последовательного регистра 5 двоичные символы по- ступают на одноименные входы параллельного регистра 7 и записываются в него с помощью последовательности тактовых импульсов с длительностью Тз/2 в тактовом интервале Тз ЗТт, следующих с номинальной тактовой частотой Рз 1/Тз 1/3Ti Fi/3, формируемых с помощью делителя 3 частоты 1:3, вход которого соединен с выходом элемента 2 задержки (фиг.2,6), которые с выхода делителя (фиг.2,в) через последовательно соединенные элемент НЕ 4 (фиг.2,в1) и элемент 6 задержки на величину Тз/3 Ti (фиг.2,В2) поступают на тактовый вход параллельного регистра 7, в результате чего исходная двоичная последовательность разделяется на группы из трех двоичных символов, каждая из которых преобразовывается далее в соответствующую параллельную комбинацию из трех двоичных символов с длительностью- Тз (фиг. 2, п - гз).

С выходов параллельного регистра 7 (фиг.2,п-гз) сигналы поступают соответственно на одноименные входы дешифратора 10 (АО, А1, А2), на управляющие входы которого (ЕО, Е1) подается единичный потенциал с выхода элемента ИЛИ 9 (фиг.2,Д1), входы которого через элемент НЕ 8 (фиг.2,д) и непосредственно подключены к выходу элемента 6 задержки (фиг.2,в2), в результате чего на соответствующем выходе дешифратора (FO-F7) формируется в анализируемый момент времени единичный импульс с длительностьюТз(фиг.2,ео-е), соответствующий структуре комбинации из трех двоичных символов (фиг.2,п-гз).

Работа дешифратора мощью таблицы. ЕО Е1 А2 А1 АО F7 F6 F5

поясняется с по1

1 1 1 1 1

0 1 1 О X

5

1 1 1 1 1 1 1 1 X

о

1 1

1 О О 1

1 О О

о о

1 1

1 О О 0 1 000 X X X О X X X О

1 о о о о о о о

о 1

о о о о о о о о

Примечание. Значком X обозначено произвольное состояние, соответствующее уровню логического О или логической 1.

Как следует из таблицы, дешифратор ра0 ботает только при наличии единичных потенциалов на обоих управляющих входах (ЕО и Е1) (в противном случае на выходах FO-F7 дешифратора формируются уровни логического О). При этом, если, например,

5 структура входной комбинации (АО-А2) соответствует значению 010, то единичный импульс формируется на выходе F2 дешифратора, при комбинации 101 - на выходе F5 и т.д., причем при комбинации 001 еди0 ничный импульс формируется на выходе F1, однако согласно предлагаемому алгоритму преобразования этот импульс передается далее в канал связи нулевым символом с длительностью Тз, вследствие чего второй

5 выход дешифратора (фиг.1,в1) в схеме преобразователя не используется (остается изолированным).

Сигналы с выходов дешифратора (фиг.2,ео-е2-е) поступают соответственно

0 на первые входы элементов И 11-17, при этом вторые входы элементов И 11-13 подключены к выходу элемента 6 задержки (фиг.2,в2), вторые входы элементов И 14 и 15 соединены с выходом элемента НЕ 8 (фиг.

5 2,д), а вторые входы элементов И 16 и 17 подключены к выходу элемента ИЛИ 9 (фиг.2,д1), в результате чего на выходе элементов И 11-13 формируются импульсы с длительностью Тз/2 в первой половине так0 тового интервалаТз(фиг.2,жо,Ж2,жз), причем на выходе элементов И 14 и 15 импульсы с длительностью Тз/2 формируются во второй половине тактового интервала Тз (фиг.2,ж4,ж5), а на выходе элементов И 16 и

5 17 формируются импульсы с длительностью Тз (фиг.2,жб,ж).

С выходов элементов И 12, 14 и 16 (фиг.2,ж2,Ж4,Жб) сигналы поступают к входам элемента ИЛИ 24, а с выходов элементов И 13, 15 и 17 (фиг.2,жз,Ж5,ж)- к входам

элемента ИЛИ 26. Сигнал с выхода элемента И 11 (фиг.2,жо) поступает на входы триггера 18 и элемента 19 задержки, при этом прямой и инверсный выходы триггера подключены соответственно к первым входам элементов И 22 и 23, вторые входы которых соединены с выходом линии 19 задержки на величину 2 г (фиг.2. зо) .соответствующую времени срабатывания триггера 18, что обеспечивает устойчивую работу элементов И 22 и 23 в моменты его переключения путем устранения возможного кратковременного подрабатывания указанных элементов до наступления момента завершения процесса переключения триггера. Выход эле- мента И 22 (фиг.2,HI) непосредственно и через линию 21 задержки на величину Тз/2 (фиг.2,KI) подключен соответственно к входам элементов ИЛИ 24 и 26, а выход элемента И 23 (фиг.2,иа) непосредственно и через линию 20 задержки на величину Тз/2 (фиг.2,к2) соединен соответственно с входами элементов ИЛИ 26 и 24,

Импульсы с длительностью Тз/2 и Тз, сформированные с помощью элементов ИЛИ 24 и 26, поступают соответственно с их выходов (фиг.2,л,м) к первому и второму входам сумматора 28 непосредственно и через преобразователь 27 уровня, обеспечивающий преобразование положительных импульсов (фиг.2,м) в отрицательные (фиг.2,MI), в результате чего на выходе сумматора формируется разнополярный вось- мипозиционный сигнал с длительностью импульсов Тз/2 и Тз (фиг.2,о), удельная ско- рость передачи которого в 3 раза превышает удельную скорость передачи исходного двоичного сигнала (фиг.2,а).

В соответствии с предлагаемым алгоритмом преобразования, при равной веро- ятности появления 1 и О в структуре исходной двоичной последовательности (Р(1) Р(0) 0,5) и при достаточно длинном интервале анализа, постоянная составляющая в спектре разнополярного восьмипози- ционного сигнала отсутствует.

При появлении комбинаций 000 в структуре входной двоичной последовательности на выходе сумматора формируются разнополярные импульсы ( ±1 или + 1) с длительностью Тз/2, причем полярность импульсов при кодировании каждой последующей комбинации 000 изменяется на обратную по отношению к полярности импульсов предыдущей кодируемой комбина- ции, что, в свою очередь, улучшает текущую балансировку восьмипозиционного сигнала по постоянной составляющей и повышает его помехоустойчивость.

Для обеспечения одинаковой помехозащищенности импульсов, передаваемых с длительностью Тз/2 иТз, введена корректировка выходных импульсов, в соответствии с которой амплитуда положительных и отрицательных импульсов с длительностью Тз уменьшается соответственно на величину ±AU (с учетом искажений, вносимых линией связи при заданной скорости передачи), что достигается с выхода элементов И 16 и 17 (фиг.2,жб,ж) через элемент ИЛИ 25 (фиг.2,н) на третий (управляющий) вход сумматора 28.

Практически предлагаемое устройство выполнено, в основном, на элементах логики (И, ИЛИ, НЕ), генераторе импульсов, делителе частоты 1:3, последовательном и параллельном регистрах, триггере, сумматоре и дешифраторе, в качестве которого может быть использован, например, дешифратор типа ИД 161.

Элементы задержки (2,6,20,21) могут быть реализованы на одновибраторе с регулируемой времязадающей цепочкой RC с переменным резистором R, включенной в цепи его запуска, а элемент 19 задержки может быть выполнен, например, на двух последовательно включенных элементах НЕ.

Преобразователь 27 уровня может быть реализован на операционном усилителе с обратной связью с использованием инвертирующего входа.

Так как в процессе преобразования двоичного кода в восьмипозиционный временной код длительность формируемых импульсов увеличивается в 3 раза (Тз/2 3Ti/2), а частота их следования уменьшается соответственно в 3 раза (Рз 1/Тз 1 /3Ti Fi/3), то принимая во внимание тот факт, что каждый из символов восьмипозиционного сигнала несет в себе информацию о трех двоичных символах, можно утверждать, что удельная скорость передачи разно- полярного восьмипозиционного сигнала увеличивается также в 3 раза по сравнению с удельной скоростью передачи исходного двоичного сигнала.

Следовательно, положительный эффект, получаемый с помощью предлагаемого устройства, превышает в 1,5 раза положительный эффект, достигаемый с помощью прототипа, так как каждый из символов четырехпозиционного сигнала несет в себе информацию только о двух двоичных символах (К 3:2 1,5).

Формула изобретения Преобразователь двоичного кода в восьмипозиционный временной код, содержащий последовательный регистр, информационный вход которого является входом преобразователя, выходы последовательного регистра соединены с одноименными информационными входами параллельного регистра, генератор импульсов, выход которого соединен через первый элемент задер- жки с тактовым входом последовательного регистра и входом делителя частоты, выход которого соединен через последовательно соединенные первый элемент НЕ и второй элемент задержки с тактовым входом па- раллельного регистра и первыми входами первого, второго и третьего элементов И, четвертый-девятый элементы И, выходы четвертого и шестого элементов И соединены соответственно с первым и вторым вхо- дами первого элемента ИЛИ, выход которого соединен с первым входом сумматора, выходы пятого и седьмого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, вы- ход которого соединен через преобразователь уровня с вторым входом сумматора, выход первого элемента И соединен через третий элемент задержки с первыми входами восьмого и девятого элементов И, триг- гер, прямой и инверсный выходы которого соединены с вторыми входами соответственно восьмого и девятого элементов И, выходы которых соединены с третьими входами соответственно первого и второго элементов ИЛИ, выход сумматора является выходом преобразователя, третий элемент

ИЛИ и четвертый элемент задержки, отличающийся тем, что, с целью повышения быстродействия преобразователя, в него введены дешифратор, второй элемент НЕ, пятый элемент задержки и четвертый элемент ИЛИ, первый и второй входы которого подключены к выходам соответственно шестого и седьмого элементов И, выход четвертого элемента ИЛИ соединен с третьим входом сумматора, вход и выход четвертого элемента задержки соединены соответственно с выходом девятого элемента И и четвертым входом первого элемента ИЛИ, вход и выход пятого элемента задержки соединены соответственно с выходом восьмого элемента И и четвертым входом второго элемента ИЛИ, выходы второго и третьего элементов И соединены с пятыми входами соответственно первого и второго элементов ИЛИ, входы триггера подключены к выходу первого элемента И, вход второго элемента НЕ объединен с первым входом третьего элемента ИЛИ и подключен к выходу второго элемента задержки, выход второго элемента НЕ соединен с первыми входами четвертого и пятого элементов И и вторым входом третьего элемента ИЛИ, выход которого соединен с управляющими входами дешифратора и первыми входами шестого и седьмого элементов И, выходы параллельного регистра соединены с одноименными информационными входами дешифратора, выходы нулевого, второго-седьмого разрядов которого соединены с вторыми входами соответственно первого-седьмого элементов И.

ю

сч г- о со г-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема дискретной информации | 1990 |

|

SU1807579A1 |

| Преобразователь двоичного кода в четырехпозиционный код | 1988 |

|

SU1594703A1 |

| Преобразователь двоичного кода в четырех-позиционный временной код | 1990 |

|

SU1757104A1 |

| Устройство для уплотнения каналов связи | 1990 |

|

SU1809544A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

| Преобразователь восьмипозиционного временного кода в двоичный код | 1990 |

|

SU1771070A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Медианный рекурсивный фильтр | 1988 |

|

SU1654837A1 |

| Автокорреляционный измеритель параметров псевдослучайного фазоманипулированного сигнала | 1990 |

|

SU1823137A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

Изобретение относится к радиотехнике вычислительной технике и может использоваться в системах передачи дискретной информации Устройство обеспечивает трехкратное повышение удельной скорости передачи путем преобразования двоичных сигналов в восьмипозиционные, что достигается в результате увеличения длительности формируемых импульсов и уменьшения частоты их следования. Устройство содержит генератор 1 импульсов, делитель 3 частоты, элементы И 11-17,22,23, ИЛИ 9, 25.НЕ 4,8 элементы 2,6,19-21 задержки, регистры 5, 7, триггер 18, дешифратор 10, преобразователь 27 уровня и сумматор 28 2 ил 1 табл CO с J CO о v| hO СП ; 1 -УЗН1-| t} ii,i / 28 | L П Г/г Л7

| УСТРОЙСТВО ДЛЯ СТАБИЛИЗАЦИИ ВИНОГРАДНЫХ СОКОВ И ВИН | 1997 |

|

RU2124049C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-04-30—Публикация

1990-04-23—Подача