ел С

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник рекуррентных последовательностей | 1985 |

|

SU1256232A1 |

| Устройство для контроля монотонно изменяющегося кода | 1988 |

|

SU1658190A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Преобразователь кода | 1987 |

|

SU1557685A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1991 |

|

RU2013017C1 |

| Устройство коррекции кода | 1986 |

|

SU1490720A1 |

| Устройство для контроля сбоев псевдослучайного испытательного сигнала | 1983 |

|

SU1172056A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ АНОМАЛЬНЫХ ЦИФРОВЫХ ОШИБОК ПРИ ПЕРЕДАЧЕ РЕЧИ МЕТОДОМ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИИ | 1999 |

|

RU2159470C1 |

| Устройство для контроля регистра сдвига | 1981 |

|

SU964646A1 |

| Многоканальная кодоимпульсная система телесигнализации | 1986 |

|

SU1325544A1 |

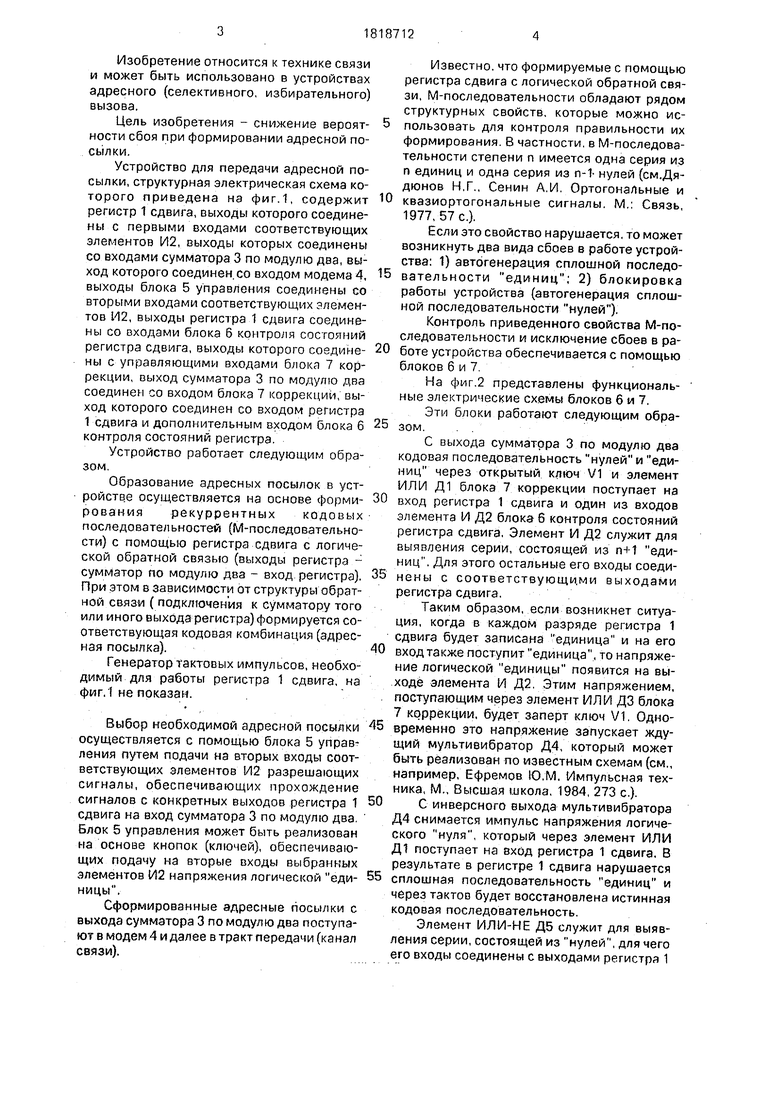

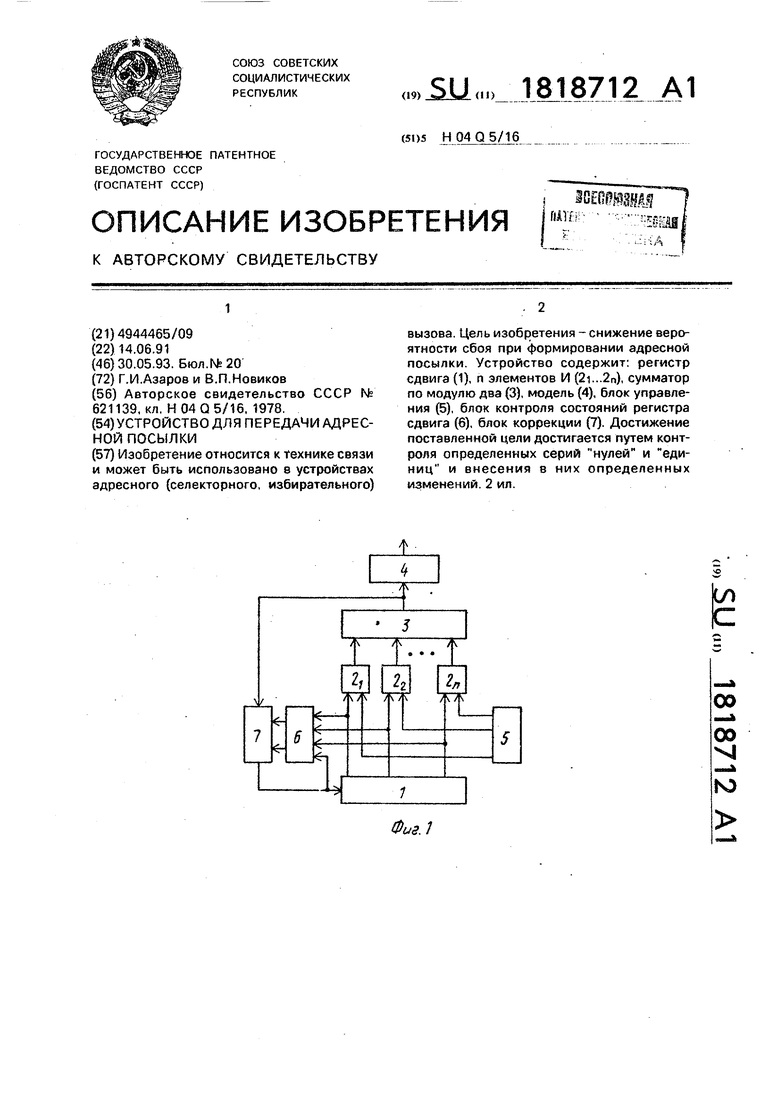

Изобретение относится к технике связи и может быть использовано в устройствах адресного (селекторного, избирательного) вызова. Цель изобретения - снижение вероятности сбоя при формировании адресной посылки. Устройство содержит: регистр сдвига (1), п элементов И (2i...2n), сумматор по модулю два (3), модель (4), блок управления (5), блок контроля состояний регистра сдвига (6), блок коррекции (7). Достижение поставленной цели достигается путем контроля определенных серий нулей и единиц и внесения в них определенных изменений. 2 ил.

ФиЗ.1

09

00 XI

ю

Изобретение относится к технике связи и может быть использовано в устройствах адресного (селективного, избирательного) вызова.

Цель изобретения - снижение вероятности сбоя при формировании адресной посылки.

Устройство для передачи адресной посылки, структурная электрическая схема которого приведена на фиг.1, содержит регистр 1 сдвига, выходы которого соединены с первыми входами соответствующих элементов И2, выходы которых соединены со входами сумматора 3 по модулю два, выход которого соединен со входом модема 4, выходы блока 5 управления соединены со вторыми входами соответствующих элементов И2, выходы регистра 1 сдвига соединены со входами блока 6 контроля состояний регистра сдвига, выходы которого соединены с управляющими входами блока 7 коррекции, выход сумматора 3 по модулю два соединен со входом блока 7 коррекций, выход которого соединен со входом регистра 1 сдвига и дополнительным входом блока 6 контроля состояний регистра.

Устройство работает следующим образом.

Образование адресных посылок в устройстве осуществляется на основе формирования рекуррентных кодовых последовательностей (М-последовательно- сти) с помощью регистра сдвига с логической обратной связью (выходы регистра - сумматор по модулю два - вход регистра). При этом в зависимости от структуры обратной связи (подключения к сумматору того или иного выхода регистра) формируется соответствующая кодовая комбинация (адресная посылка).

Генератор тактовых импульсов, необходимый для работы регистра 1 сдвига, на фиг.1 не показан.

Выбор необходимой адресной посылки осуществляется с помощью блока 5 управления путем подачи на вторых входы соответствующих элементов 1/12 разрешающих сигналы, обеспечивающих прохождение сигналов с конкретных выходов регистра 1 сдвига на вход сумматора 3 по модулю два. Блок 5 управления может быть реализован на основе кнопок (ключей), обеспечивающих подачу на вторые входы выбранных элементов И2 напряжения логической единицы.

Сформированные адресные посылки с выхода сумматора 3 по модулю два поступают в модем 4 и далее в тракт передачи (канал связи).

Известно, что формируемые с помощью регистра сдвига с логической обратной связи, М-последовательности обладают рядом структурных свойств, которые можно использовать для контроля правильности их формирования. В частности, в М-последовательности степени п имеется одна серия из п единиц и одна серия из п-1- нулей (см.Дя- дюнов Н.Г., Сенин А.И. Ортогональные и

квазиортогональные сигналы. М.: Связь, 1977,57с.).

Если это свойство нарушается, то может возникнуть два вида сбоев в работе устройства: 1) автогенерация сплошной последо5 вательности единиц ; 2) блокировка работы устройства (автогенерация сплошной последовательности нулей).

Контроль приведенного свойства М-последовательности и исключение сбоев в ра0 боте устройства обеспечивается с помощью блоков 6 и 7.

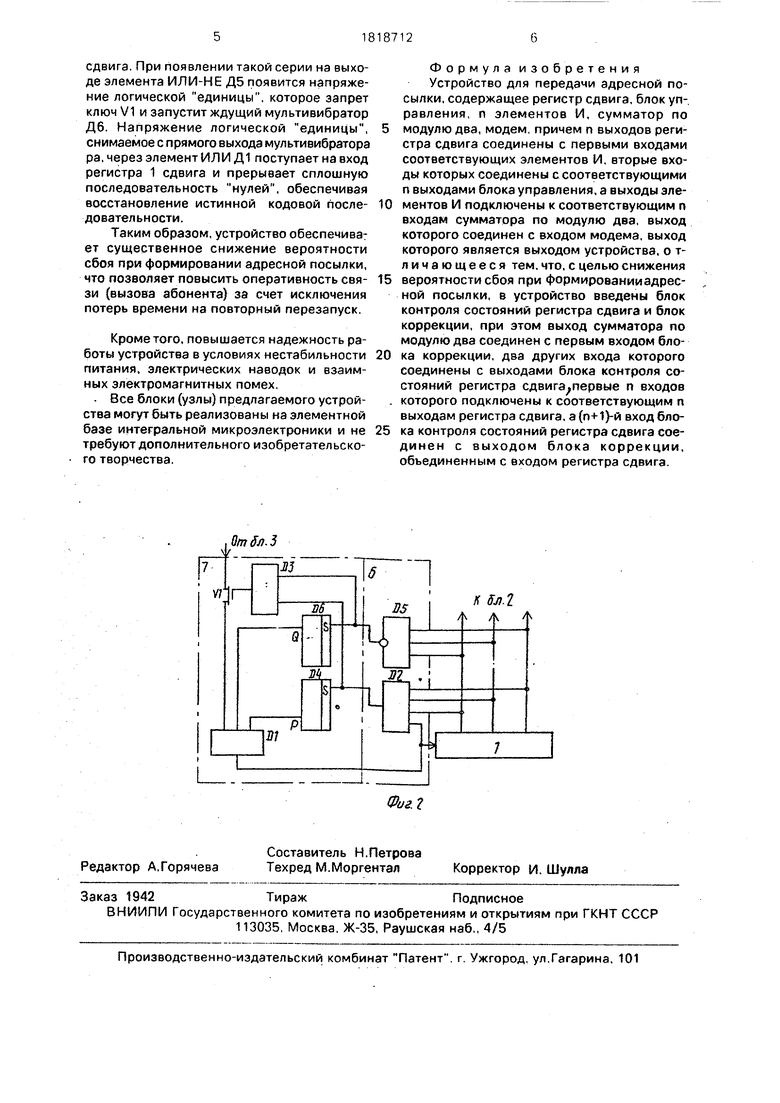

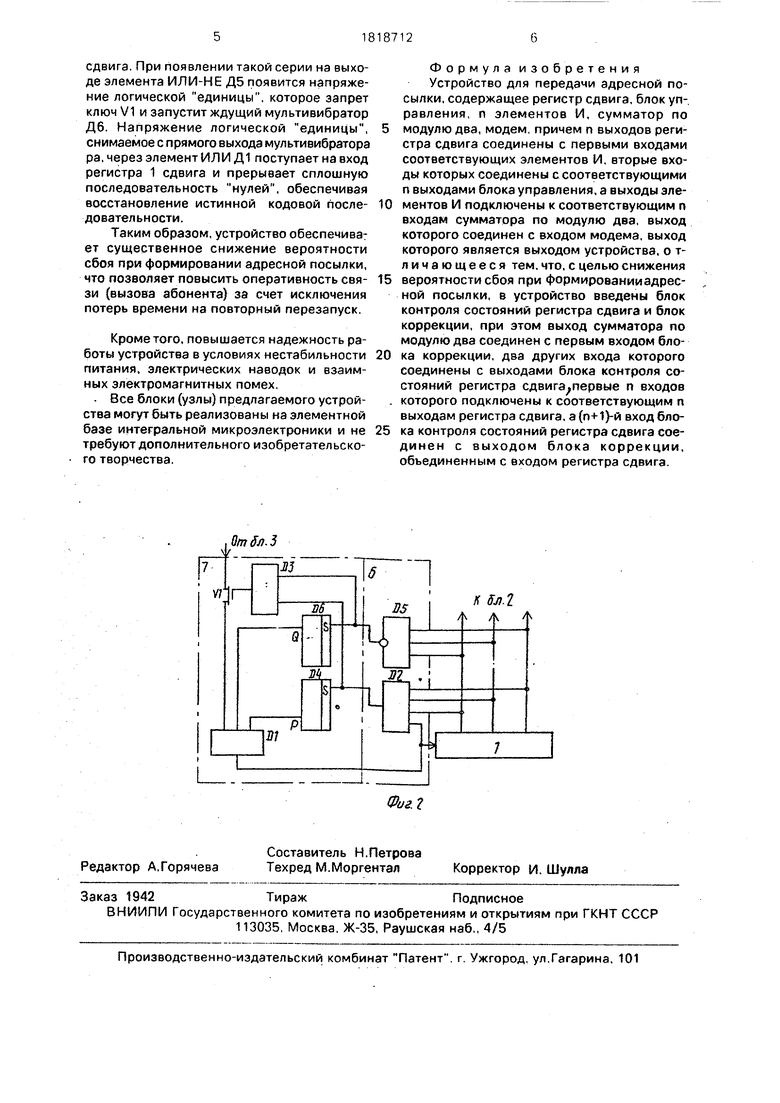

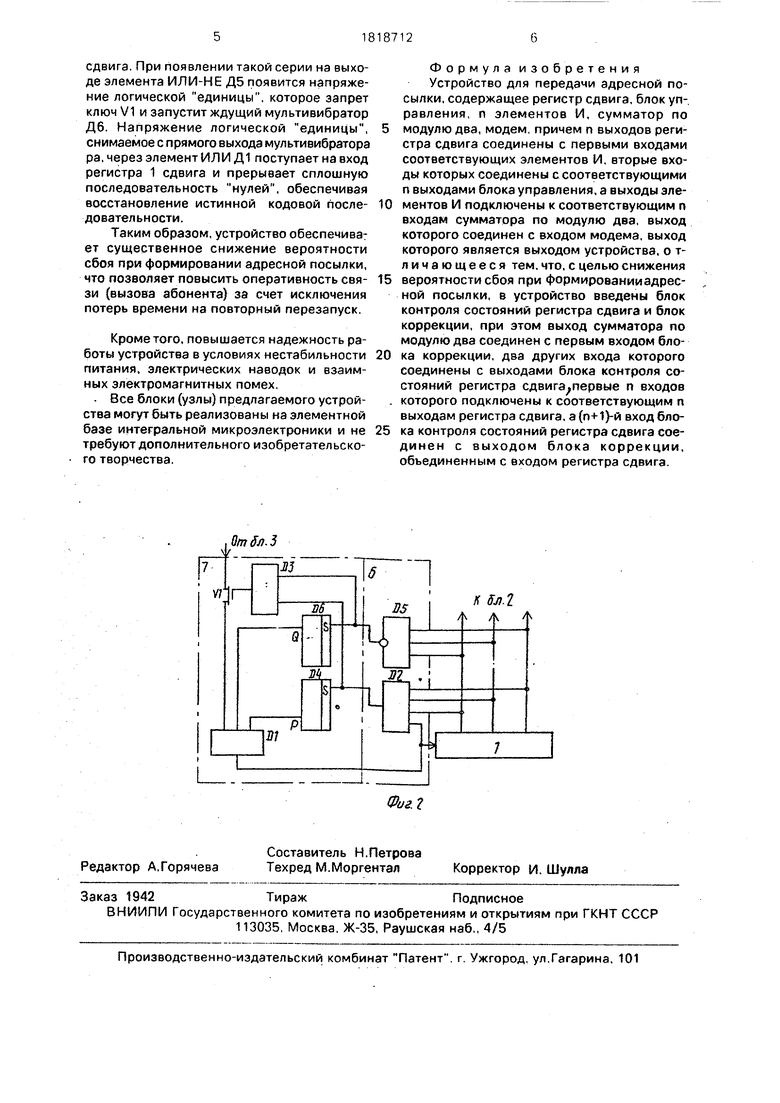

На фиг.2 представлены функциональные электрические схемы блоков б и 7. Эти блоки работают следующим обра5 зом. . .

С выхода сумматора 3 по модулю два кодовая последовательность нулей и единиц через открытый ключ V1 и элемент ИЛИ Д1 блока 7. коррекции поступает на

0 вход регистра 1 сдвига и один из входов элемента И Д2 блока 6 контроля состояний регистра сдвига, Элемент И Д2 служит для выявления серии, состоящей из n+t единиц. Для этого остальные его входы соеди5 нены с соответствующими выходами регистра сдвига.

Таким образом, если возникнет ситуация, когда в каждом разряде регистра 1 сдвига будет записана единица и на его

0 вход также поступит единица, то напряжение логической единицы появится на выходе элемента И Д2. Этим напряжением, поступающим через элемент ИЛИ ДЗ блока 7 коррекции, будет заперт ключ V1. Одно- 5 временно это напряжение запускает ждущий мультивибратор Д4, который может быть реализован по известным схемам (см., например, Ефремов Ю. М. Импульсная техника, М., Высшая школа, 1984, 273 с.).

0 с инверсного выхода мультивибратора Д4 снимается импульс напряжения логического нуля, который через элемент ИЛИ Д1 поступает на вход регистра 1 сдвига. В результате в регистре 1 сдвига нарушается

5 сплошная последовательность единиц и через тактов будет восстановлена истинная кодовая последовательность.

Элемент ИЛИ-НЕ Д5 служит для выявления серии, состоящей из нулей, для чего его входы соединены с выходами регистра 1

сдвига. При появлении такой серии на выходе элемента ИЛИ-НЕ Д5 появится напряжение логической единицы, которое запрет ключ V1 и запустит ждущий мультивибратор Д6. Напряжение логической единицы, снимаемое с прямого выхода мультивибратора ра, через элемент ИЛИ Д1 поступает на вход регистра 1 сдвига и прерывает сплошную последовательность нулей, обеспечивая восстановление истинной кодовой после- довательности.

Таким образом, устройство обеспечива: ет существенное снижение вероятности сбоя при формировании адресной посылки, что позволяет повысить оперативность свя- зи (вызова абонента) за счет исключения потерь времени на повторный перезапуск.

Кроме того, повышается надежность работы устройства в условиях нестабильности питания, электрических наводок и взаимных электромагнитных помех.

. Все блоки (узлы) предлагаемого устройства могут быть реализованы на элементной базе интегральной микроэлектроники и не требуют дополнительного изобретательского творчества.

От 6л 3

Формула изобретения Устройство для передачи адресной посылки, содержащее регистр сдвига, блок управления, п элементов И, сумматор по модулю два, модем, причем п выходов регистра сдвига соединены с первыми входами соответствующих элементов И, вторые входы которых соединены с соответствующими п выходами блока управления, а выходы элементов И подключены к соответствующим п входам сумматора по модулю два, выход которого соединен с входом модема, выход которого является выходом устройства, о т- личающееся тем. что, с целью снижения вероятности сбоя при формировании адресной посылки, в устройство введены блок контроля состояний регистра сдвига и блок коррекции, при этом выход сумматора по модулю два соединен с первым входом блока коррекции, два других входа которого соединены с выходами блока контроля состояний регистра сдвига первые п входов которого подключены к соответствующим п выходам регистра сдвига, а(п+1)-й вход блока контроля состояний регистра сдвига соединен с выходом блока коррекции, объединенным с входом регистра сдвига.

| Устройство для передачи адресной посылки | 1977 |

|

SU621139A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-05-30—Публикация

1991-06-14—Подача