Изобретение относится к вычислительной технике и может быть использовано для построения интерфейсных устройств микропроцессорных систем.

Целью изобретения является расширение области применения и повышение быстродействия,,

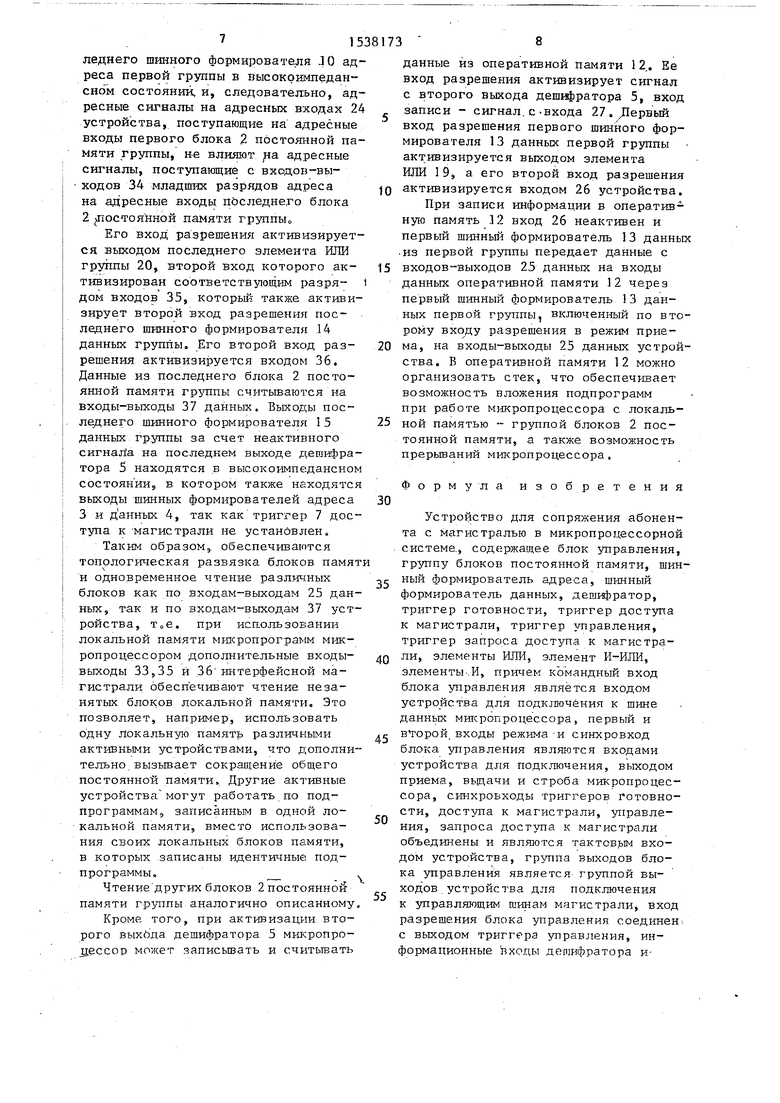

На чертеже представлена функциональная схема предлагаемого устройства микропроцессорной связи.

Устройство состоит из блока 1 управления (системного контролера), группы блоков 2 постоянной памяти, шинного формирователя 3 адреса, шинного формирователя 4 данных, дешифратора 5, триггера б готовности, триггера 7 доступа к магистрали, триггера 8 управления, триггера 9 запроса доступа к магистрали, первой группы шинных формирователей 10 адреса, второй группы шинных формирователей 11 адреса, оперативной памяти 12, первой группы шинных формирова- телей 13 данных, второй группы шинных формирователей 14 данных, второг и третьего элементов ИЛИ 15 и 168 элемента И-ИЛИ 17, первого элемента ИЛИ 18, четвертого элемента ИЛИ 19, группы элементов ИЛИ 20, первого, третьего и второго элементов И 21- 23, входов 24 адреса, входов-выходов 25 данных, входа 26 приема, входа 27 выдачи, входа 28 строба, так- тового входа 29, выхода 30 готовности, входа 31 ожидания, выходов 32 старших разрядов адреса, группы выходов 33 занятости, входов-выходов 34 младших разрядов адреса, группы входов 35 разрешения чтения, входа 36 приема, входов-выходов 37 данных, группы выгодов 38 управления, входа 39 ответа, входа 40 разрешения доступа, выхода 41 запроса доступа.

Входы 24 адреса, входы-выходы 25 данных, входы 26,27 и 31, вход 28 синхронизации, тактовый вход 29, выход 31 устройства подключаются к стандартным выходам адреса, входам- выходам данных и к шине управления микропроцессора соответственно. Выходы 32 старших разрядов адреса, входы-выходы 34 младших разрядов адреса, входы-выходы Л данных, выходы 38 и 41, входы 39 и 40 подключаются к соответствующим разрядам стандартного интерфейса магистрали.

Устройство работает следующим образом с

В системный контроллер 1 по вхо дам-выходам4 25 устройства по переднему фронту строба на входе 28 (выход шины управления микропроцессора Строб) записывается слово состояния микропроцессора0 Системный конт- роллер 1 по слову состояния микропроцессора, входам 26 (Прием), 27 (Выдача) формирует сигналы управления устройства. Если информация, выставляемая на входах 24, не входит во множество адресов, идентифицирующих группу блоков 2 постоянной памяти или оперативную память 12, то вы

.

Q г п 5

0 5

0

5

ходы дешифраторов 5 не активизированы. Поэтому неактивен и выход элемента ИЛИ 18. В то же время активизирован выход, элемента ИЛИ 16, так как его входы активизированы одним из входов 26 (Прием) или 27 (Выдача) в зависимости от цикла работы микропроцессора.

Все это приводит к тому, что по переднему фронту импульса на тактовом входе 29 (Фаза 2 микропроцессора) устанавливается триггер запроса доступа к магистрали 9, так как его информационный вход активизирован выходом элемента И 23. Выход триггера запроса доступа к магистрали 9 активизирует выход 41 Запрос доступа к магистрали. Если не активизирован вход 40 управления Разрешение доступа к магистрали, то устанавливается триггер доступа к магистрали. 7 также по переднему фронту импульса на тактовом входе 29 устройства, так как его информационный вход активизирован выходом элемента И 21 . Если выход 39 Ответ равен логической 1, то логический О на выходе триггера 6 готовности удерживает по выходу 30 Готовность микропроцессор в состоянии ожидания, что сопровождается, в свою очередь, активизацией входа 31 Ожидание устройства. Поэтому активизируется выход элемента И 22 и по переднему фронту импульса на тактовом входе 29 устройства устанавливается триггер 8 управления. Выходной сигнал триггера 8 управления подключает шинный формирователь адресов 3 и данных 4 к интерфейсной магистрали. Таким образом, адресные выходы микропроцессора по входам 24 адреса устанавливают на интерфейсной магистрали адрес устройства, с которым будет происходить обмен. Выходной сигнал триггера 8 управления обеспечивает подключение выходов системного контроллера 1 к разрядам управления интерфейсной магистрали Таким образом выдается сигнал чтения или записи.

При появлении на выходе 39 сигнала логического О, сввдетельствующего о том, что данные приняты, либо установлены на входы-выходы 37 данных устройством, с которым происходит обмен, активизируется выход элемента ИЛИ 15 соответственно устанавливается по переднему фронту импульса

на тактовом входе 29 триггера 6 готовности. Этим формируется сигнал готовности для микропроцессора по выходу 30 управления, получив который, он1снимает сигнал ожидания с входа 31 управления, что, в свою очередь, приводит к обнулению триггера 8 управления. Таким образом, выходы системного контроллера 1 переводятся в высокоимпедансное состояние и снимаются сигналы управления с интерфейсной магистрали. Прием или выдача данных по входам-выходам 25 данных завершается снятием микропроцессором соответствующих управляющих сигналов с входов 26 и 27 управления. Таким образом происходит обмен информацией микропроцессора с внешним устройством аналогично известному устройству.

Если же микропроцессор обращается к группе блоков 2 постоянной памяти, которая является локальной, то это сопровождается активизацией одного из выходов дешифратора 5, который подключается к входам 24 выходом элемента И-ИЛИ 17, второй и третий входы которого активизируются одним из входов 26 или 27, а выход которого активизирует разрешающий вход дешифратора 5, первый вход элемента И-ИЛИ 17 активизируется неактивным уровнем сигнала на входе 28 управления. Следовательно, активизируется выход элемента ИЛИ 18, что приводит к активизации второго входа элемента ИЛИ 15. Поэтому по переднему фронту импульса на тактовом входе 29 устанавливается триггер 6 готовности. Активный сигнал с выхода элемента ИЛИ 18 запрещает установку триггеров 7 доступа к магистрали и запроса доступа к магистрали 9. Выходной сигнал триггера 6 готовности обеспечивает формирование готовности микропроцессора по выходу 30, который, следовательно, не входит в режим ожидания. Выходные сигналы дешифратора 5 также поступают на выходы 33, которые подключаются к допол- ните льным разрядам интерфейсной магистрали Код занятости локальной памяти.

Активный уровень на первом выходе дешифратора 5 приводит к активизации выхода элемента ИЛИ 19, который, в свою очередь, активизирует входы разрешения первого шинного формиро

8173

10

вателя 10 адреса первой группы, блокирует входы разрешения первого шинного формирователя TJ адреса второй группы, активизирует первый вход - разрешения первого шинного формирователя 13 данных первой группы. Второй вход разрешения первого шинного формировател 13 данных первой группы активизируется входом 26 При

0

5

0

ем при выставлении микропроцессором этого сигнала. Таким образом, через первый шинный формирователь 10 адреса первой группы на адресные входы первого блока 2 постоянной памяти группы поступают младшие разряды адресных сигналов с входов 24 адреса и не могут поступить адресные сигналы с входов-выходов 34 младших разрядов адреса через первый шинный формирователь 11 адреса второй группы, выходы которого находятся в вы- сокоимпедансном состоянии. Вход разрешения первого блока 2 постоянной памяти группы активизируется выходом первого элемента ИЛИ группы 20, первый вход которого активизирован первым выходом дешифратора 5. Данные из первого блока 2 постоянной памяти группы поступают на входы первого шинного формирователя 13 данных первой группы, а с его входов-выходов - на первые входы-выходы 25 данных устройства и с них в микропроцессор.

Информация на выходах 33 указывает, к какому из блоков 2 постоянной памяти группы происходит обращение. К остальным блокам доступ разрешен и по активному уровню сигнала на выходах 33. На входы 35 подается унитарный код незанятого блока памяти из группы блоков 2 постоянной памяти, на входы-выходы 34 младших разрядов адреса подается адрес требуемой ячейки памяти в незанятом блоке памяти, а на вход 36 подается активный уровень сигнала чтения„ Таким образом, например, на последний блок памяти из группы блоков 2 постоянной памяти адрес подается с входов- выходов 34 младших разрядов адреса через последний шинный формирователь I 1 адреса второй rpynnbiv первый и второй входы разрешения которого активизированы .неактивным уровнем сигнала на последнем выходе дешифратора 5. В свою очередь, неактивный уровень сигнала на этом выходе дешифратора 5 обеспечивает удержание выходов пос5

0

5

0

15

леднего шинного формирователя JO адреса первой группы в высокоимпедан- сном состоянии, и, следовательно, адресные сигналы на адресных входах 24 устройства, поступающие на адресные входы первого блока 2 постоянной памяти группы, не влияют ра адресные сигналы, поступающие с входов-выходов 34 младших разрядов адреса на адресные входы последнего блока

2 постоянной памяти группы

Его вход разрешения активизируется выходом последнего элемента ИЛИ группы 20, второй вход которого активизирован соответствующим разря- дом входов 35, который также активизирует второй вход разрешения последнего шинного формирователя 14 данных группы. Его второй вход разрешения активизируется входом 36. Данные из последнего блока 2 постоянной памяти группы считываются на входы-выходы 37 данных. Выходы последнего шинного формирователя 15 данных группы за счет неактивного сигнала на последнем выходе дешифратора 5 находятся в высокоимпедаисном состоянии, в котором также находятся выходы шинных формирователей адреса

3и данных 4, так как триггер 7 доступа к магистрали не установлен.

Таким образом, обеспечиваются топологическая развязка блоков памят и одновременное чтение различных блоков как по входам-выходам 25 данных, так и по входам-выходам 37 устройства, т0е. при использовании локальной памяти микропрограмм микропроцессором дополнительные входы- выходы 33935 и 36 интерфейсной магистрали обеспечивают чтение незанятых блоков локальной памяти. Это позволяет, например, использовать одну локальную память различными активными устройствами, что дополнительно вызывает сокращение общего постоянной памяти. Другие активные устройства могут работать по подпрограммам, записанным в одной локальной памяти, вместо использования своих локальных блоков памяти, в которых записаны идентичные подпрограммы.

Чтение других блоков 2 постоянной памяти группы аналогично описанному

Кроме того, при активизации второго выхода дешифратора 5 микропроцессор может записывать и считывать

V

10

15

20

25

8173

30

35

40

45

50

55

8

данные из оперативной памяти 12. Ее вход разрешения активизирует сигнал с второго выхода дешифратора 5, вход записи - сигнал с-входа 27 . Первый вход разрешения первого шинного формирователя 13 данных первой группы активизируется выходом элемента ИЛИ 19, а его второй вход разрешения активизируется входом 26 устройства. При записи информации в оперативную память 12 вход 26 неактивен и первый шинный формирователь 13 данных из первой группы передает данные с входов-выходов 25 данных на входы данных оперативной памяти 12 через первый шинный формирователь 13 данных первой группы, включенный по второму входу разрешения в режим приема, на входы-выходы 25 данных устройства. В оперативной памяти 12 можно организовать стек, что обеспечивает возможность вложения подпрограмм при работе микропроцессора с локальной памятью - группой блоков 2 постоянной памяти, а также возможность прерываний микропроцессора,

Формула изобретения

Устройство для сопряжения абонента с магистралью в микропроцессорной системе, содержащее блок управления, группу блоков постоянной памяти, шинный формирователь адреса, шинный формирователь данных, дешифратор, триггер готовности, триггер доступа к магистрали, триггер управления, триггер запроса доступа к магистрали, элементы ИЛИ, элемент И-ИЛИ, элементы И, причем командный вход блока управления является входом устройства для подключения к шине данных микропроцессора, первый и второй входы режима и синхровход блока управления являются входами устройства для подключения, выходом приема, выдачи и строба микропроцессора, синхроьходы триггеров готовности, доступа к магистрали, управления, запроса доступа к магистрали объединены и являются тактовым входом устройства, группа выходов блока управления является группой выходов устройства для подключения к управляющим шинам магистрали, вход разрешения блока управления соединен с выходом триггера управления, информационные входы дешифратора и

шинного формирователя адреса являются группой входов устройства для подключения к адресной шине микро- процессора, выходы дешифратора через первый элемент ИЛИ соединены с первыми входами второго элемента.ИЛИ, первого и второго элементов И, второй вход второго элемента ИЛИ является входом устройства для подключения к шине Ответ магистрали, выход второго элемента ИЛИ подключен к информационному входу триггера готовности, выход которого является выходом готовности устройства, входы третьего элемента ИЛИ соединены соответственно с входами устройства для подключения выходов приема и выдачи микропроцессора, выход третьего элемента ИЛИ соединен с вторыми входами первого и второго элементов И, третий вход первого элемента И является входом устройства для подключения к шине разрешения доступа магистрали, а выход первого элемента И соединен с информационным входом триггера доступа к магистрали, выход которого подключен к первому входу третьего элемента И, к первому входу разрешения шинного формирователя данных и к входу разрешения шинного формирователя адреса, третий вход третьего элемента И объединен с входом сброса триггера управления и является входом устройства для подключения к шине ожидания микропроцессора, выход третьего элемента И соединен с информационным входом триггера управления, выход второго элемента И соединен с информационным входом триггера запроса доступа к мегистрали, выход которого является выходом устройства для подключения к шине запроса доступа магистрали, первый, второй и третий входы элемента И-ИЛИ являются входами устройства для подключения к шинам приема, выдачи и строба микропроцессора, выход элемента И-ИЛИ соединен с входом разрешения дешифратора, информационные входы шинного формирователя данных подключены к входам устройства для подключения к шине данных микропроцессора, выходы шинного формирователя данных являются выходами устройства для подключения к шинам данных магистрали, второй вход разрешения шинного формирователя данных подключен к входу устройства

0

5

0

5

0

5

0

5

0

5

для подключения к шине приема микропроцессора, отличающееся тем, что, с целью расширения области применения и повышения быстродействия, оно содержит две группы шинных формирователей данных, оперативную память, четвертый элемент ИЛИ и группу элементов ИЛИ, причем первый и второй выходы дешифратора соединены с первьм и вторым входами четвертого элемента ИЛИ, выход которого соединен с входами разрешения первых шинных формирователей адреса первой и второй групп и к первому входу разрешения первого шинного формирователя данных первой группы, первый выход дешифратора соединен с входом разрешения оперативной памяти, вход записи которой подключен к входу устройства для подключения к шине выдачи микропроцессора, входы-выходы первого шинного формирователя адреса первой группы объединены с входами-выходами первого шинного формирователя адреса второй группы и соединены с адресными входами первого блока постоянной памяти группы и оперативной памяти, входы- выходы шинных формирователей адреса первой группы, начиная с второго, объединены с входами-выходами одноименных шинных формирователей адреса второй группы и соединены с адресными входами одноименных блоков постоянной памяти группы, группа выхо дов первого блока постоянной памяти группы и группа выходов оперативной памяти объединены и соединены с группами информационных входов первых шинных формирователей данных первой и второй групп, группы выходов блоков постоянной памяти группы, начиная с второго, соединены с группами информационных входов одноименных шинных формирователей данных первой и второй группы, входы чтения блоков постоянной памяти группы соединены с выходами соответствующих элементов ИЛИ группы, первые входы которых, а также разрешающие входы шинных формирователей адреса, кроме первых, первой и второй групп и первые разрешающие входы шинных формирователей данных, кроме первого, первой группы соединены с соответствующими выходами дешиЬратора, вторые входы элементов ИЛИ группы и первые разрешающие входы гаиннпх формирователей данных иторой группы образуют группу входов устройства для подключения к шинам разрешения считывания магистрали, вторые разрешающие входы шинных формирователей данных первой и второй групп образуют соответствующие входы устройства для подключения соответственно к шине приема микропроцессора и шине приема магистрали, входы-выходы данных вшнных формирователей данных первой группы подключены к входу-выходу устройства для подключения к шине данных микропроцессора, выходы данных шинных формирователей данных второй группы образуют выход устройства для подключения к шине данных магистрали, группа выходов данных первого шин ного формирователя данных первой группы соединена с группой входов данных

оперативной памяти, группы информационных входов шинных формирователей адреса первой группы и вторая группа информационных входов шинного

формирователя адреса подключены к входам устройства для подключения к адресной шине микропроцессора, первая группа выходов шинного формирователя адреса является группой выходов устройства для подключения к старшим разрядам адресной шины магистрали, входы данных шинных формирователей адреса второй группы подключены к второй группе выходов шинногоформирователя адреса и образуют группу входов-выходов устройства для подключения к младшим разрядам адресной шины магистрали, группа выходов дешифратора является группой выходов

0 устройства дня подключения к шинам занятости магистрали.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Микропроцессорная система для программного управления технологическим оборудованием | 1988 |

|

SU1525678A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1476434A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения интерфейсных устройств микропроцессорных систем. Целью изобретения является расширение области применения и повышение быстродействия. Поставленная цель достигается тем, что в устройство микропроцессорной связи содержащее блок управления, группу блоков постоянной памяти, шинный формирователь адреса, шинный формирователь данных, дешифратор, триггер готовности, триггер доступа к магистрали, триггер управления, триггер запроса доступа к магистрали, первый, второй и третий элементы ИЛИ, элемент И-ИЛИ, первый, второй и третий элементы И, дополнительно введены первая и вторая группы шинных формирователей адреса, первая и вторая группы формирователей данных, оперативная память, группа элементов ИЛИ, четвертый элемент ИЛИ и образованы новые связи. Введение группы шинных формирователей адреса данных позволяет обращаться со стороны активных устройств на магистрали к соответствующим блокам постоянной или оперативной памяти во время обращения микропроцессора к другим блокам постоянной или оперативной памяти. Введение оперативной памяти позволяет осуществить работу с подпрограммами, прерываниями.е.кондрахина620.165.29а. 4 ил.в.с.шехтера.е.кондрахина620.178.7оконный световод 5, соединяющий кварцевый резонатор с фотоприемником 6, подк

14

JL

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-23—Публикация

1987-12-28—Подача