Известны устройства для перевода чисел из двоично-десятичной системы в двоичную, в которых операция перевода выполняется либо по программе, либо с привлечением сложных схем, содержащих большое количество счетчиков.

Предложенное устройство, в котором используется сдвигающий регистр, отличается тел1, что содержит источник сигнала коррекции, дешифратор коррекции, веитили, схему «ИЛИ и счетчик сдвигов. Вход дешифратора коррекции соединен с выходом счетчика сдвигов, входы первого вентиля - с источником сигнала коррекции, с выходами дешифратора коррекции и триггера старшего разряда регистра. Входы второго вентиля подключены к выходам первого и третьего вентилей, а выход второго вентиля - ко входу триггера старщего разряда регистра. Входы третьего вентиля соединены с пулевыми выходами второго триггерного регистра и с выходом схемы «ИЛИ, а входы четвертого вентиля - с выходами первого вентиля и схемы «ИЛИ. Выход четвертого вентиля подключен ко входу второго триггера регистра. Входы пятого вентиля подсоединены к выходу первого вентиля и единичному выходу четвертого триггера регистра, а выход пятого вентиля - ко входу «ретьего триггера регистра. Входы схемы

«ИЛИ соединяются с нулевыми выходами третьего и четвертого триггеров регистра.

Это позволяет упростить систему введения коррекции при делении на два.

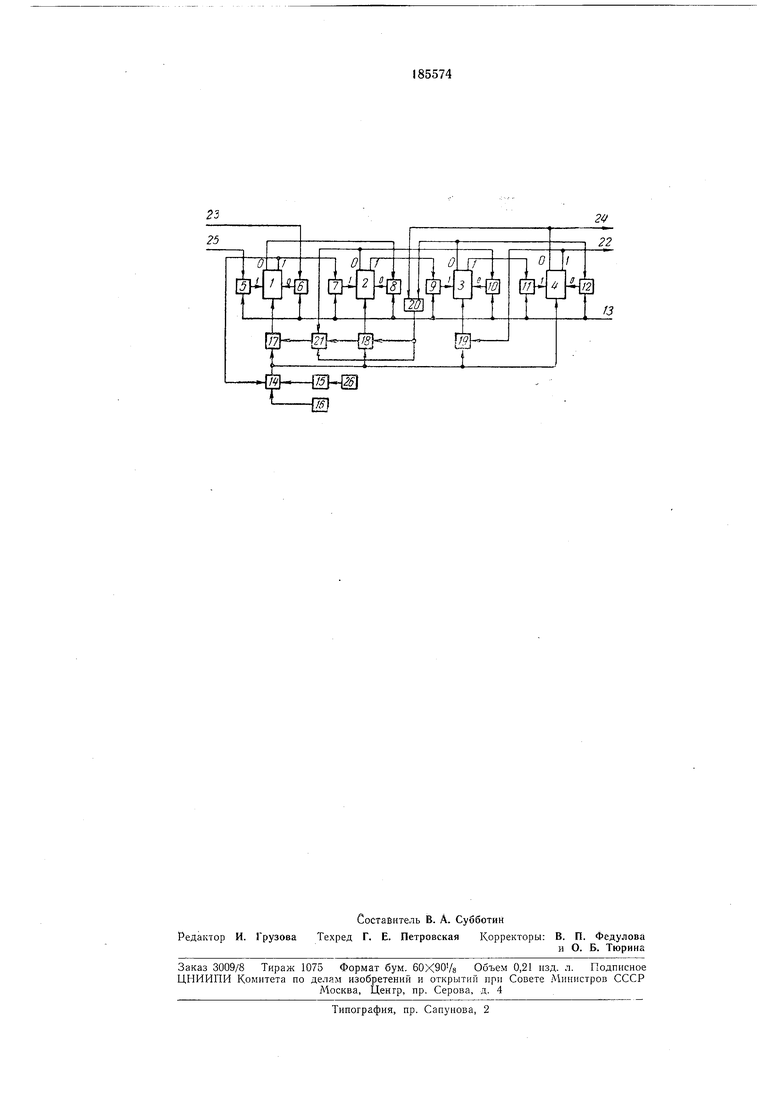

Ыа чертеже изображена предложенная схема.

Сдвиг числа в сдвигающем регистре осуществляется по обычной схеме. Выходы каладого триггера /-4 (единичный и нулевой) соединяются с соответствующими входами следующего младшего двоичного разряда через логические элементы «И о-.12. На вторые входы этих элементов «И поступают импульсы сдвига по шине 13.

Коррекция десятичного разряда должна происходить каждый раз после сдвига единицы в дапиый десятичный разряд, т. е. при наличии единицы в триггере / после сдвига. Единичный выход триггера / соединен со входом логического элемента «И 14. Иа вход этого же элемента «И поступает сигнал дешифратора 15, разрешающий коррекцию, а на другой вход - импульс коррекции от источника 16. С выхода логического элемента «И 14 сигнал поступает на счетный вход триггера 4 непосредственно, а на счетные входы триггеров 1, 2 и 3 соответственно через логические элементы «PI 17, 18 и 19. Вход логического элемента «И 19 соединен с единичным копиром триггера 4, а вход логического элемента

«И 18 - с выходом логического элемента «ИЛИ 20, на входы которого поступают сигналы с нулевых выходов триггеров 3 и 4. На вход логического элемента «И 17 поступает сигнал с выхода логического элемента «И 21. На входы логического элемента «Н 2-/ поступают сигналы с выхода логического элемента «ИЛИ 20 и нулевого выхода триггера 2.

В регистре все десятичные разряды соединены между собой следующим образом. Выход 22 сдвига единицы каждого десятичного разряда соединен с соответствующим входом

23следующего младшего десятичного разряда, а выход 24 сдвига нуля - соответственно со входом 25. Ввиду того, что в самый старший десятичный разряд сдвиг десятичных цифр не производится, он не имеет цепи коррекции.

После каждого сдвига вправо на один разряд, т. е. после каждого деления на два, на выходах 22 и 24 самого младшего десятичного разряда образуется остаток, являющийся очередной старшей цифрой двоичного числа. Остаток может быть равен единице или нулю.

В связи с тем, что при сдвиге двоично-десятичного числа вправо на один разряд в сдвигающем регистре освобождается по крайней мере один самый старщий двоичный разряд, в освободившемся разряде может быть помещено число, переведенное в двоичную систему (при каждом сдвиге получается только одна очередная цифра двоичного числа). С целью записи образующегося двоичного числа в освободившемся от десятичного числа разряде входы 23 и 25 самого старшего десятичного разряда соединены соответственно с выходами

24и 22 самого младшего десятичного разряда. При этом образованные в самом младшем десятичном разряде цифры двоичного числа поочередно будут поступать на входы самого старшего разряда.

Помещенное в сдвигающем регистре двоичное число при сдвигах коррекции не требует. Поэтому, когда освобождаются четыре двоичных разряда, в которых помещается тетрада, от очередной двоично-десятичной цифры необходимо исключить выполнение коррекции в следующем младшем десятичном разряде. Для этой цели предусмотрен счетчик 26 сдвигов и специальный дещифратор 15.

Дешифратор построен таким образом, что каждый раз после сдвига числа на четыре двоичных разряда, т. е. после освобождения одного десятичного разряда регистра от десятичной цифры, запрещается коррекция в следующем младшем разряде до окончания преобразосания. В случае преобразования п-разрядных десятичных старший п-й десятичный разряд не имеет цепи коррекции, а во всех остальных разрядах коррекция разрешена. После четырех сдвигов, т. е. после того, как

п-й десятичный разряд заведомо освободится от десятичной цифры, запрещается коррекция п-1 разряда. После следующих четырех сдвигов, т. е. после того, как п-1 разряд непременно освободится от десятичной цифры, запрещается коррекция в п-1 и п-2 десятичных разрядах. Каждйй раз после четырех сдвигов, происходит запрещение коррекции в следующем младшем десятичном разряде. При этом запрет коррекции во всех старших десятичных разрядах не снимается.

Предмет изобретения

Устройство для преобразования целых чисел из двоично-десятичной системы в двоичную,

содержащее сдвигающий регистр, отличающееся тем, что, с целью упрощения системы введения коррекции при делении на два, устройство содержит источник сигнала коррекции, дешифратор коррекции, вентили, схему

«Р1ЛИ и счетчик сдвигов, причем вход дешифратора коррекции соединен с выходом счетчика сдвигов, входы первого вентиля подключены к источнику сигнала коррекции, выходу дешифратора коррекции и выходу триггера старшего разряда регистра; входы второго вентиля соединены с выходами первого и третьего вентилей, а выход второго вентиля подсоединен ко входу триггера старшего разряда регистра; входы третьего вентиля соедийены с нулевыми выходами второго триггерпого регистра и с выходом схемы «ИЛИ, входы четвертого вентиля подключены к выходам первого вентиля и схемы «ИЛИ, а выход четвертого вентиля соединен со входом второго

триггера регистра; выходы пятого вентиля нодсоединены к выходу первого вентиля и единичному выходу четвертого триггера регистра, а выход пятого вентиля соединен со входом третьего триггера регистра, входы схемы

«ИЛИ подключены к нулевым выходам третьего и четвертого триггеров регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1974 |

|

SU494744A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1973 |

|

SU517890A1 |

| Счетное устройство | 1984 |

|

SU1210221A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

Даты

1966-01-01—Публикация