Известно оперативное запоминающее устройство (ОЗУ), содержащее разрядную линейку, нодсоединенную к разрядному регистру на параметронах с формирователем тока записи.

Описываемое устройство отличается тем, что для выполнения операций логического сложения и умножения в разрядную линейку введен трансформатор, к трем входным обмоткам которого подключены формирователь тока записи и два дополнительных параметрона, а выходная обмотка подключена к разрядной линейке.

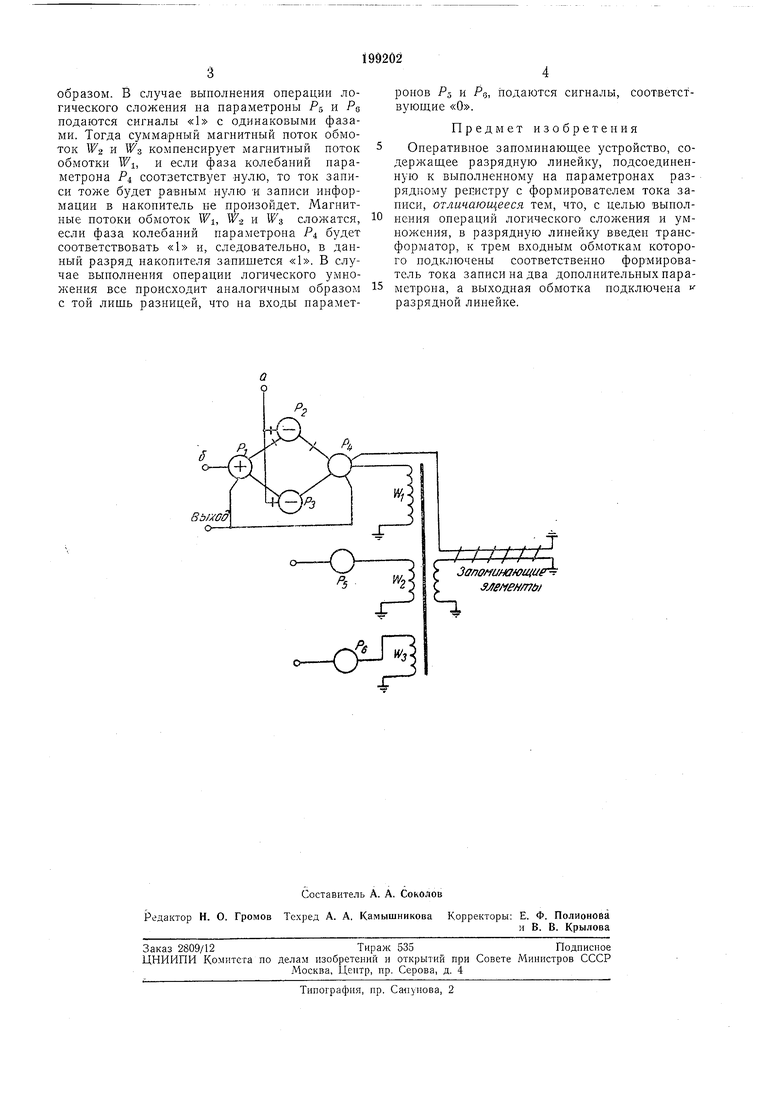

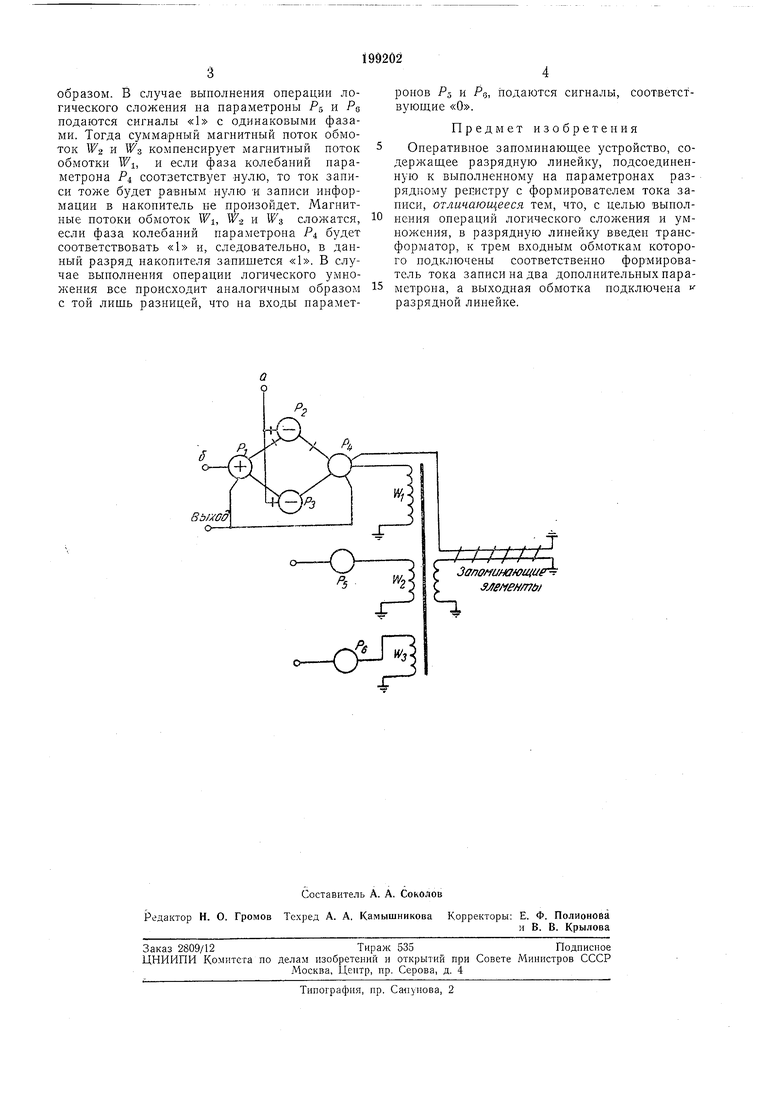

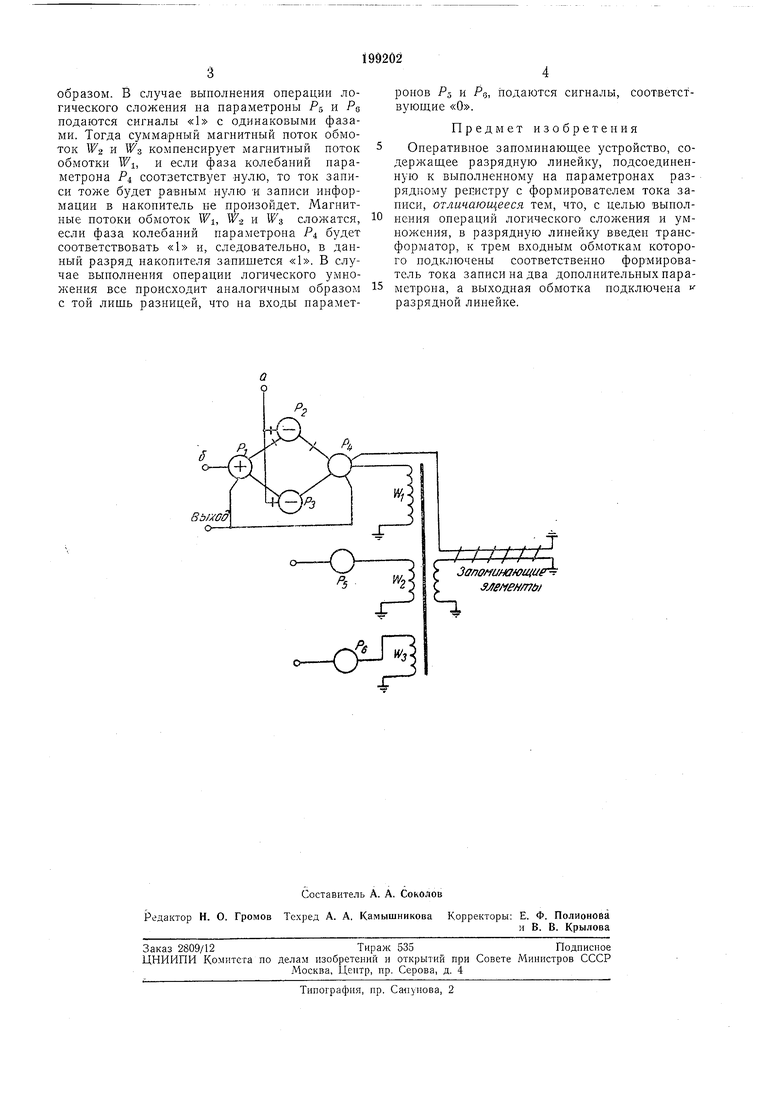

На чертеже изображена функциональная схема одного разряда описываемого устройства.

Параметроны Р, Ра, PS и Р составляют обычную схему разряда регистра числа. Параметрон Pi является как формирователем тока записи, так и усилителем тока чтения. При подаче на вход а сигнала «чтение (единица), на входы параметрона 4 с выхода параметронов Р и РЗ независимо от состояния параметрона PI поступают сигналы противоположных фаз, которые компенсируют друг друга. Таким образом, фаза колебаний параметрона Pi задается фазой сигнала, считанного из накопителя. Если же на вход а подается сигнал «запись (нуль), фаза колебаний параметрона Р определятся фазой сигнала, поступившего на вход б.

Операции логического сложения и логического умножения производятся путем выборки одного из чисел из накопителя и записи его по адресу, который содержит второе число, участвующее в операции. При этом для |ВЫ11олнения операции сложения необходимо, чтобы запись производилась в те разряды накопителя, которым соответствуют разряды регистра числа, содержащие «1. В остальные разряды запись не производится. Для операции умножения запись должна производиться в разряды, которым соответствуют разряды регистра числа, содержащие «О.

Пример. Логическое сложение числа, хранящегося по адресу да (10111001), с числом, хранящимся по адресу а-г (00010111).

ПоСоте чтения числа ,ai и поступления его в числовой регистр производят запись по адресу а-2 способом, указанным выше. Получают число 10111111, которое является результатом ло1 ического сложения чисе.т ai и аз. Таким образом, результат операции сразу оказывается записанным по адресу и-2.

Число витков обмотки Wi равно сумме витков обмоток Wa и Ws, причем Wo- W-j. В нормальном режиме записи и чтения на иараметроны PS и РВ подаются сигналы с противоположными фазами, и вследствие того, что магнитные потоки обмоток W-2 и Ws компенсируют друг друга, ОЗУ работает обычным образом. В случае выполнения операции логического сложения на параметроны Р и PQ подаются сигналы «1 с одинаковыми фазами. Тогда суммарный магнитный поток обмоток W-2 и Wz компенсирует магнитный поток обмотки IFi, и если фаза колебаний параметрона P соотзетствует нулю, то ток записи тоже будет равным нулю и записи информации в накопитель не нроизойдет. Магнитные нотоки обмоток Wi, W.y и Wi, сложатся, если фаза колебаний параметрона Р будет соответствовать «1 и, следовательно, в данный разряд накопителя запишется «1. В случае выполнения операции логического умножения все происходит аналогичным образом с той лишь разницей, что на входы параметронов fs и Ре, подаются сигналы, соответствующие «О. Предмет изобретения Оперативное запоминающее устройство, содержащее разрядную линейку, подсоединенную к выполненному на цараметронах разрядному регистру с формирователем тока записи, отличающееся тем, что, с целью выполнения операций логического сложения и умножения, в разрядную линейку введен трансформатор, к трем входным обмоткам которого подключены соответственно формирователь тока записи на два дополнительных параметрона, а выходная обмотка подключена разрядной линейке.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1974 |

|

SU507899A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| УСТРОЙСТВО для ПАРАЛЛЕЛЬНОГО СУММИРОВАНИЯДВУХ ЧИСЕЛ | 1970 |

|

SU268498A1 |

| Цифровое устройство числового программного управления | 1971 |

|

SU441858A1 |

| ЛОГИЧЕСКОЕ ЗАПОЛНИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU432598A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386444A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| ЦИФРОВОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА ПОЛНОТОЧНОМНАКОПИТЕЛЕ | 1971 |

|

SU289514A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

f-«t-

-i-r-r-r

у / f f r I

Запоминающие 3jre/ieHmt /

Даты

1967-01-01—Публикация