Известные аналого-цифровые преобразователи обобщенного многошкального считывания, в которых используется набор шкал эталонов с одинаковым числом делений ъ каждой из них, построены по замкнутому принципу с преобразователем цифра - аналог в цепи обратной связи. В этих преобразователях код определяется сравнением умноженной на соответствующий коэффициент (равный отношению цены деления грубой шкалы старших разрядов К цене деления данной) разности сигнала и суммы эталонов (получаемой в цепи обратной связи) с эталонами дополнительной шкалы, совпадающей со шкалой старших разрядов. Для этнх целей используются вычитающая схема, схема умножения с переменным коэффициентом (операционный усилитель), дополнительная грубая шкала эталонов, шкала компараторов, где происходит сравнение усиленной разности вычитающей схемы, шифратор результатов сравнения в двоичный код и преобразователь этого кода в сумму эталонов, состоящий из соединенных с суммирующей схемой ключей, коммутируюших в соответствии с кодом эталоны соответствуюших шкал.

триггеры к выходам временного распределителя, соединены каждый с соответствующей суммирующей схемой, а выходы суммирующих схем подключены к компараторам, соединенным с шифратором двоичного кода и, кроме того, через триггеры с дешифратором, подключенным к управляющнм входам ключей, через которые источники эталонных уровней шкал соединены с каждой из суммирующих схем.

Это позволяет повысить точность преобразования и сократить количество оборудования.

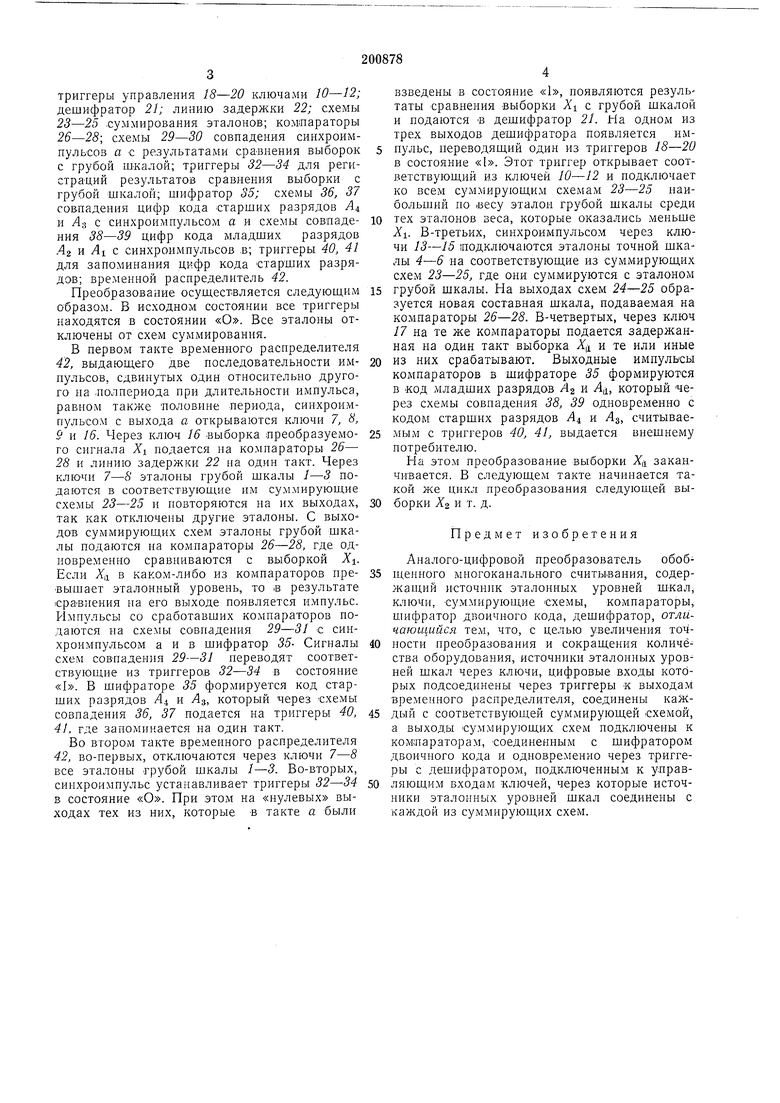

На чертеже приведена блок-схема четырехразрядного преобразователя с обратной связью.

Он имеет две шкалы, в каждой из которых три деления. С помощью грубой шкалы измеряется весь диапазон преобразования. Цена деления этой шкалы составляет V-i диапазона изменения входного сигнала и равна диапазону измерений точной щкалы. Цена деления точной щкалы равна Д цены деления грубой щкалы и 1/10 диапазона изменения входного сигнала.

Преобразователь содержит источники эталонных уровней шкал (напряжений или токов) : грубую шкалу 1-3, точную шкалу 4- 6; ключи для коммутации эталонов грубой щкалы 7-9 и 10-12, точной - 13-/5; ключн 16, 17 для коммутации входного сигнала;

триггеры управления 18-20 ключами 10-12; дешифратор 21; лииию задержки 22; схемы 23-25 .суммирования эталонов; компараторы 26-28; схемы 29-30 совпадения синхроимпульсов а с результатами сра внения выборок с грубой шкалой; триггеры 32-34 для регистрации результатов сравнения выборки с грубой шкалой; шифратор «35; схемы 36, 37 совнадения цифр кода старших разрядов А и AZ с синхроимпульсом а и схемы совпадения 38-39 цифр кода младших разрядов Лз и Лх с синхроимпульсов ,в; триггеры 40, 41 для запоминания цифр кода старших разрядов; вре.менной распределитель 42.

Преобразование осуш,ествляется следующим образом. В исходном состоянии все триггеры находятся в состоянии «О. Все эталоны отключены от схем суммирования.

В нервом такте временного распределителя 42, выдающего две последовательности имнульсов, сдвинутых один относительно другого на лолпериода нри длительности импульса, равном также ноловине периода, синхроимпульсом с выхода а. открываются ключи 7, 8, 9 и 16. Через ключ 16 выборка преобразуемого сигнала Х подается на компараторы 26- 28 и линию задержки 22 на один такт. Через ключи 7-6 эталоны грубой шкалы 1-3 подаются в соответствующие им суммирующие схемы 23-25 и повторяются на их выходах, так как отключены другие эталоны. С выходов суммирующих схем эталоны грубой шкалы подаются на комнараторы 26-28, где одновременно сравниваются с выборкой i. Если 1 в каком-либо из компараторов превышает эталонный уровень, то .в результате сравнения на его выходе появляется импульс. Импульсы со сработавших компараторов подаются на схемы совпадения 29-31 с синхроимпульсом айв шифратор 35- Сигналы схем совнадения 29-31 переводят соответствуюшие из триггеров 32-34 в состояние «I. В шифраторе 35 формируется код старших разрядов А и AS, который через схемы совпадения 36, 37 подается на триггеры 40,

41,где запоминается на один такт.

Во втором такте временного распределителя

42,во-первых, отключаются через ключи 7-8 все эталоны грубой шкалы /-3. Во-вторых, синхроимпульс устанавливает триггеры 32-34 в состояние «О. При этом на «нулевых выходах тех из них, которые в такте а были

взведены в состояние «1, появляются результаты сравнения выборки Al с грубой шкалой и подаются в дешифратор 21. На одном из трех выходов дешифратора появляется имнульс, нереводящий один из триггеров /5-20 в состояние «I. Этот триггер открывает соответствующий из ключей 10-12 и нодключает ко всем суммирующим схемам 23-25 наибольший но весу эталон грубой шкалы среди

тех эталонов веса, которые оказались меньше Xi. В-третьих, синхроимпульсом через ключи 13-15 подключаются эталоны точной шкалы 4-6 на соответствующие из суммирующих схем 23-25, где они суммируются с эталоном

грубой шкалы. На выходах схем 24-25 образуется новая составная шкала, подаваемая на компараторы 26-28. В-четвертых, через ключ 17 на те же компараторы подается задержанная на один такт выборка Х и те или иные

из них срабатывают. Выходные импульсы компараторов в шифраторе 35 формируются в код младших разрядов А и Л, который через схемы совпадения 38, 39 одновременно с кодом старших разрядов AI и Лз, считываемым с триггеров 40, 41, выдается внешнему потребителю.

На этом преобразование выборки Х, заканчивается. В следующем такте начинается такой же цикл преобразования следующей выборки Xs и т. д.

Предмет изобретения

Аналого-цифровой преобразователь обобщенного многоканального считывания, содержаищи источник эталонных уровней шкал, ключи, суммирующие схемы, компараторы, шифратор двоичного кода, дешифратор, отличающийся тем, что, с целью увеличения точности преобразования и сокращения количества оборудования, источники эталонных уровней шкал через ключи, цифровые входы которых подсоединены через триггеры к выходам временного распределителя, соединены каЖдый с соответствующей суммирующей схемой, а выходы суммирующих схем подключены к комэтараторам, соединенным с шифратором двоичного кода и одновременно через триггеры с дешифратором, подключенным к управляющим входам ключей, через которые источники эталонных уровней шкал соединены с каждой из суммирующих схем.

Ли Л А,

/

I Г

л Т71 ПТ1 рШ

1 «/7 /// гт п

71 WrillJ-b

.-j-i..

т

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1973 |

|

SU711676A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1102033A1 |

| Многоканальный аналого-цифровой преобразователь | 1977 |

|

SU726664A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU1117835A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| Параллельно-последовательный преобразователь напряжения в код | 1982 |

|

SU1039027A2 |

| Устройство для преобразования координат | 1980 |

|

SU898426A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Цифровой фазометр | 1985 |

|

SU1298687A2 |

Даты

1967-01-01—Публикация