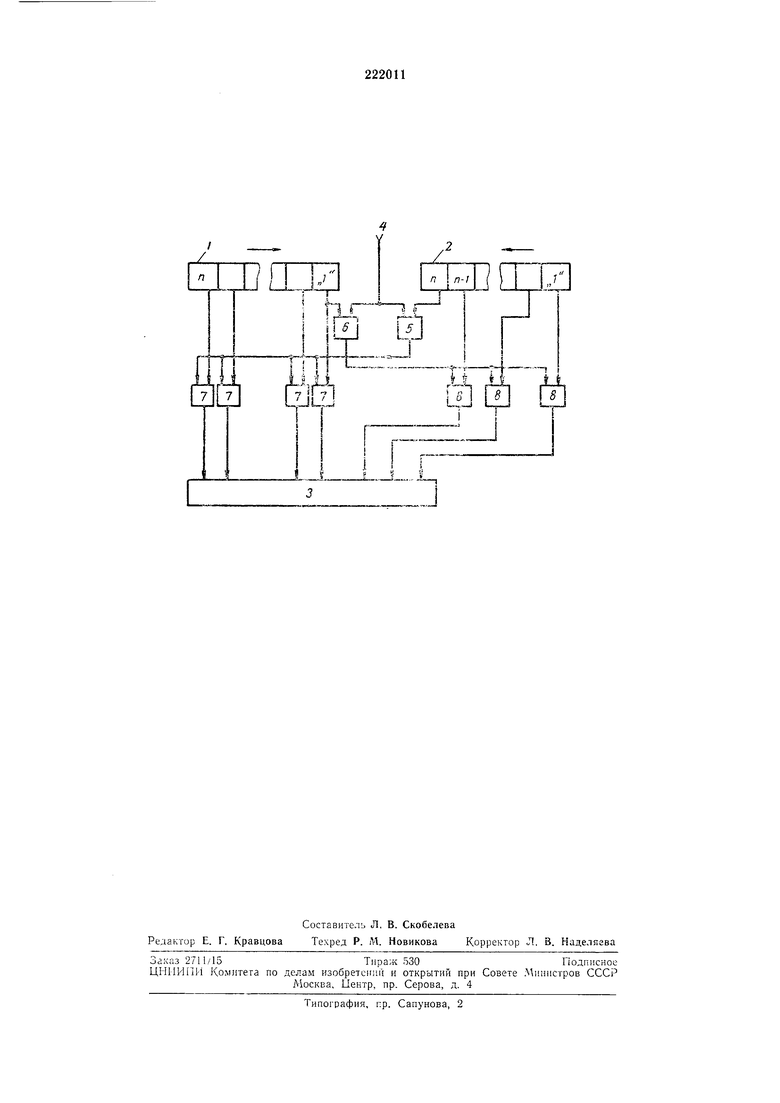

Известны устройсгва для умножения двух «-разрядных чисел, содержащие регистры множимого и множителя с цепями сдвига, схемы сов иадения и 2л-разрядный параллельный сумматор. Предложенное устройство отличается от известных тем, что первые входы схем совпадений, формирующих младшие разряды частичных произведений, подключены к единичным выходам всех разрядов регистра множителя, кроме cTapinero разряда, вторые входы этих схем совпадений объединены и связаны с единичным выходом младшего разряда регистра множимого через схему совпадения, второй вход кото-рой подключен К щнне тактовых ИМпульсов. Такое соединение позволит упростить конструкцию устройства и повысить его надежность. На чертеже представлена структурная схема предлагаемого устройства. Схема содержит 1 - я-разрядный регистр множимого с цепями сдвига кода на один разряд вправо, 2-л-разрядный регистр множителя с цепями сдвига кода на один разряд влево, 3-2п-разрядный параллельный двоичный сумматор, 4-цепь выдачи (из узла управлення) такговых импульсов передачи частичного произведения в сумматор 3, 5 -схему совпадений, один вход которой подключен к единичному выходу триггера старшего разряда регистра 2, а другой - к цепи 4, 6 - схему совпадений, один вход которой подключен к единичному выходу триггера младшего разряда регистра 1, а другой - к цепи 4, 7 - п.-схем совпадений, первые входы которых подключены к единичным выходам триггеров всех разрядов регистра /, вторые входы - к выходу схемы совпаденпй 5, а выходы схем совпадений - к входам старшнх разрядов (от п-го до 2п - 1-го) сумматора 3, 8п - 1 схем совпадений, первые входы которых подключены к единичным выходам триггеров всех разрядов регистра 2 (кроме самого старшего), все вторые входы - к выходу схемы совпадений 6, а выходы этих схем совпадений - к входам младших (от 1-го до п-1-го) разрядов сумматора 3. Устройство работает следующим образом. После введення в регистры / и 2 кодов сомножителей при поступлении но цепи 4 тактового импульса выполняется передача кода регистра / в старшие разряды сумматора 3, если в старшем разряде регистра 2 записана «1 и нередача кода регистра 2 (кроме самого старшего разряда) в младшие разряды сумматора, если в младшем разряде регистра / записана «1. Во время выполнения суммирования в сумматоре 3, осуществляются сдвиги кода (в регистре / - на один разряд вправо а в регистре 2 - на один разряд влево). При этом в старшем разряде регистра 1 и младшем разряде регистра 2 устанавливаются «нули. Далее ири приходе ио цепи 4 следующих тактовых импульсов описанные операции повторяются либо до тех пор, иока хотя бы в одном из регистров / и 2 не окажется код, состоящий из одних «нулей, либо п раз.

Поскольку после каждого сдвига в регистрах / и 2 в оставшихся в них кодах устанавливается обязательно по одному «нулю, которые йотом «продвигаются ио этим регистрам, то максимально возможное число «единиц в коде у каждого последующему частичного произведения окажется на два меньше, чем у предыдущего.

Объяснение действия устройства основано на замене иснользуемого в известных устройствах «ромба (получаемого при ъыткыъгимл всех частичных произведений, образуемых в каждом такте, без их суммирования, но с учетом их сдвигов) эквивалентным ему с точки зрения результата «треугольником.

Пусть, например, осуществляется умножение двух четырехразрядных двоичных чисел ABCD (множимое) и abed (множитель).

Тогда для известных устройств с направлениями сдвигов в регистрах мнол имого и множителя, одинаковыми с показанными на чертелхе, «ромб имеет вид:

Такты

1Аа Ва Са Da

2Ab Bb Cb

Db

3Ac Be

DC Cd Cc Bd

4Ad

Dd

предлагаемого устройDa Db DC Dd

Cb Cc Cd

Ac

Be Ad

3 4

Bd

Следует отметить, что в результате сим.метрни «треугольника относительно его среднего столбца фактически безразлично, который пз регистров 7 и 2 (см. чертеж) считать региетром множимого и который регистром множителя, при условии, что старшие п разрядов частичных ироизведений формиру отся схемами совпадений, подключенными к тому регистру, у которого предусмотрены цепи сдвига кода вправо, а младщие п-/ разрядов частичных произведен формиру отся с. совпадений, нодкл очеиными к разрядам (кро:vie самого старшего) того регистра, у которого предус.мотреиы пели сдвига кода влево.

Если осуществляется умно:Кение двух л-разрядиых чисел с округлением нронзведоиия до п значащих цифр, то предлагаемое )ттройство упрощается иуто 1сключення излишиих п-/с разрядов сумматора 3 и п-к схем совпадений 5, формируюш,их самые ладщие разряды чаетичных произведений.

Предмет и з о б р е т е i и я

Устройство для умнол-сення двух л-разрядных чисел, содержащее регистры множ:имо -о и множителя с цепям сдвига, со знаде1 ия и 2л-разрядный параллельный сумматор, отличающееся тем, что, с целью иовышения надежное и и упрощения ко струкции, первые ВХОДЫ схем совиаден Й, ладшие разряды частичных ироизвсде ий, подкл очены к единичным Г5ыходам всех разрядов регистра множителя, кроме старшего разряда, вторые входы этих схем совпадений объединены и связаны с единичным выходом младшего разряда регистра множимого через схему совпадения, второй вход которой подключен к uimiQ тактовых им ульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения @ - разрядных чисел | 1989 |

|

SU1735843A1 |

Даты

1968-01-01—Публикация