Известны устройства памяти приращений цифрового дифференциального анализатора (ЦДЛ), реализуюпдего уточненный метод трапеций и содержащего кольцевые регистры хранения приращений.

Предлагаемое устройство отличается от известных тем, что оно содержит схему запрета, включенную в цепь, соединяющую предпоследнюю ячейку первого регистра со входами первого и второго регистра. Это упрощает устройство.

Кодирование в регистре приращений можно организовать следующим образом:

.+ 1 - .+

Тогда знак нулевого значения может нести информацию о знаке предыдущего ненулевого приращения. Технически задача состоит в том, чтобы устройство управления вводом и выводом приращений в регистрах приращений осуществляло, помимо своих обычных функций преобразование запоминаемых кодов при поступлении очередных нулевых переполнений. Этн преобразования не должны нарушать обычных функций регистров и в то же время обеспечивать хранение знака последнего ненулевого переполнения на несколько итераций,

пока не придет новое переполнение, не равное, нулю.

Для решения этой задачи предлагается ввести дополнительную обратную связь с выхода «отрицательного регистра (регистр, г. котором запоминается второй разряд переполнения) на выходы обоих регистров. Обычно каждый из регистров приращений замкнут в кольцо обратной связью с выхода последнего элемента на вход первого. Последний элемент имеет цепь возвращения Б первоначальное состояние, на которую подаются импульсы очистки перед поступлением переполнений с выхода каждого интегратора. Дополннтельную обратную связь предлагается подключать с предпоследнего элемента регистра (без очистки) через фазирующие элементы задержки на входы обоих регистров. Эта обратная связь отключается с помощью специальных цепей

запрета при поступлении хотя бы одного импульса с выхода интегратора или с последних элементов регистра приращений, когда кет импульсов очистки. Такого рода обратная связь обеспечивает следующее преобразование

кодов в регистрах приращений при поступлении с выхода интегратора нулевого переполпения:

Поскольку обратная связь охватывает элементы очистки регистра приращений, то при поступлепии нулевых переполнений коды 00 и И могут храниться в регистре неограниченно большое число итераций. В то же время, использование в выходных элементах операции «исключенного ИЛИ с одинаковых разрядов регистра при выборке приращений из регистра обеспечивает независимость кодов 00, 01, 10 (тернарной системы кодирования переполнений) от вновь введенного значения 11 (кзатернгрной системы кодирования приращений).

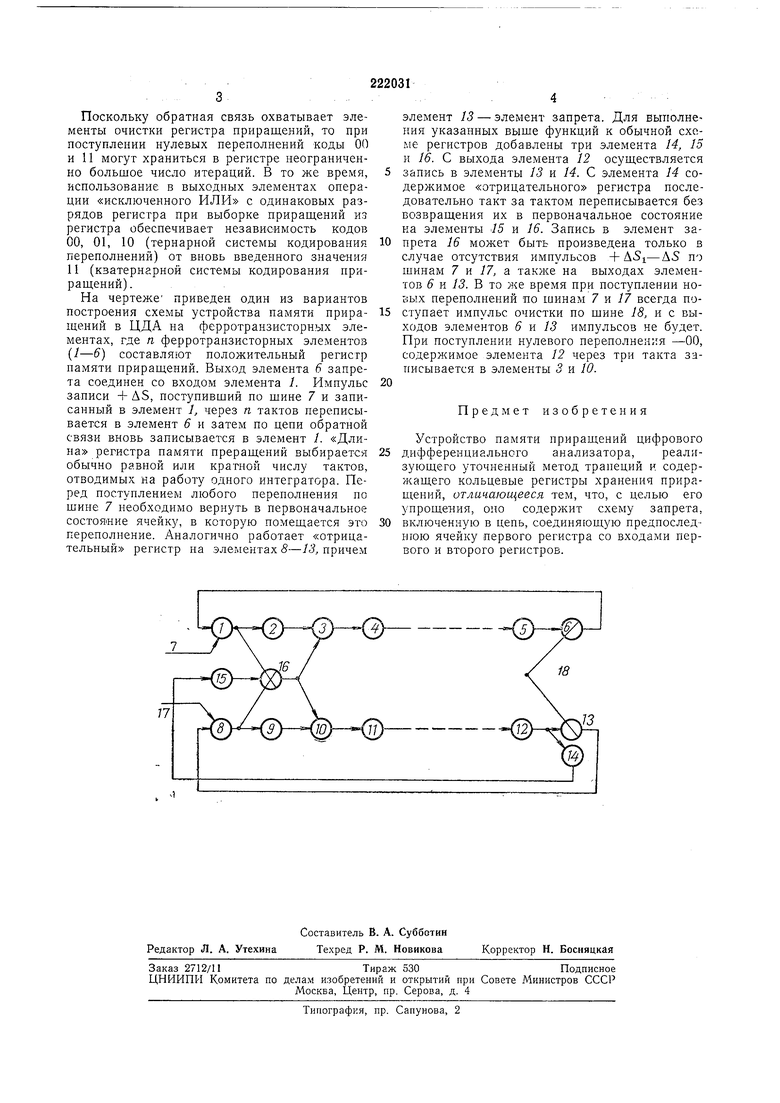

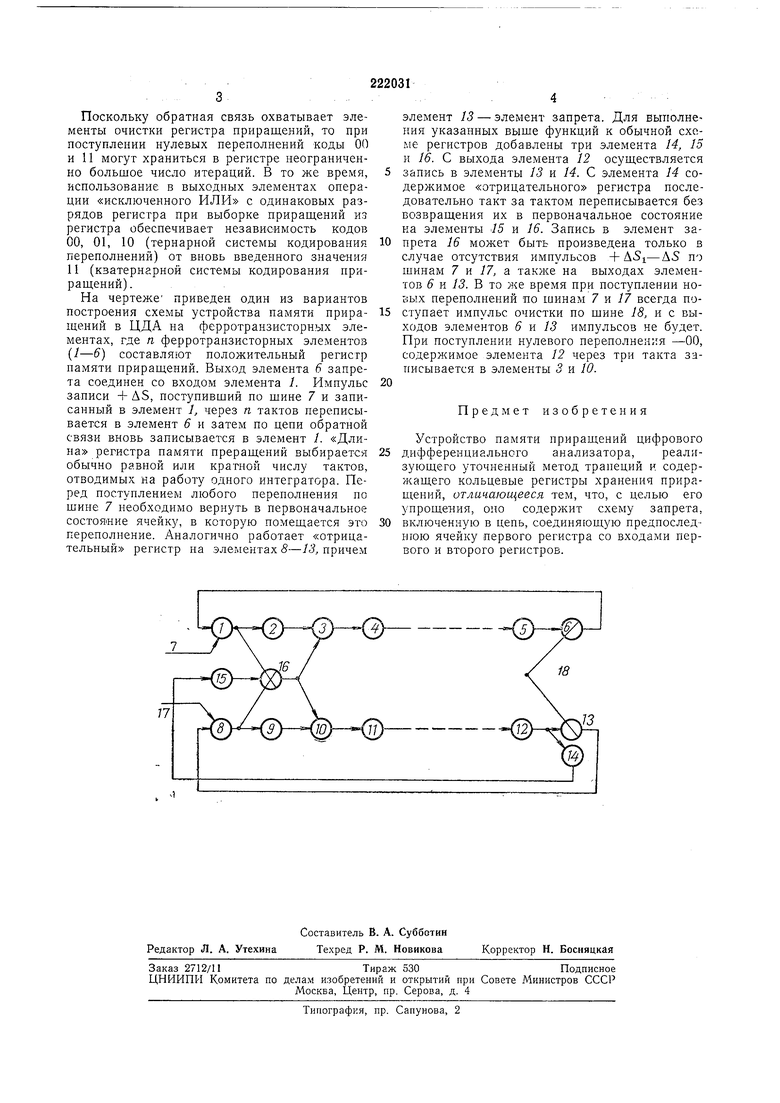

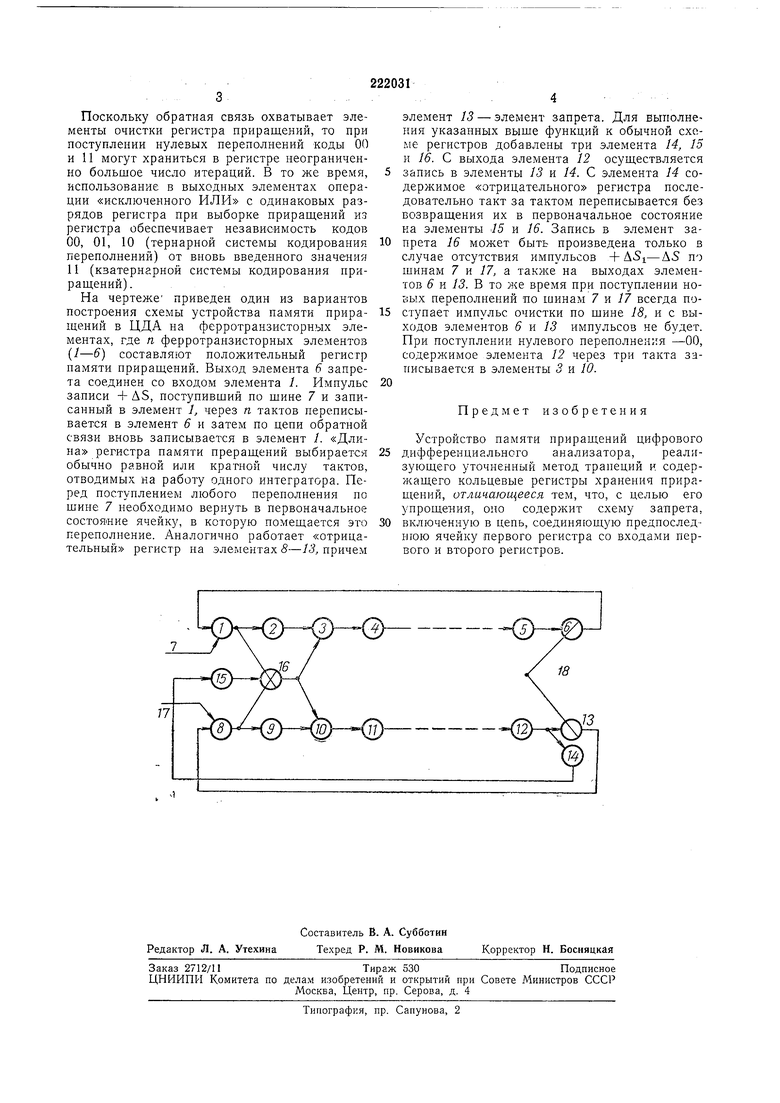

На чертеже приведен один из вариантов построения схемы устройства памяти приращений в ЦДЛ на ферротранзисторных элементах, где п ферротранзисторных элементов (/-6) составляют положительный регистр памяти приращений. Выход элемента 6 запрета соединен со входом элемента /. Импульс записи + Д5, поступивший по шине 7 и записанный в элемент 1, через п тактов переписывается в элемент 6 и затем по цепи обратной связи вновь записывается в элемент /. «Длина регистра памяти преращений выбирается обычно равной или кратной числу тактов, отводимых на работу одного интегратора. Перед поступлением любого переполнения по шине 7 необходимо вернуть в первоначальное состояние ячейку, в которую помещается это переполнение. Аналогично работает «отрицательный регистр на элементах 8-13, причем

элемент 13 - элемент запрета. Для вытюлнения указанных выше функций к обычной схеме регистров добавлены три элемента 14, 15 и 16. С выхода элемента 12 осуществляется

запись в элементы 13 и 14. С элемента 14 содержимое «отрицательного регистра последовательно такт за тактом переписывается без возвращения их в первоначальное состояние на элементы 75 и 16. Запись в элемент запрета 16 может быть произведена только в случае отсутствия импульсов + A5i-Л5 по шинам 7 и /7, а также на выходах элементов 6 н 13. В то же время при поступлении новых переполнений по щинам 7 я 17 всегда поступает импульс очистки по щине 18, и с выходов элементов 6 v. 13 импульсов не будет. При поступлении нулевого переполнения -00, содержимое элемента 12 через три такта записывается в элементы 3 и 10.

Предмет изобретения

Устройство памяти приращений цифрового дифференциального анализатора, реализующего уточненный метод трапеций и содержащего кольцевые регистры хранения приращений, отличающееся тем, что, с целью его упрощения, оно содержит схему запрета, включенную в цепь, соединяющую предпоследнюю ячейку первого регистра со входами первого и второго регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕПРЕРЫВНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1969 |

|

SU241121A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| ВСЕСОЮСЛЛЛ , HATwiiTIiO - <3>& iтг;:;и(«{?сг:! |•^U'iEKA I | 1964 |

|

SU164487A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК | 1967 |

|

SU206169A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1972 |

|

SU415676A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

Даты

1968-01-01—Публикация