Известные непрерывные цифровые интеграторы, выполиениые па ферротранзнсторпых элементах, содержат регистр подынтегральной функции, делитель частоты и кольцевой сдвигающий регистр, обеспечивающий сиихронизацию работы устройства.

Предлагаемый цифровой интегратор отличается от известных тем, что он содержит матричпо-диагональпо расположенные триггеры, соединенные с регистром подынтегральиой функции и делителем частоты. Такое выполпение устройства позволяет повысить его быстродействие.

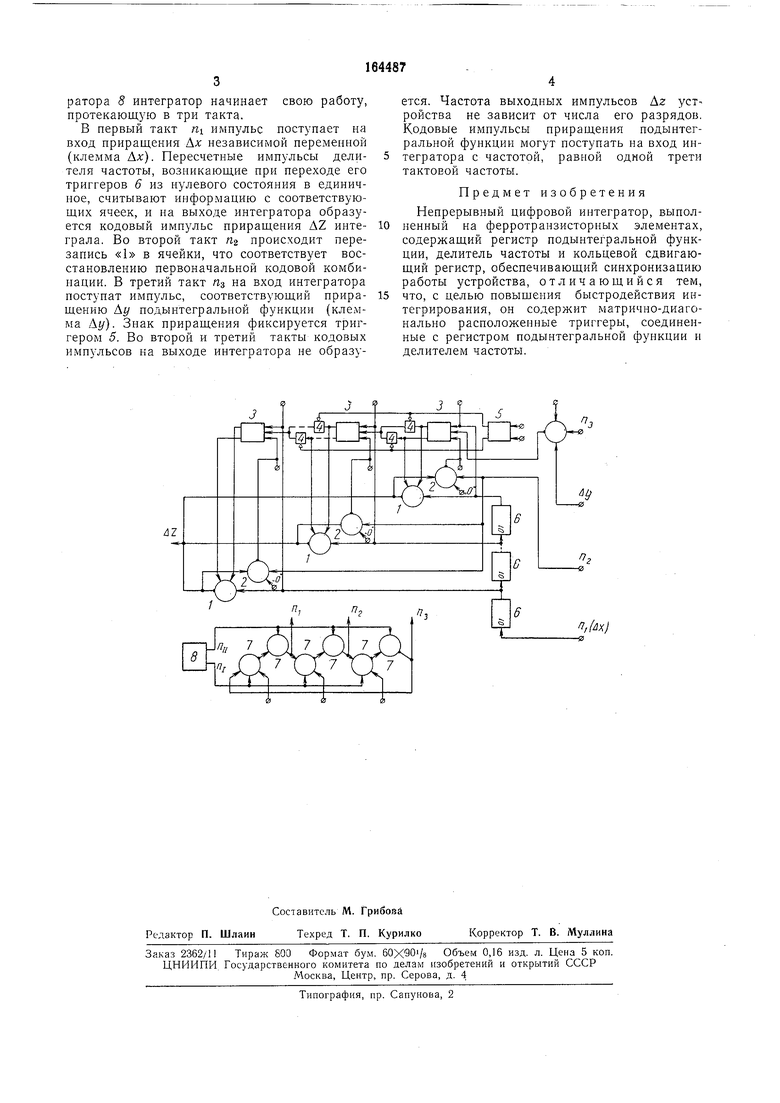

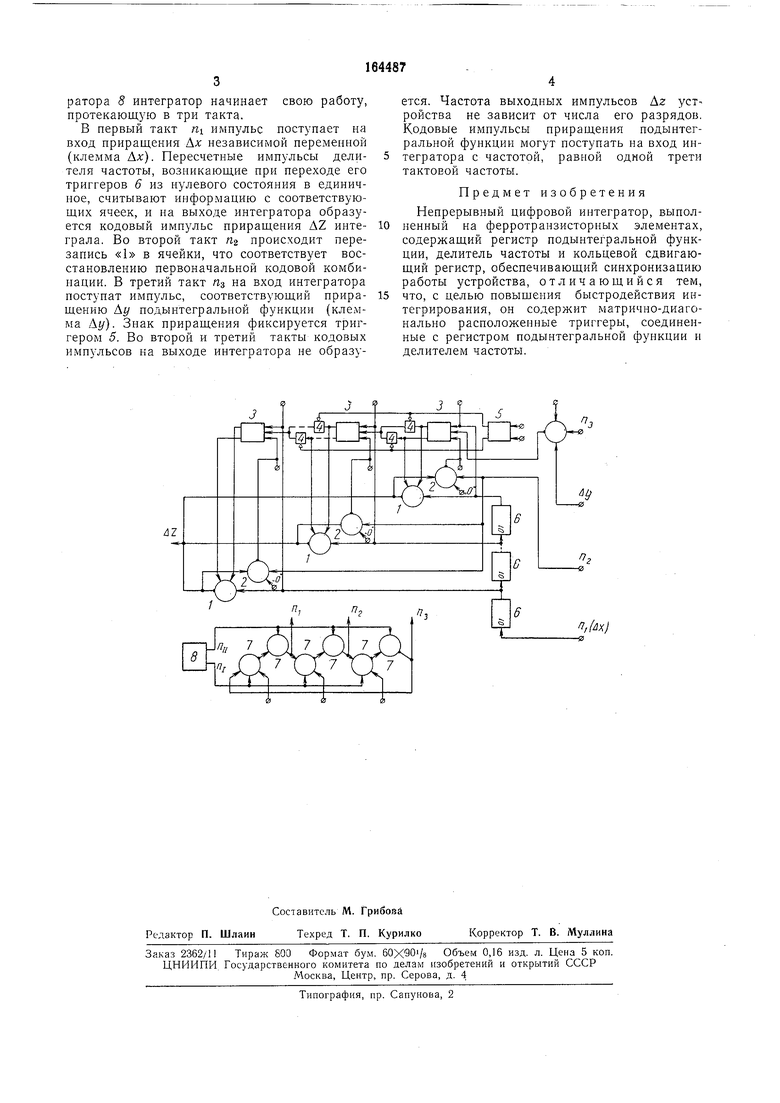

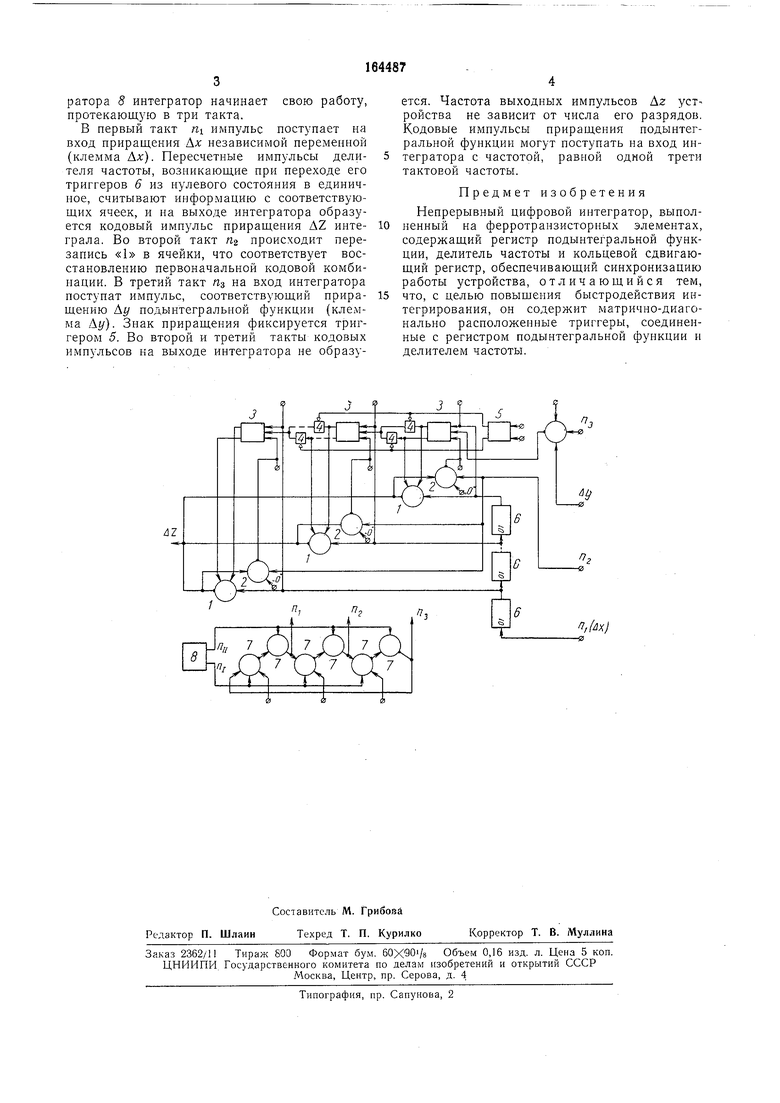

На чертеже изображена фуикциопальпая схема пепрерывпого цифрового 1П1тегратора.

Основная часть интегратора содержит к матричио-диагональио расположенных динамических триггеров (к - число двоичпых разрядов регистра нодыптегральной функции), состоящих из ферротранзистор1Нз1х ячеек / и 2 и статическнх триггеров 3. Регнстром подыптегралыюй фуикцни является реверсивный двоичиый счетчик, состоящий из к последовательио еоедипеииых друг с другом ферротранзисториых статических триггеров 3.

Поступающая па вход счетчнка информация в виде единичных ндгаульсов фиксируется в нем в виде нормального двоичного кода. Счетчик управляется, с помощью логических элементов 4 «И. Переключение с одного режима работы (суммироваипя) на другой (вычитапие) производится посредством триггера 5, собранного по обычной полупроводниковой схеме па транзпсторах. Коллекторный ток этих транзисторов подмагничивает ферротранзисторные ячейки логических элементов «И. Подмагпичивание является необходимым условием работы устройства. Па вход дииамических триггеров (диагональный ряд ферротранзисторных ячеек) поступают тактовые импульсы от делителя частоты, состоящего из к триггеров 6. Сиихронизация работы всего устройства производится с помощью кольцевого сдвигающего регистра, собранного на транзнстор1Н 1х ячейках 7, который управляется двухтактным генератором 8 импульсов.

Перед иачалом работы интегратора соответствующне ферротранзнсторные ячейки устанавлнвают в нулевое состоянне, подавая имнульсы па клеммы «О.

Затем в регпстр подынтегральной фупкции, собраиньи иа триггерах 5, вводится нараллельным двоичным кодом начальное значение подынтегральной функции (клеммы «О, «1). При этом един1ща записывается в соответствующие ячейки д1Н ампческих триггеров. Первая слева ячейка / сдвигающего регистра устанавливается в еднничное состояние (клемма «1). С зануеком двухтактного генератора 8 интегратор начинает свою работу, протекающую в три такта,

В первый такт п. импульс поступает на вход приращения Ал: независимой переменной (клемма Лл:). Пересчетиые импульсы делителя частоты, возникающие при переходе его триггеров 6 из нулевого состояния в единичное, считывают информацию с соответствующих ячеек, и на выходе интегратора образуется кодовый импульс приращения AZ интеграла. Во второй такт Пг происходит перезапись «1 в ячейки, что соответствует восстановлению первоначальной кодовой комбинации. В третий такт «з на вход интегратора поступат импульс, соответствующий приращению Ау подынтегральной функции (клемма Аг/). Знак приращения фиксируется триггером 5. Во второй и третий такты кодовых импульсов на выходе интегратора не образуется. Частота выходных импульсов Аг устройства не зависит от числа его разрядов. Кодовые импульсы приращения подынтегральной функции могут поступать на вход интегратора с частотой, равной одной трети тактовой частоты.

Предмет изобретения

Непрерывный цифровой интегратор, выполненный на ферротранзисторных элементах, содержащий регистр подынтегральной функции, делитель частоты и кольцевой сдвигающий регистр, обеспечивающий синхронизацию работы устройства, отличающийся тем, что, с целью повышения быстродействия интегрирования, он содержит матрично-диагонально расположенные триггеры, соединенные с регистром подынтегральной функции и делителем частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕПРЕРЫВНЫЙ ЦИФРОВОЙ ИНТЕГРАТОР | 1969 |

|

SU241121A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ УСТОЙЧИВОСТИ ФАЗИРУЮЩИХ УСТРОЙСТВ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ | 1968 |

|

SU211151A1 |

| Цифро-частотный интегратор | 1979 |

|

SU935955A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Устройство для деления частоты пов-ТОРЕНия иМпульСОВ | 1979 |

|

SU817891A1 |

| Круговой интерполятор для контурных систем программного управления станками | 1973 |

|

SU484502A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1968 |

|

SU219911A1 |

| Устройство задания скорости в системах числового программного управления | 1984 |

|

SU1211695A1 |

Даты

1964-01-01—Публикация