Изобретение относится к вычислительной технике и может быть использовано при автоматическом контроле микропроцессорных устройств.

Целью изобретения является повышение полноты тестов за счет формирования многосвязных последовательностей кодов микротестов.

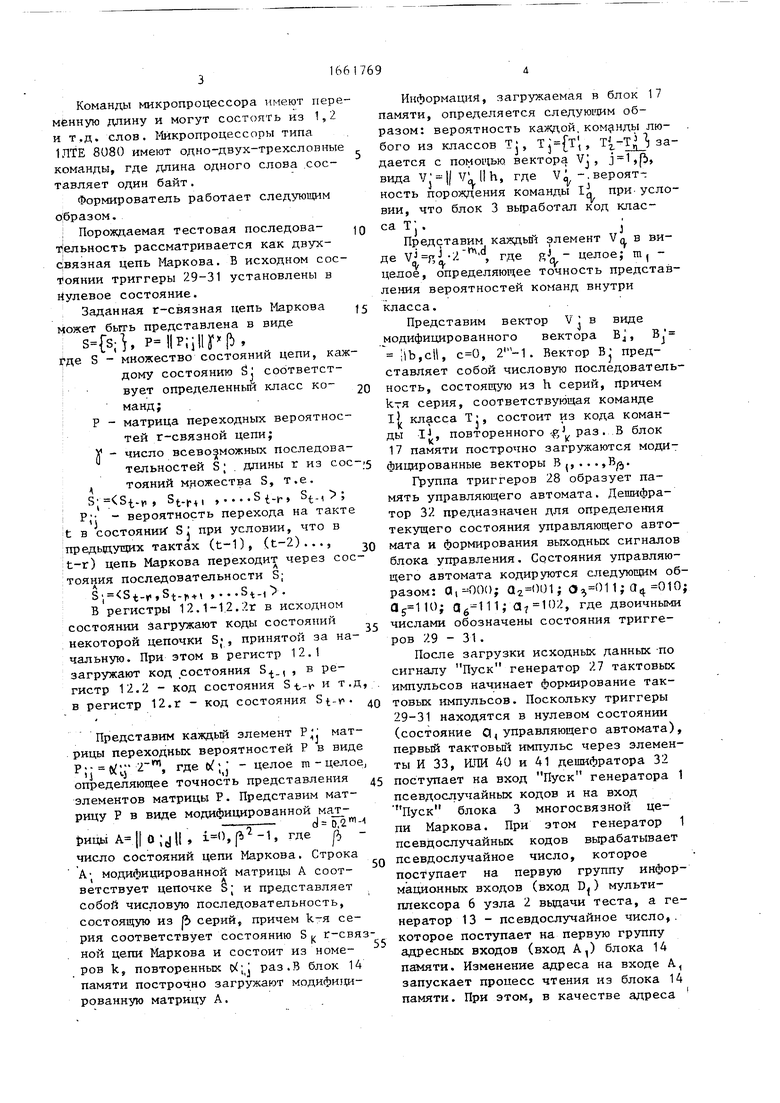

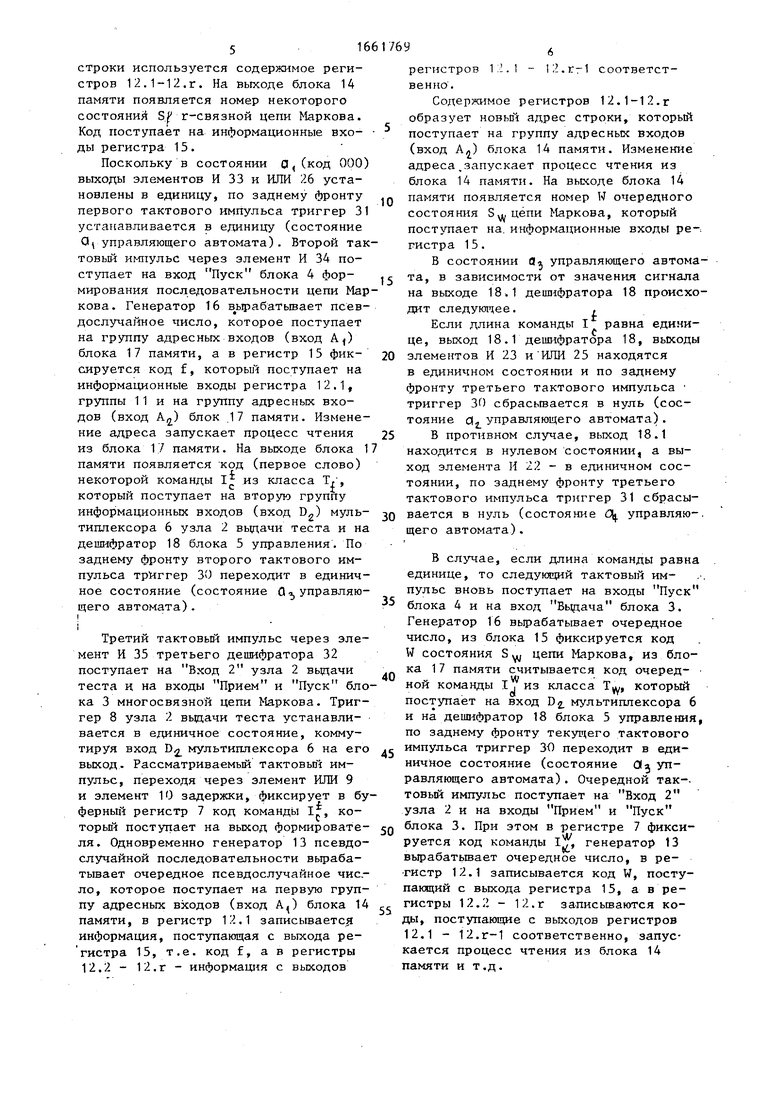

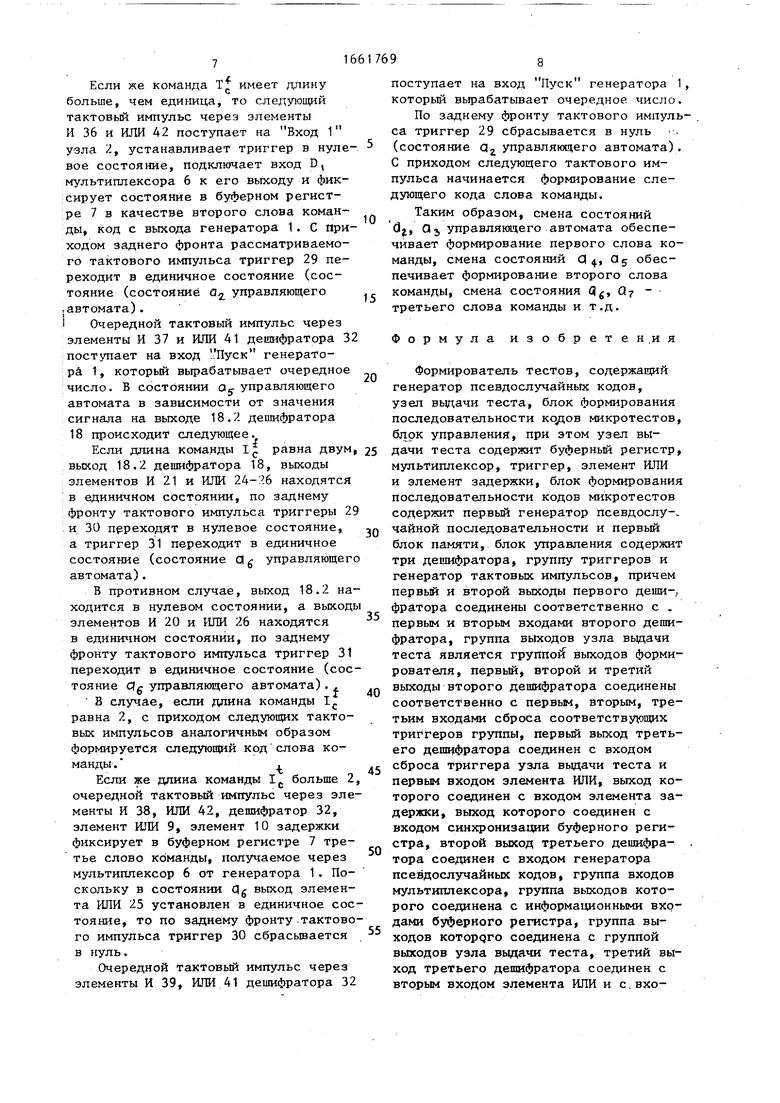

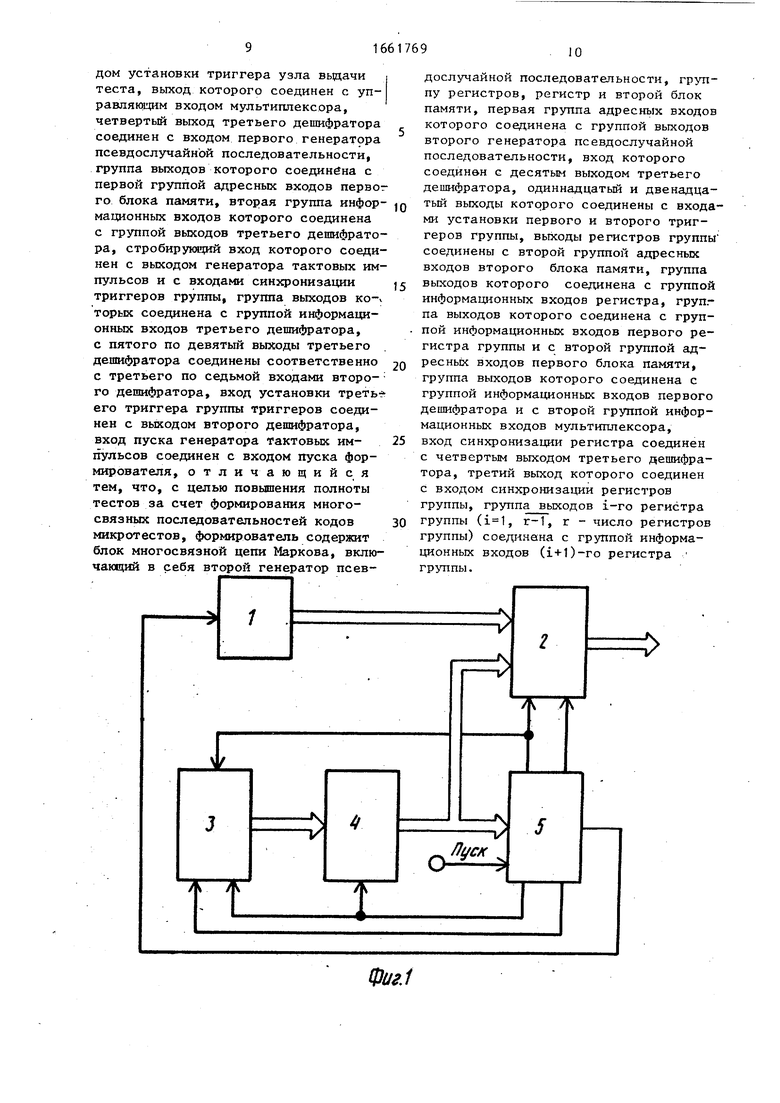

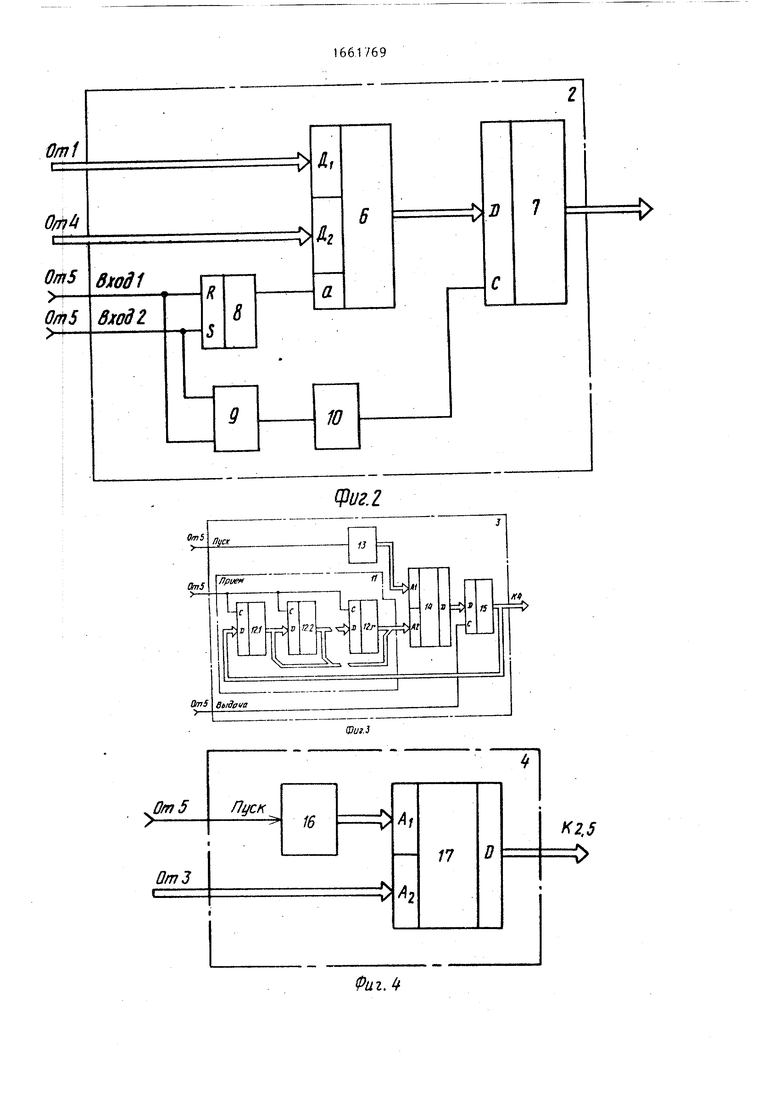

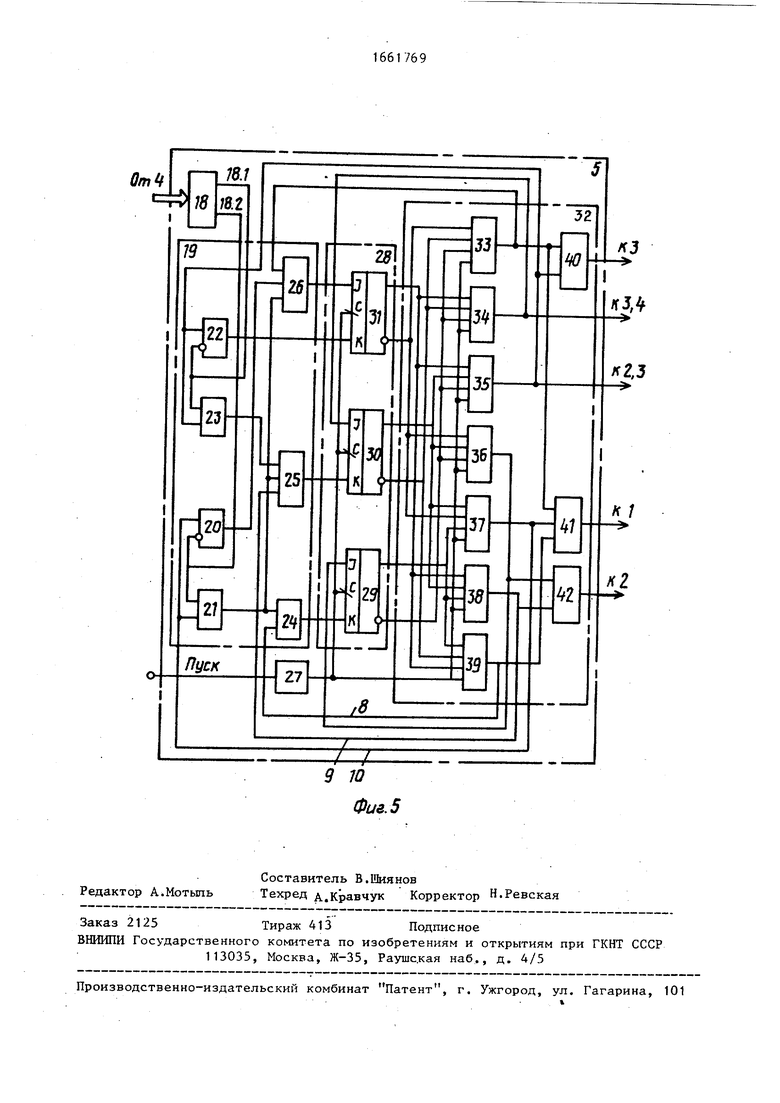

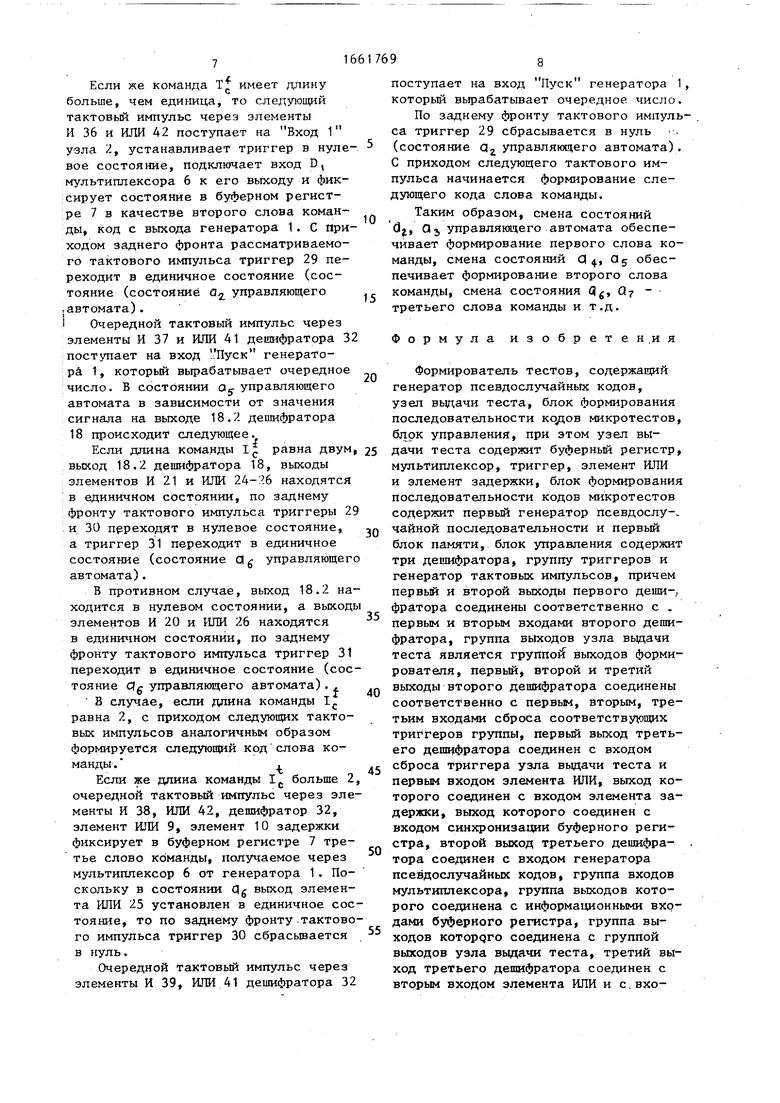

На фиг. 1 представлена структурная схема формирователя; на фиг. 2 - схема узла выдачи теста; на фиг.З - схема блока многосвязной цепи Маркова; на фиг. 4 - схема блока формирования последовательности кодов микротестов; на фиг. 5 - схема блока управления .

Формирователь тестов (фиг. 1) содержит генератор 1 псевдослучайных кодов, узел 2 выдачи теста, блок 3 многосвязной цепи Маркова, блок 4 формирования последовательности кодов микротестов, блок 5 управления.

Узел 2 выдачи теста (фиг. 2) содержит мультиплексор 6, буферный регистр 7, триггер 8, элемент ИЛИ 9 и . элемент 10 задержки.

Блок 3 многосвязанон цепи Маркова (фиг. 3) содержит группу регистров 11, образованную регистрами 12.1-12.2r, где г - связность цепи Маркова, генератор 13 псевдослучайной последовательности, блок 14 памяти, регистр 15.

Блок 4 формирования последовательности кодов микротестов (фиг. 4) содержит генератор 16 псевдослучайной последовательности и блок 17 памяти.

Блок 5 управления (фиг. 5) содержит первый дешифратор 18, второй дешифратор 19, образованный элементами И 20-23 и элементами ЯТИ 24-26, генератор 27 тактовых импульсов, группу триггеров 28, образованной триггерами 29-31, третий дешифратор 32, образованный элементами И 33-39 и элементами ИЛИ 40-4 .

Для пояснения работы формирователь тестов воспользуется следующей структурой команд микропроцессора.

(Л

С5 05

j

ОЭ

со

Команды микропроцессора имеют переменную длину и могут состоять из 1,2 и т.д. слов. Микропроцессоры типа 1ЛТЕ 8U80 имеют одно-двух-трехслонные команды, где длина одного слова составляет один байт.

Формирователь работает следующим образом.

, Порождаемая тестовая последова- т ельность рассматривается как двухсвязная цепь Маркова. В исходном состоянии триггеры 29-31 установлены в нулевое состояние.

Заданная r-связная цепь Маркова может быть представлена в виде

, p ||p;illpp,

где S - множество состояний цепи, каждому состоянию S; соответствует определенный класс ко- манд;

Р - матрица переходных вероятностей r-связной цепи; У - число всевозможных последовательностей S; длины г из сос, тояний множества S, т.е.

, st.f+, , ....St-r st-i

P;- - вероятность перехода на такте t в состоянии S; при условии, что в предыдущих тактах (t-1), (t-2) ..., t-r) цепь Маркова переходит через состояния последовательности S;

S ( t S.f, + ( ,...St-1 .

В регистры 12.1-12.2r в исходном состоянии загружают коды состояний некоторой цепочки Sj, принятой за начальную. При этом в регистр 12.1 загружают код состояния St, , в регистр 12.2 - код состояния S-t-r и т.д в регистр 12.г - код состояния .

Представим каждый элемент матрицы переходных вероятностей Р в виде рч 1Г Ј , где . - целое то - целое определяющее точность представления элементов матрицы Р. Представим матрицу Р в виде модифицированной .2wu 1

рицы А-|| OJjll , , (42-1, где ft - число состояний цепи Маркова. Строка А ( модифицированной матрицы А соответствует цепочке Ј; и представляет собой числовую последовательность, состоящую из | серий, причем k-я серия соответствует состоянию S г-связ ной цепи Маркова и состоит из номе- ров k, повторенных Ы;1 раз.В блок 14 памяти построчно загружают модифицированную матрицу А.

Информации, загружаемая в блок 17 памяти, определяется следующим образом: вероятность каждой, команды любого из классов Т:, , , ) задается с помощью вектора VI, j , вида V jj V II h, где V -.вероятность порождения команды li при-условии, что блок 3 выработал код класса т;

) J

Представим каждый элемент Va ,,; i ., -it,H 1 . /. . гле pJ - пе.ппе:

в виде ,(1, где целое;Тт, - целое, определяющее точность представления вероятностей команд внутри класса.

Представим вектор V в виде модифицированного вектора BJ, В llbjcil, , . Вектор В: представляет собой числовую последовательность, состоящую из h серий, причем я серия, соответствующая команде Т.. класса Т-, состоит из кода команды 1, повторенного -gj раз. В блок 17 памяти построчно загружаются модифицированные векторы В,...,В).

Группа триггеров 28 образует память управляющего автомата. Дешифратор 32 предназначен для определения текущего состояния управляющего автомата и формирования выходных сигналов блока управления. Состояния управляющего автомата кодируются следующим образом: 0, 1; а 010 Q6-111; 37( где двоичными числами обозначены состояния триггеров 29 - 31 .

После загрузки исходных данных -по сигналу Пуск генератор 27 тактовых импульсов начинает формирование тактовых импульсов. Поскольку триггеры 29-31 находятся в нулевом состоянии (состояние QJуправляющего автомата), первый тактовый импульс через элементы И 33, ИЛИ 40 и 41 дешифратора 32 поступает на вход Пуск генератора 1 псевдослучайных кодов и на вход блока 3 многосвязной цепи Маркова. При этом генератор 1 псевдослучайных кодов вырабатывает псевдослучайное число, которое поступает на первую группу информационных входов (вход D.) мультиплексора 6 узла 2 выдачи теста, а генератор 13 - псевдослучайное число,. которое поступает на первую группу адресных входов (вход А,) блока 14 памяти. Изменение адреса на входе А5 запускает процесс чтения из блока 14 памяти. При этом, в качестве адреса

516

строки используется содержимое регистров 12.1-12.г. На выходе блока 14 памяти появляется номер некоторого состояния S r-связной цепи Маркова. Код поступает на информационные вхо- ды регистра 15.

Поскольку в состоянии О (код 000) выходы элементов И 33 и ИЛИ 26 установлены в единицу, по заднему фронту первого тактового импульса триггер 31 устанавливается в единицу (состояние QI управляющего автомата). Второй тактовый импульс через элемент И 34 поступает на вход Пуск блока 4 формирования последовательности цепи Маркова . Генератор 16 в ырабатывает псевдослучайное число, которое поступает на группу адресных входов (вход А блока 17 памяти, а в регистр 15 фиксируется код f, который поступает на информационные входы регистра 12.1, группы 11 и на группу адресных входов (вход А) блок 17 памяти. Изменение адреса запускает процесс чтения из блока 1/ памяти. На выходе блока 1 памяти появляется код (первое слово) некоторой команды I из класса Т,1, который поступает на вторую группу информационных входов (вход D2) мультиплексора 6 узла 2 выдачи теста и на дешифратор 18 блока 5 управления. По заднему фронту второго тактового импульса триггер 30 переходит в единичное состояние (состояние Q управляющего автомата). I

Третий тактовый импульс через элемент И 35 третьего дешифратора 32 поступает на Вход 2 узла 2 выдачи теста и. на входы Прием и Пуск блока 3 многосвязной цепи Маркова. Триггер 8 узла 2 выдачи теста устанавливается в единичное состояние, коммутируя вход D мультиплексора 6 на его выход. Рассматриваемый тактовый импульс, переходя через элемент ИЛИ 9 и элемент 10 задержки, фиксирует в буферный регистр 7 код команды I который поступает на выход формирователя. Одновременно генератор 13 псевдослучайной последовательности вырабатывает очередное псевдослучайное число, которое поступает на первую группу адресных входов (вход А,) блока 14 памяти, в регистр 12.1 записывается информация, поступающая с выхода регистра 15, т.е. код f, а в регистры 12.2 - 12.г - информация с выходов

7696

регистров 1 .1 - 12.Г-1 соответственно .

Содержимое регистров 12.1-12.г образует новьй адрес строки, который поступает на группу адресных входов (вход Ал) блока 14 памяти. Изменение адреса .запускает процесс чтения из блока 14 памяти. На выходе блока 14

памяти появляется номер W очередного состояния Зацепи Маркова, который поступает на информационные входы регистра 15.

В состоянии Я управляющего автомата, в зависимости от значения сигнала на выходе 18.1 дешифратора 18 происходит следующее. ,

Если длина команды I равна единице, выход 18.1 дешифратора 18, выходы

0 элементов И 23 и ИЛИ 25 находятся в единичном состоянии и по заднему фронту третьего тактового импульса триггер 30 сбрасывается в нуль (состояние d управляющего автомата).

5 В противном случае, выход 18.1

находится в нулевом состоянии, а выход элемента И 22 - в единичном состоянии, по заднему фронту третьего тактового импульса триггер 31 сбрасы0 вается в нуль (состояние (fy управляю-, щего автомата).

В случае, если длина команды равна единице, то следующий тактовый импульс вновь поступает на входы Пуск

5 блока 4 и на вход Выдача блока 3. Генератор 16 вырабатывает очередное число, из блока 15 фиксируется код W состояния Sw цепи Маркова, из бло- ка 17 памяти считывается код очеред- ной команды из класса 1, который поступает на вход DJ. мультиплексора 6 и на дешифратор 18 блока 5 управления, по заднему фронту текущего тактового

с импульса триггер 30 переходит в единичное состояние (состояние Ola управляющего автомата). Очередной так-, товый импульс поступает на Вход 2 узла 2 и на входы Прием и Пуск

Q блока 3. При этом в регистре 7 фиксируется код команды , генератор 13 вырабатывает очередное число, в регистр 12.1 записывается код W, поступающий с выхода регистра 15, а в регистры 12. Л - 12.г записываются коды, поступающие с выходов регистров 12.1 - 12.Г-1 соответственно, запускается процесс чтения из блока 14 памяти и т.д.

if с больше, чем единица, то следующий

тактовый импульс через элементы И 36 и ИЛИ 42 поступает на Вход 1 узла 2, устанавливает триггер в нуле- вое состояние, подключает вход D, мультиплексора 6 к его выходу и фиксирует состояние в буферном регистре 7 в качестве второго слова команды, код с выхода генератора 1. С Приходом заднего фронта рассматриваемого тактового импульса триггер 29 переходит в единичное состояние (состояние (состояние dj. управляющего 5автомата). 1 Очередной тактовый импульс через элементы И 37 и ИЛИ 41 дешифратора 32 поступает на вход Пуск генератора 1, который вырабатывает очередное число. В состоянии а5 управляющего автомата в зависимости от значения сигнала на выходе 18.2 дешифратора 18 происходит следующее.

Если длина команды I равна двум, выход 18.2 дешифратора 18, выходы элементов И 21 и ИЛИ находятся в единичном состоянии, по заднему фронту тактового импульса триггеры 29 и 30 переходят в нулевое состояние, а триггер 31 переходит в единичное состояние (состояние 01$ управляющего автомата).

В противном случае, выход 18.2 находится в нулевом состоянии, а выходы элементов И 20 и ИЛИ 26 находятся в единичном состоянии, по заднему фронту тактового импульса триггер 31 переходит в единичное состояние (состояние cfg управляющего автомата). , В случае, если длина команды 1С равна 2, с приходом следующих тактовых импульсов аналогичным образом формируется следующий код слова команды

Если же длина команды 1 больше 2,

.

-с

очередной тактовый импульс через элементы И 38, ИЛИ 42, дешифратор 32, элемент ИЛИ 9, элемент 10 задержки фиксирует в буферном регистре 7 третье слово команды, получаемое через мультиплексор 6 от генератора 1. Поскольку в состоянии Og выход элемента ИЛИ 25 установлен в единичное состояние, то по заднему фронту .тактового импульса триггер 30 сбрасывается в нуль.

Очередной тактовый импульс через элементы И 39, ИЛИ 41 дешифратора 32

5 „

5

0

5

0

5

поступает на вход Пуск генератора 1, который вырабатывает очередное число.

По заднему фронту тактового импульса триггер 29 сбрасывается в нуль (состояние аг управляющего автомата). С приходом следующего тактового импульса начинается формирование следующего кода слова команды.

Таким образом, смена состояний dj, Qj управляющего автомата обеспечивает формирование первого слова команды, смена состояний О 4, Q$ обеспечивает формирование второго слова команды, смена состояния ЈJg, Q7 - третьего слова команды и т.д.

Формула изобретен.и я

Формирователь тестов, содержащий генератор псевдослучайных кодов, узел выдачи теста, блок формирования последовательности кодов микротестов, блок управления, при этом узел выдачи теста содержит буферный регистр, мультиплексор, триггер, элемент ИЛИ и элемент задержки, блок формирования последовательности кодов микротестов содержит первый генератор псевдослу-. чайной последовательности и первый блок памяти, блок управления содержит три дешифратора, группу триггеров и генератор тактовых импульсов, причем первый и второй выходы первого деши-., фратора соединены соответственно с . первым и вторым входами второго дешифратора, группа выходов узла выдачи теста является группой выходов формирователя, первый, второй и третий выходы второго дешифратора соединены соответственно с первым, вторым, третьим входами сброса соответствующих триггеров группы, первый выход третьего дешифратора соединен с входом сброса триггера узла выдачи теста и первым входом элемента ИЛИ, выход которого соединен с входом элемента задержки, выход которого соединен с входом синхронизации буферного регистра, второй выход третьего дешифра- . тора соединен с входом генератора псевдослучайных кодов, группа входов мультиплексора, группа выходов которого соединена с информационными входами буферного регистра, группа выходов KOTopo.ro соединена с группой выходов узла выдачи теста, третий выход третьего дешифратора соединен с вторым входом элемента ИЛИ и с.входом установки триггера узла вьщачи теста, выход которого соединен с управляющим входом мультиплексора, четвертый выход третьего дешифратора соединен с входом первого генератора псевдослучайной последовательности, группа выходов которого соединена с первой группой адресных входов первог го блока памяти, вторая группа инфор- мационных входов которого соединена с группой выходов третьего дешифратора, стробирующий вход которого соединен с выходом генератора тактовых импульсов и с входами синхронизации триггеров группы, группа выходов ко- торых соединена с группой информационных входов третьего дешифратора, с пятого по девятый выходы третьего дешифратора соединены соответственно с третьего по седьмой входами второго дешифратора, вход установки третье- его триггера группы триггеров соединен с выходом второго дешифратора, вход пуска генератора тактовых им- пульсов соединен с входом пуска формирователя, отличающийся тем, что, с целью повышения полноты тестов за счет формирования многосвязных последовательностей кодов микротестов, формирователь содержит блок многосвязной цепи Маркова, включающий в себя второй генератор псевдослучайной последовательности, группу регистров, регистр и второй блок памяти, первая группа адресных входов которого соединена с группой выходов второго генератора псевдослучайной последовательности, вход которого соединен с десятым выходом третьего дешифратора, одиннадцатый и двенадцатый выходы которого соединены с входами установки первого и второго триггеров группы, выходы регистров группы соединены с второй группой адресных входов второго блока памяти, группа выходов которого соединена с группой информационных входов регистра, груп.- па выходов которого соединена с группой информационных входов первого регистра группы и с второй группой адресных входов первого блока памяти, группа выходов которого соединена с группой информационных входов первого дешифратора и с второй группой информационных входов мультиплексора, вход синхронизации регистра соединен с четвертым выходом третьего дешифратора, третий выход которого соединен с входом синхронизации регистров группы, группа выходов 1-го регистра группы (, r-1, r - число регистров группы) соединена с группой информационных входов (i+1)-ro регистра группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Формирователь тестов | 1987 |

|

SU1552185A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2010316C1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1334139A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

Изобретение относится к вычислительной технике и может быть использовано при автоматическом контроле микропроцессорных устройств. Цель изобретения - повышение полноты тестов за счет формирования многосвязных последовательностей кодов микротестов. Управление процессом формирования тестов с помощью многосвязной цепи Маркова позволяет повысить обнаруживающую способность (полноту) формируемых тестов за счет обеспечения условий загрузки, проявления и транспортировки неисправностей. 5 ил.

7k A

$

А Л

О

1

Фиг.1

Фиг. 2

OmS

Пуск

OnS

Прием

t

122

OnS

выдача

11

i С

К

КЧ

ФигЛ

| Формирователь тестов | 1987 |

|

SU1552185A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-07—Публикация

1989-03-09—Подача