т

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь тестов | 1989 |

|

SU1661769A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2010316C1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для моделирования случайных процессов | 1984 |

|

SU1223227A1 |

| Устройство для формирования тестовых воздействий | 1985 |

|

SU1555705A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах контроля. Цель изобретения - повышение быстродействия. Формирователь содержит узел 4 выдачи теста, генератор 1 псевдослучайных кодов, блок управления 5, блок 2 формирования последовательности микротестов 6 и дешифратор 3. 7 илл.

м

5± Ј2

И

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах контроля.

Цель изобретения - повышение быстродействия .

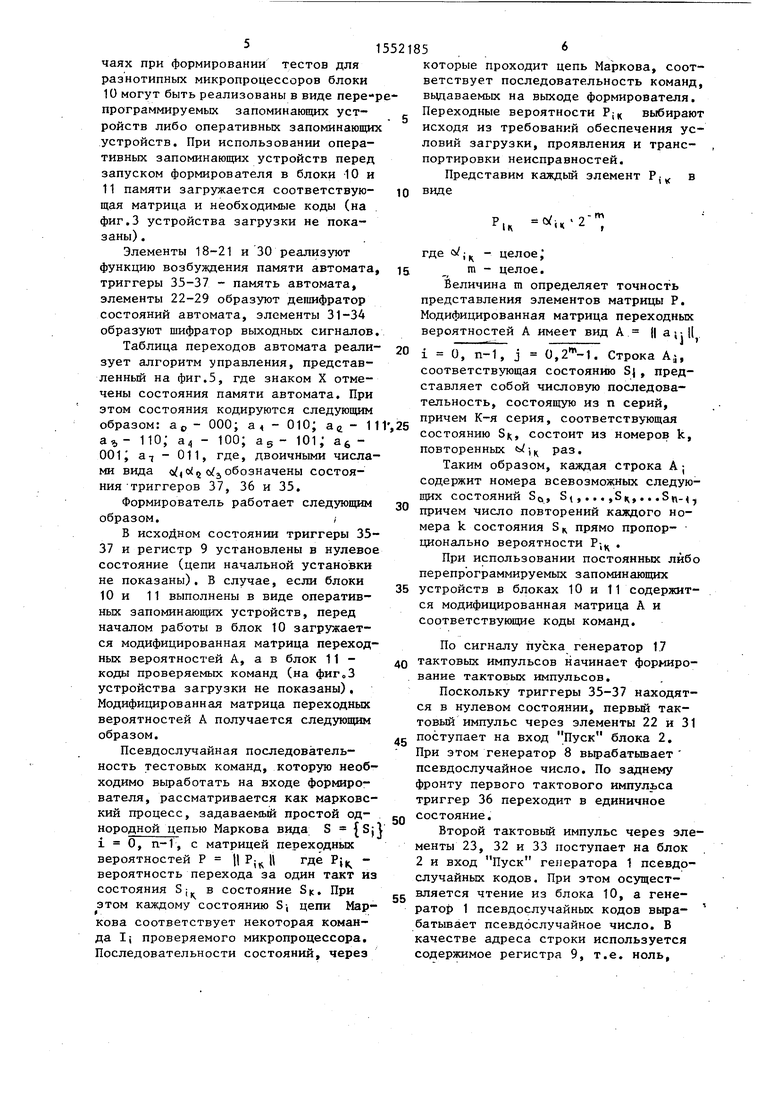

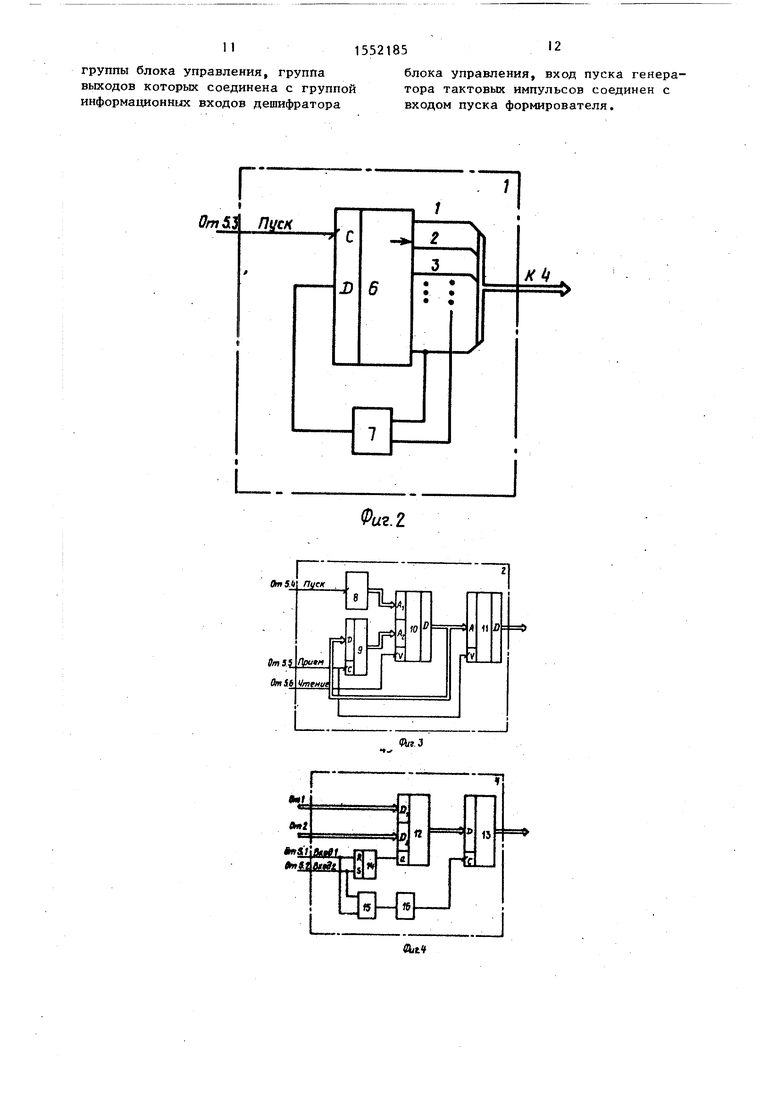

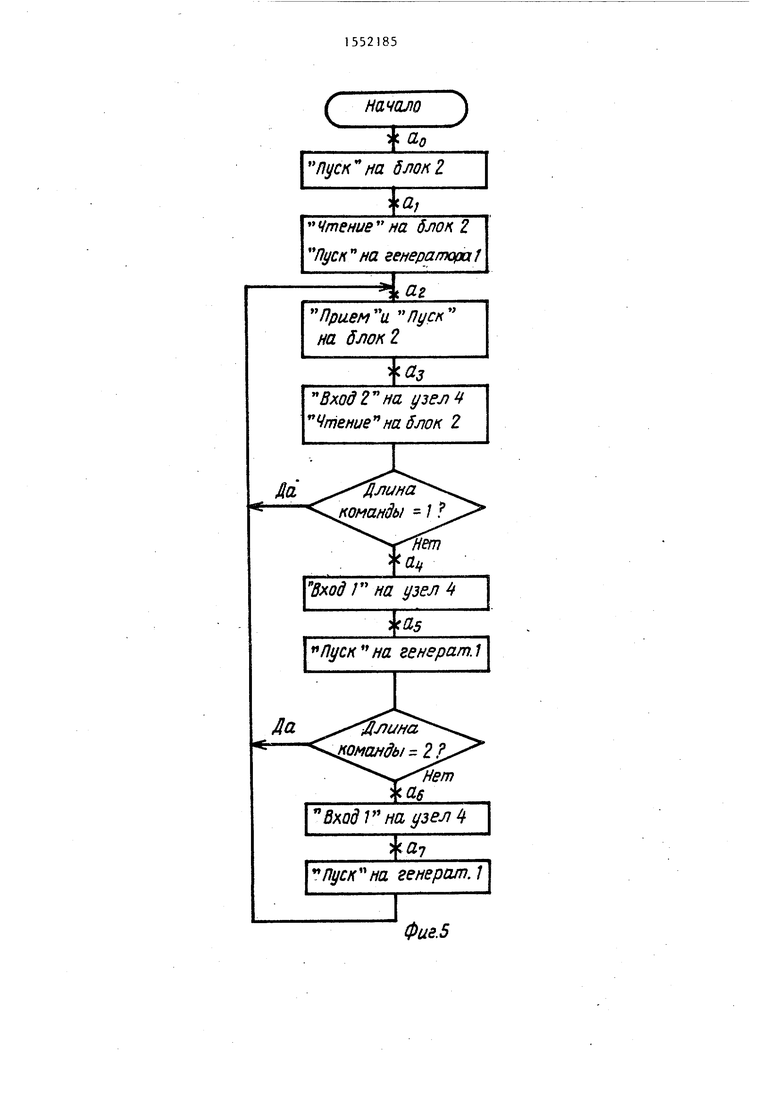

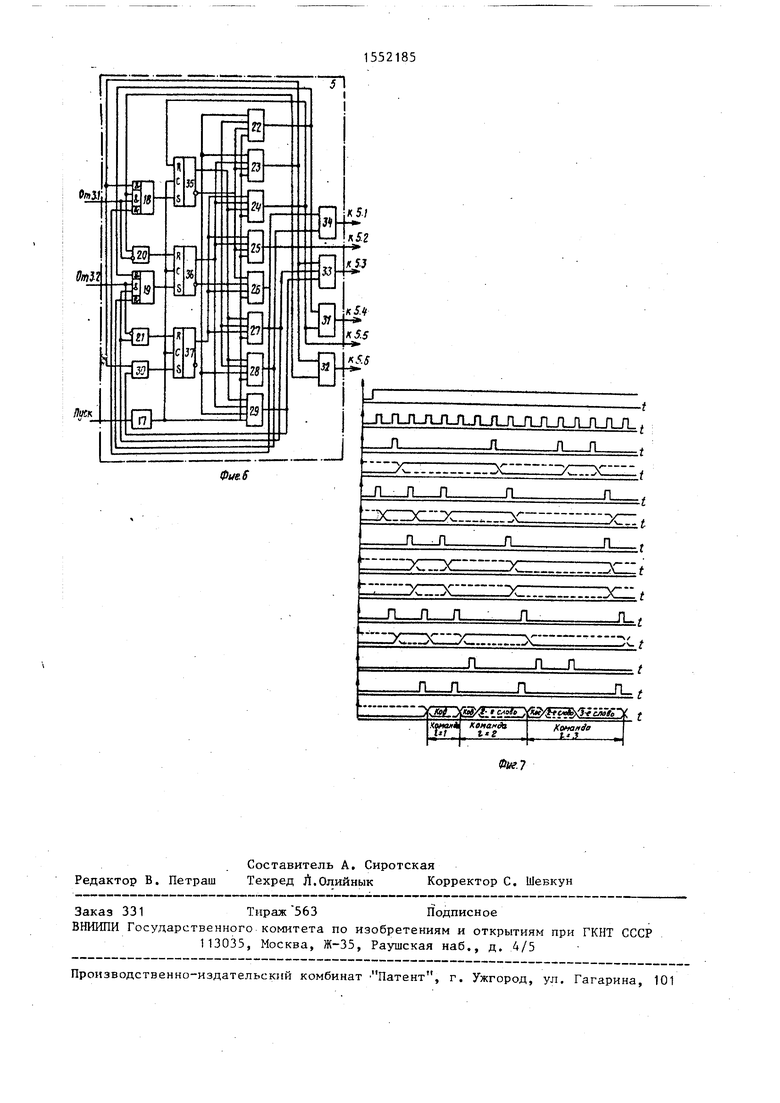

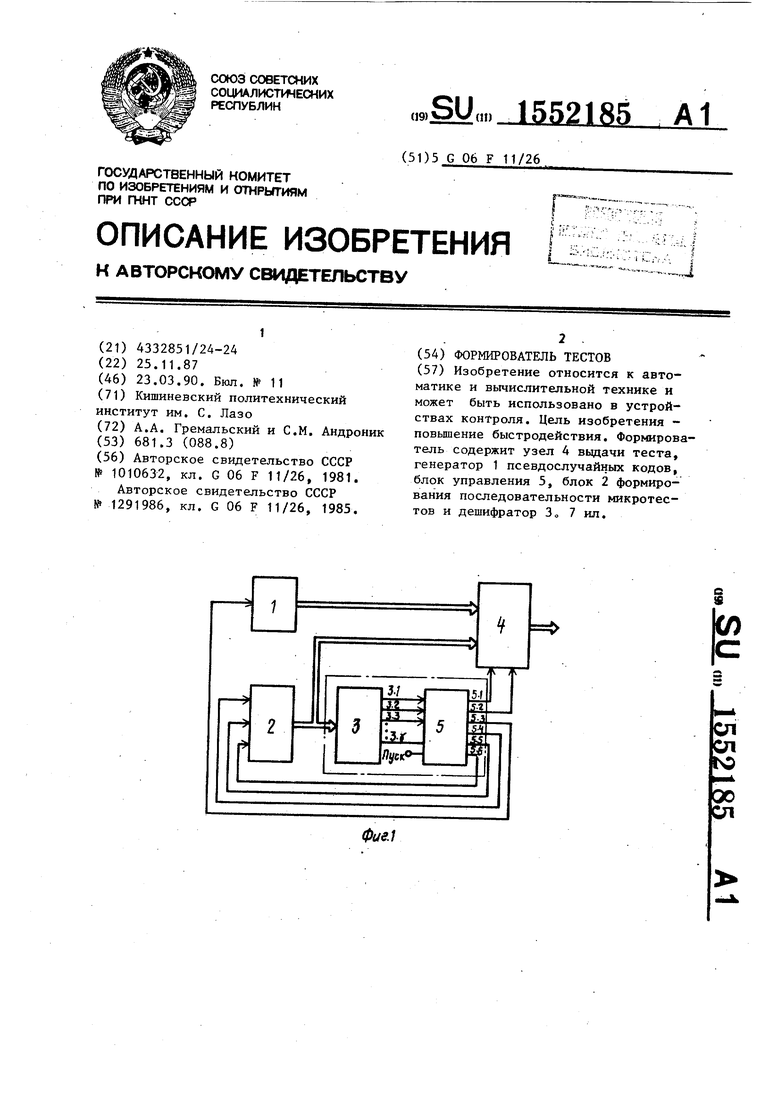

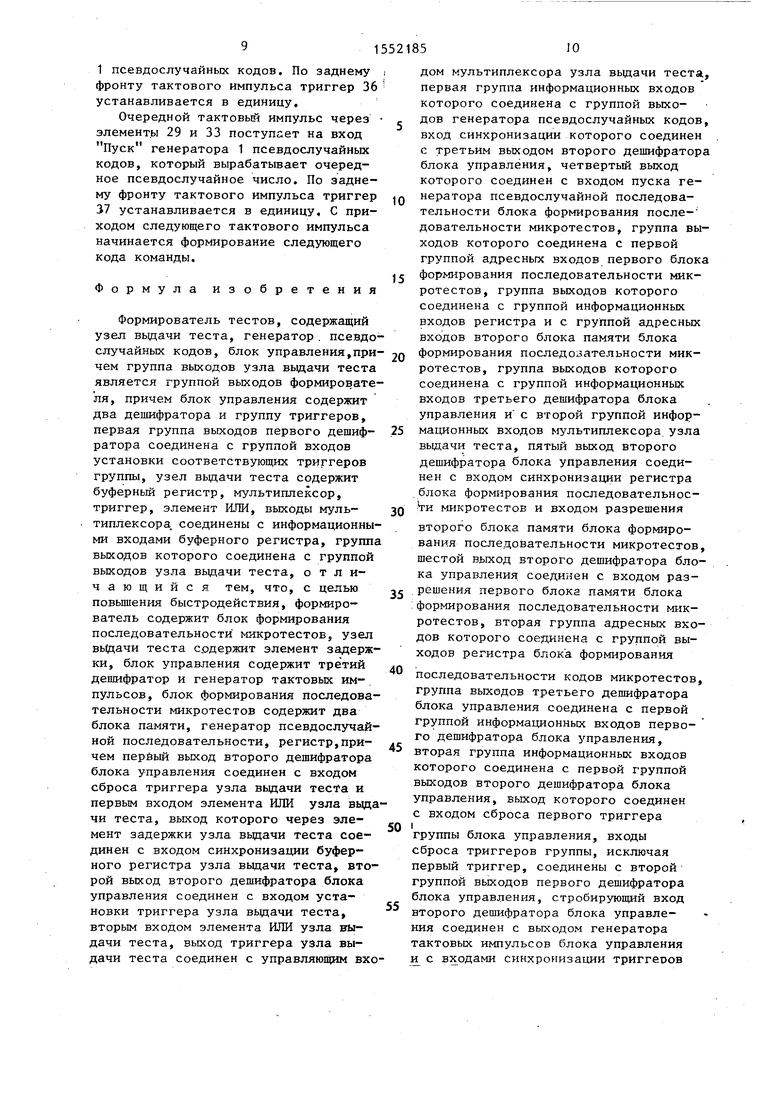

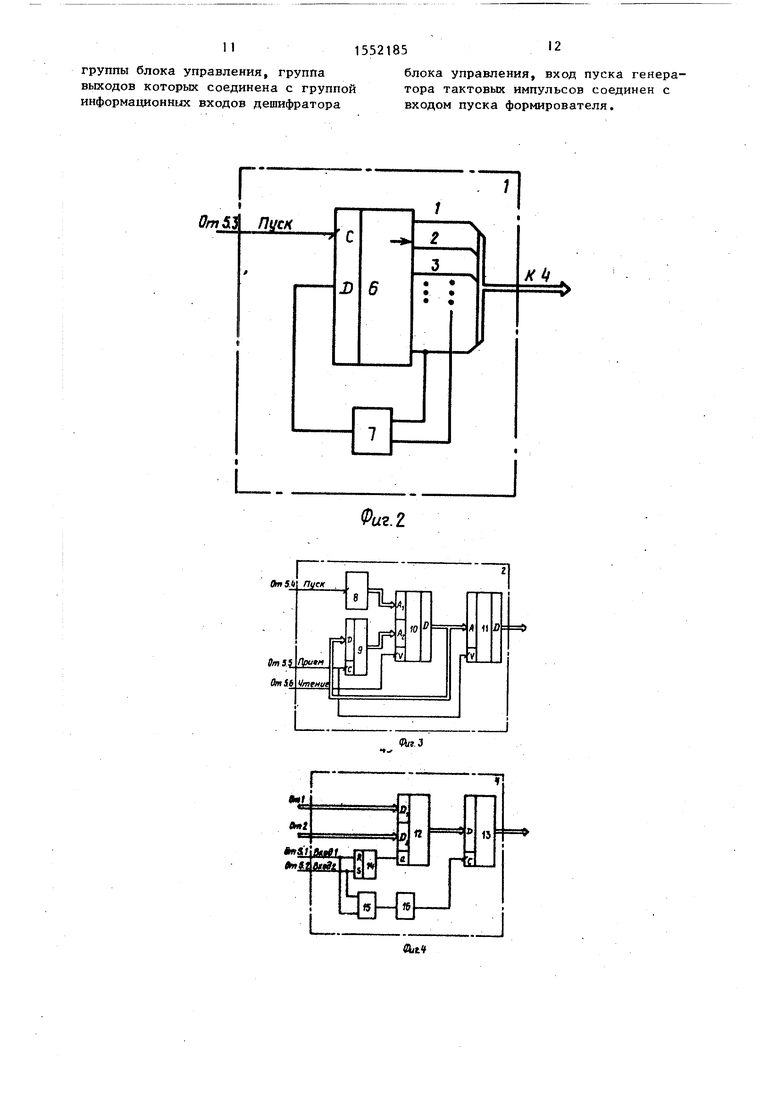

На фиг.1 представлена структурная фхема формирователя; на фиг.2 - схема генератора псевдослучайных кодов; на фиг.З - схема блока формирования Последовательности микротестов; на сриг.4 - схема узла выдачи теста; на оиг.5 - блок-схема работы блока управления , на фиг.6 - схема блока управления; .на фиг.7 - временные диаграммы работы формирователя.

Формирователь тестов содержит ге ератор 1 псевдослучайных кодов,блок JZ формирования последовательности Цшротестов, дешифратор 3 длины ко- Манды, узел 4 выдачи теста, блок 5 управления.

В генераторе (фиг„2) используется сдвиговый регистр 6 и сумматор 7 по Модулю два.

Блок 2 (фиг.З) содержит генератор 8 псевдослучайной последовательности регистр 9, блок 10 памяти модифицированной матрицы переходных вероятностей и блок 11 памяти кодов команд

Узел 4 выдачи теста (фиг.4) пред- |Назначен для формирования очередного {слова команды и состоит из мультиплексора 12, буферного регистра 13, триггера 14, элемента ИЛИ 15 и эле- мента 16 задержки.

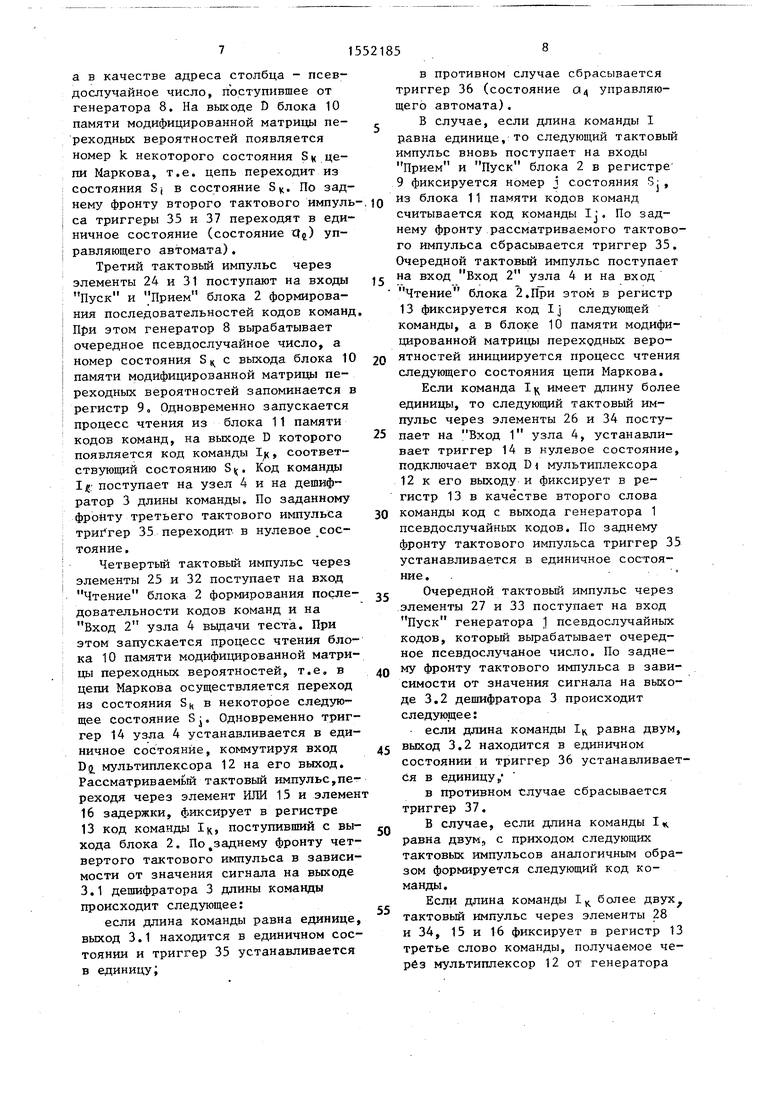

Блок 5 управления (фиг.5) представляет собой синхронный управляющи .автомат с множеством внутренних состояний |aD,a1,..,,a7JH содержит генератор 17 тактовых импульсов, элементы И-ИЛИ 18 и 19, элементы И 20- 29, элементы ИЛИ 30-34 и триггеры 35-37. Причем элементы 18-21, 30 образуют дешифратор, элементы 22-29 и 31-34 образуют шифратор.

Генератор 1 псевдослучайных кодов предназначен для генерации случайных чисел, используемых в качестве второго, третьего и т.д„ слова команды, т.е. в качестве адресов и данных В простейшем случае он может быть реализован на сдвиговых регистрах с обратными связями.

Блок 2 формирования последовательности микротестов предназначен для формирования первого слова команды. Формируемые слова образуют

0

5

0

5

0

5

0

5

0

5

псевдослучайную последовательность, в которой вероятность появления очередного кода команды зависит от того, какой код команды выдавался в предыдущем такте. Стохастические свойства указанной последовательности определяются матрицей переходных вероятностей цепи Маркова.

Дешифратор 3 предназначен для определения структуры формируемой команды. На вход дешифратора поступает первое слово команды, а на его i-м выходе, где i - длина дешифруемой команды, появляется сигнал логической единицы. Дешифратор имеет выходов 1-1,где 1 - максимально возможная длина команды).

Генератор 8 псевдослучайных чисел вырабатывает равномерно распределенные числа. В простейшем случае он может быть реализован по той же схеме, что и генератор 1 (фиг.2). При подаче на вход генератора 8 сигнала Пуск на его выходе появляется псевдослучайное число. Очередное псевдослучайное число вырабатывается при подаче следующего сигнала Пуск и т.д.

Регистр 9 предназначен для хранения номера текущего состояния (адреса строки) цепи Маркова. Блок 10 памяти модифицированной матрицы переходных вероятностей представляет собой двухмерный массив из log2nL- разрядных слов, где п - число состояний цепи Марковао Число п состояний цепи определяется числом команд микропроцессора, для проверки которых необходимо сформировать соответствующий тест.Адресация слова осуществляется путем указания номера строки в регистре 9 (вход А) и номера столбца на выходе генератора 8 (вход Ад). Число строк блока 10 памяти модифицированной матрицы переходных вероятностей равно п, а число столбцов 2, где m определяется способом представления переходных вероятностей

- г/ . , о ; .

- ; j-i , d,j

целое,

в виде Pu

В простейшем случае блок 10 и блок 11 - постоянные запоминающие устройства, содержащие соответствующую матрицу и коды. Мультиплексор 12 в зависимости от значения сигнала на его управляющем входе передает на выход либо данные с входа D(, ( Q 0), либо данные с входа D ч ( Q 1) . В более сложных слу

чаях при формировании тестов для разнотипных микропроцессоров блоки

10могут быть реализованы в виде пере-р программируемых запоминающих устройств либо оперативных запоминающих устройств. При использовании оперативных запоминающих устройств перед запуском формирователя в блоки 10 и

11памяти загружается соответствующая матрица и необходимые коды (на фиг.З устройства загрузки не показаны) .

Элементы 18-21 и 30 реализуют функцию возбуждения памяти автомата, триггеры 35-37 - память автомата, элементы 22-29 образуют дешифратор состояний автомата, элементы 31-34 образуют шифратор выходных сигналов.

Таблица переходов автомата реализует алгоритм управления, представленный на фиг.5, где знаком X отмечены состояния памяти автомата. При этом состояния кодируются следующим образом: а 0 - 000; а - 010; ае- 11 аъ- 110; а 4 - 100; as - 101; а6 - 001; a - 011, где, двоичными числами вида , tf Q с/э обозначены состояния триггеров 37, 36 и 35.

Формирователь работает следующим образом./

В исходном состоянии триггеры 35- 37 и регистр 9 установлены в нулевое состояние (цепи начальной установки не показаны). В случае, если блоки 10 и 11 выполнены в виде оперативных запоминающих устройств, перед началом работы в блок 10 загружается модифицированная матрица переходных вероятностей А, а в блок 11 - коды проверяемых команд (на фиг«,3 устройства загрузки не показаны). Модифицированная матрица переходных вероятностей А получается следующим образом.

Псевдослучайная последовательность тестовых команд, которую необходимо выработать на входе формирователя, рассматривается как марковский процесс, задаваемый простой од- нородной цепью Маркова вида S i 0, п-1, с матрицей переходных

вероятностей Р || Р; | вероятность перехода за один состояния S, в состояние этом каждому состоянию S-,

гДе щ

Р такт из

SK. При цепи Маркова соответствует некоторая команда Ij проверяемого микропроцессора. Последовательности состояний, через

которые проходит цепь Маркова, соответствует последовательность команд, выдаваемых на выходе формирователя. Переходные вероятности PiK выбирают исходя из требований обеспечения условий загрузки, проявления и транспортировки неисправностей.

Представим каждый элемент Р, виде

к

U

tf

IK

15

0

5

0

35

0

5

0

5

где CS/;K - целое, m - целое.

Величина m определяет точность представления элементов матрицы Р. Модифицированная матрица переходных вероятностей А имеет вид А || .

1 0, n-1, j 0,. Строка Aif соответствующая состоянию S , представляет собой числовую последовательность, состоящую из п серий, причем К-я серия, соответствующая состоянию 5ц, состоит из номеров k, повторенных ь/-, раз.

Таким образом, каждая строка А | содержит номера всевозможных следующих состояний SQ, S t,... ,Sц,...S(i-| 7 причем число повторений каждого номера k состояния S K прямо пропорционально вероятности Р;К .

При использовании постоянных либо перепрограммируемых запоминающих устройств в блоках 10 и 11 содержится модифицированная матрица А и соответствующие коды команд.

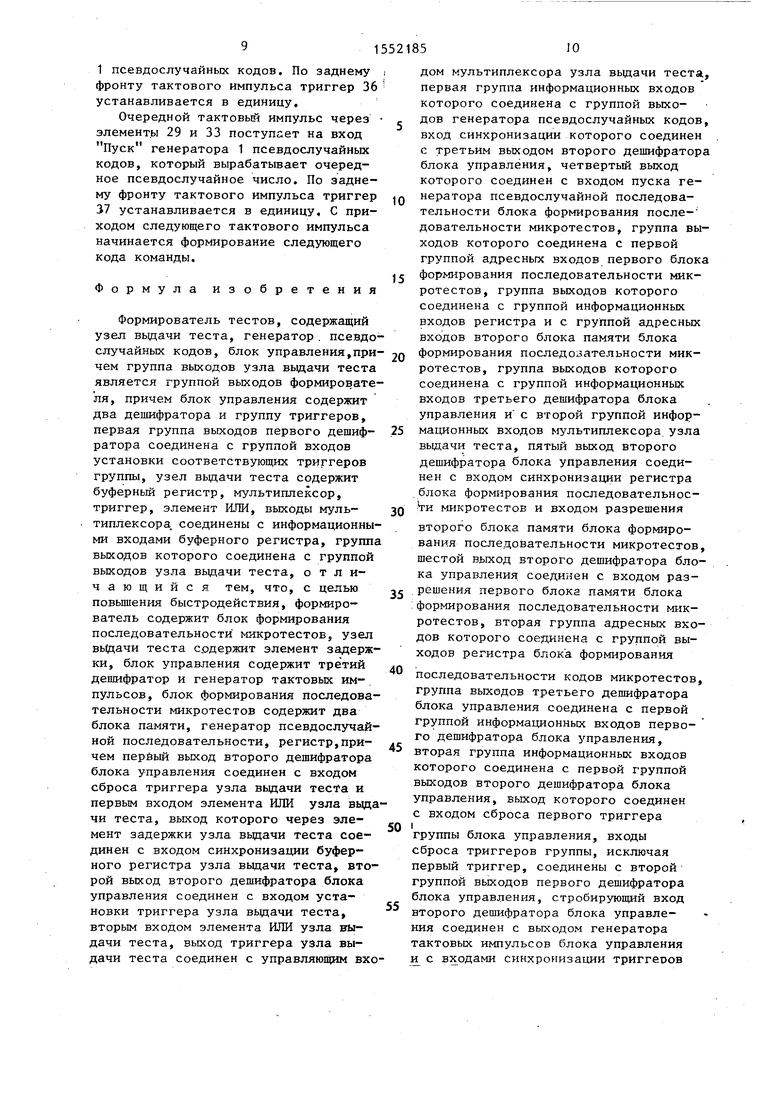

По сигналу пуска генератор 17 тактовых импульсов начинает формирование тактовых импульсов.

Поскольку триггеры 35-37 находятся в нулевом состоянии, первый тактовый импульс через элементы 22 и 31 поступает на вход Пуск блока 2. При этом генератор 8 вырабатывает псевдослучайное число. По заднему фронту первого тактового импульса триггер 36 переходит в единичное состояние.

Второй тактовый импульс через элементы 23, 32 и 33 поступает на блок

2и вход Пуск генератора 1 псевдослучайных кодов. При этом осуществляется чтение из блока 10, а генератор 1 псевдослучайных кодов выра- батывает псевдослучайное число. В качестве адреса строки используется содержимое регистра 9, т.е. ноль,

а в качестве адреса столбца - псевдослучайное число, поступившее от генератора 8. На выходе D блока 10 памяти модифицированной матрицы пе- реходных вероятностей появляется номер k некоторого состояния S« цепи Маркова, т.е. цепь переходит из состояния S, в состояние S. По заднему фронту второго тактового импуль са триггеры 35 и 37 переходят в единичное состояние (состояние qt) управляющего автомата).

Третий тактовый импульс через элементы 24 и 31 поступают на входы Пуск и Прием блока 2 формирования последовательностей кодов команд При этом генератор 8 вырабатывает очередное псевдослучайное число, а номер состояния S с выхода блока 10 памяти модифицированной матрицы переходных вероятностей запоминается в регистр 9. Одновременно запускается процесс чтения из блока 11 памяти кодов команд, на выходе D которого появляется код команды IK, соответствующий состоянию S$. Код команды 1 поступает на узел 4 и на дешифратор 3 длины команды. По заданному фронту третьего тактового импульса триггер 35 переходит в нулевое сос- тояние.

Четвертый тактовый импульс через элементы 25 и 32 поступает на вход Чтение блока 2 формирования после- довательности кодов команд и на Вход 2 узла 4 выдачи теста. При этом запускается процесс чтения блока 10 памяти модифицированной матрицы переходных вероятностей, т.е. в цепи Маркова осуществляется переход из состояния SK в некоторое следующее состояние S:. Одновременно тригJ

гер 14 узла 4 устанавливается в единичное состояние, коммутируя вход DЈ мультиплексора 12 на его выход. Рассматриваемый тактовый импульс,переходя через элемент ИЛИ 15 и элемен 16 задержки, фиксирует в регистре 13 код команды 1К, поступивший с вы- хода блока 2. По „заднему фронту четвертого тактового импульса в зависимости от значения сигнала на выходе 3.1 дешифратора 3 длины команды происходит следующее:

если длина команды равна единице, выход 3.1 находится в единичном состоянии и триггер 35 устанавливается в единицу;

5 0 5 0

5 0

5 Q

5

в противном случае сбрасывается триггер 36 (состояние 04 управляющего автомата).

В случае, если длина команды I равна единице, то следующий тактовый импульс вновь поступает на входы Прием и Пуск блока 2 в регистре 9 фиксируется номер j состояния S , из блока 11 памяти кодов команд считывается код команды I:, По заднему фронту рассматриваемого тактового импульса сбрасывается триггер 35. Очередной тактовый импульс поступает на вход Вход 2 узла 4 и на вход Чтение блока 2.При этом в регистр 13 фиксируется код Ij следующей команды, а в блоке 10 памяти модифицированной матрицы переходных вероятностей инициируется процесс чтения следующего состояния цепи Маркова.

Если команда 1К имеет длину более единицы, то следующий тактовый импульс через элементы 26 и 34 поступает на Вход 1 узла 4, устанавливает триггер 14 в кулевое состояние, подключает вход D мультиплексора 12 к его выходу и фиксирует в регистр 13 в качестве второго слова команды код с выхода генератора 1 псевдослучайных кодов. По заднему фронту тактового импульса триггер 35 устанавливается в единичное состояние.

Очередной тактовый импульс через элементы 27 и 33 поступает на вход Пуск генератора псевдослучайных кодов, который вырабатывает очередное псевдослучаное число. По заднему фронту тактового импульса в зависимости от значения сигнала на выходе 3.2 дешифратора 3 происходит следующее:

если длина команды 1К равна двум, выход 3.2 находится в единичном состоянии и триггер 36 устанавливается в единицу „

в противном случае сбрасывается триггер 37.

В случае, если длина команды I равна двум, с приходом следующих тактовых импульсов аналогичным образом формируется следующий код команды.

Если длина команды 1К более двух тактовый импульс через элементы 28 и 34, 15 и 16 фиксирует в регистр 13 третье слово команды, получаемое через мультиплексор 12 от генератора

1 псевдослучайных кодов. По заднему фронту тактового импульса триггер 36 устанавливается в единицу.

Очередной тактовый импульс через элементы 29 и 33 поступает на вход Пуск генератора 1 псевдослучайных кодов, который вырабатывает очередное псевдослучайное число. По заднему фронту тактового импульса триггер 37 устанавливается в единицу, С приходом следующего тактового импульса начинается формирование следующего кода команды.

Формула изобретения

Формирователь тестов, содержащий узел выдачи теста, генератор псевдослучайных кодов, блок управления,при- чем группа выходов узла выдачи теста является группой выходов формирователя, причем блок управления содержит два дешифратора и группу триггеров, первая группа выходов первого дешиф- ратора соединена с группой входов установки соответствующих триггеров группы, узел выдачи теста содержит буферный регистр, мультиплексор, триггер, элемент ИЛИ, выходы муль- типлексора. соединены с информационными входами буферного регистра, группа выходов которого соединена с группой выходов узла выдачи теста, отличающийся тем, что, с целью повышения быстродействия, формирователь содержит блок формирования последовательности микротестов, узел выдачи теста содержит элемент задержки, блок управления содержит третий дешифратор и генератор тактовых импульсов, блок формирования последовательности микротестов содержит два блока памяти, генератор псевдослучайной последовательности, регистр,при- чем первый выход второго дешифратора блока управления соединен с входом сброса триггера узла выдачи теста и первым входом элемента ИЛИ узла выдачи теста, выход которого через элемент задержки узла выдачи теста соединен с входом синхронизации буферного регистра узла выдачи теста, второй выход второго дешифратора блока управления соединен с входом установки триггера узла выдачи теста, вторым входом элемента ИЛИ узла выдачи теста, выход триггера узла выдачи теста соединен с управляющим входом мультиплексора узла выдачи теста первая группа информационных входов которого соединена с группой выходов генератора псевдослучайных кодов вход синхронизации которого соединен с третьим выходом второго дешифратор блока управления, четвертый выход которого соединен с входом пуска генератора псевдослучайной последовательности блока формирования последовательности микротестов, группа выходов которого соединена с первой группой адресных входов первого блок формирования последовательности микротестов, группа выходов которого соединена с группой информационных входов регистра и с группой адресных входов второго блока памяти блока формирования последовательности микротестов, группа выходов которого соединена с группой информационных входов третьего дешифратора блока управления и с второй группой информационных входов мультиплексора узла выдачи теста, пятый выход второго дешифратора блока управления соединен с входом синхронизации регистра блока формирования последовательности микротестов и входом разрешения

второго блока памяти блока формирования последовательности микротестов шестой выход второго дешифратора блока управления соединен с входом разрешения первого блока памяти блока формирования последовательности микротестов, вторая группа адресных входов которого соединена с группой выходов регистра блока формирования

последовательности кодов микротестов группа выходов третьего дешифратора блока управления соединена с первой группой информационных входов первого дешифратора блока управления, вторая группа информационных входов которого соединена с первой группой выходов второго дешифратора блока управления, выход которого соединен

с входом сброса первого триггера

i

группы блока управления, входы

сброса триггеров группы, исключая первый триггер, соединены с второй группой выходов первого дешифратора блока управления, стробирующий вход второго дешифратора блока управления соединен с выходом генератора тактовых импульсов блока управления и с входами синхронизации триггеров

группы блока управления, группа выходов которых соединена с группой информационных входов дешифратора

Г

ОтЫ

Писк

С

D

v

I

блока управления, вход пуска генератора тактовых импульсов соединен с входом пуска формирователя.

«

Фаъ.г

С

блок2 Jf7

Чтение на блок 2 Пуск на генератора 1

Приемки. Пуск на блок 2

Вход2 на узел Ч Чтение на блок 2

Ad

ffxod / на узел 4

Пуск на генерат.1

Да Цлина

Команды-2

Нет ив

1 ВходТна, узел 4

генерал.

начало

)

iSL

JLЈL

Фиг.5

э щ

arв

к 5.}

, к5ц

H/rf к 5.5

Щр

Пхк

ts

Фае. 6

K5t

KS.Z

к 5.}

nJOJlJUULJlJUUUUUUUUl.

П П П

л

Л

:t

ЛП.

--t.

ЛTL

t

t t

t

ЛTL

П

TL

| Устройство для задания тестов | 1981 |

|

SU1010632A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Формирователь тестов | 1985 |

|

SU1291986A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-03-23—Публикация

1987-11-25—Подача