Предложенный реверсивный двоичный счетчик относится к области вычислительной техники н может быть применен в электронных вычислительных машинах.

Известны двоичные реверсивные счетчики, содержащие регистр кода, элементы «И и «ИЛИ и схему уиравления. В известных схемах счетчиков особенности элементов схемы (триггеров, усилителей, линий задержек, иепей одновременного распространення переноса и т. п.) не дают возможности постронть эффективную схему и осуществить логическую структуру, которая являлась бы оптимальной в смысле достижения максимального быстродействия при л инимальиом оборудовании.

Предложенный реверсивный двоичный счетчик отличается тем, что содержит регистр кода и регистр переноса, выполненные на парафазных элементах с управлением от двухфазного тактируюн1его генератора, причем единичный выход каждого разряда регистра кода соедннен со входами двух (первой и второй) из четырех схем «И, связанных через схему «ИЛИ со 1входом этого же разряда, а также соединен в этом и более старщих разрядах регистра переноса со входом второй схемы «И, одной из трех, связанных через схему «ИЛИ со входом этого разряда; нулевой выход каждого разряда регнстра кода соединен со входом третьей схемы «И того же и более старших разрядов регистра переноса; единичны) выход каждого разряда регистра исреноса соединен со входом нервой схемы «II да 1ного разряда, а также со входами третьей схемы «И в этом разряде регистра кода и четвертой схемы «И в еледующем; нулевой выход регистра иереноса соединен со входом четвертой схемы «II того же разряда и входом BTOpoii схемы «И следующего разряда регистра кода, выход усилителя сложения единицы одной фазы соединен со входом четвертой схемы «И каждого разряда регнстра кода, а выход усилителя сложения единицы другой фазы - со входом второй схемы «И каждого разряда регистра переноса; аналогично выход усилителя вычитания единицы одной фазы соедннен со входом третьей схемы «PI регистра кода, а выход усилителя другой фазы - со входом третьей схемы «И регистра переноса; выход тактирующего генератора одной фазы соедннен с одним из входов всех схем «И регистра кода, кроме первой, и со входом первой схемы «1Ь регистра переноса, а выход генератора другой фазы соединен с одним из входов всех остальных схем «И счетчика.

Предложенная схема счетчика сокращает время сложення илн вычнтания единицы, причем полное измснелие состояния счетчика занимает время двух полутактов работы тактирующего генератора.

В первую фазу тактирования устанавливаются единицы в тех разрядах регистра переноса, которые соответствуют иеирерывной, иачииая с первого разряда, иоследователыюсти единии--для сложения с единицей - плн нослсдовательиости нуле - для вычитания едиинцы - разрядов регистра кода, так что во вре.мя второй фазы тактировать разряды регистра переноса одновременно изменяют еостояния сс:ответствуюш,нх разрядов регистра кода, входяидих в указанную последовательность; это из,1еис1 ис состояний состоит в том, :то для с/южения с единицей разряды регист;:а кода -асятся з нули, а нервый нз разрядов, иаходивнигхся ;з пуле, устанавливается в единицу, а для вычитания единицы, разряды ре|истра К(хта устанавливаются в едги-шцы, и иержыГ разрядов, находивилихся в едишще, сб|;|ас1 1вается в пуль.

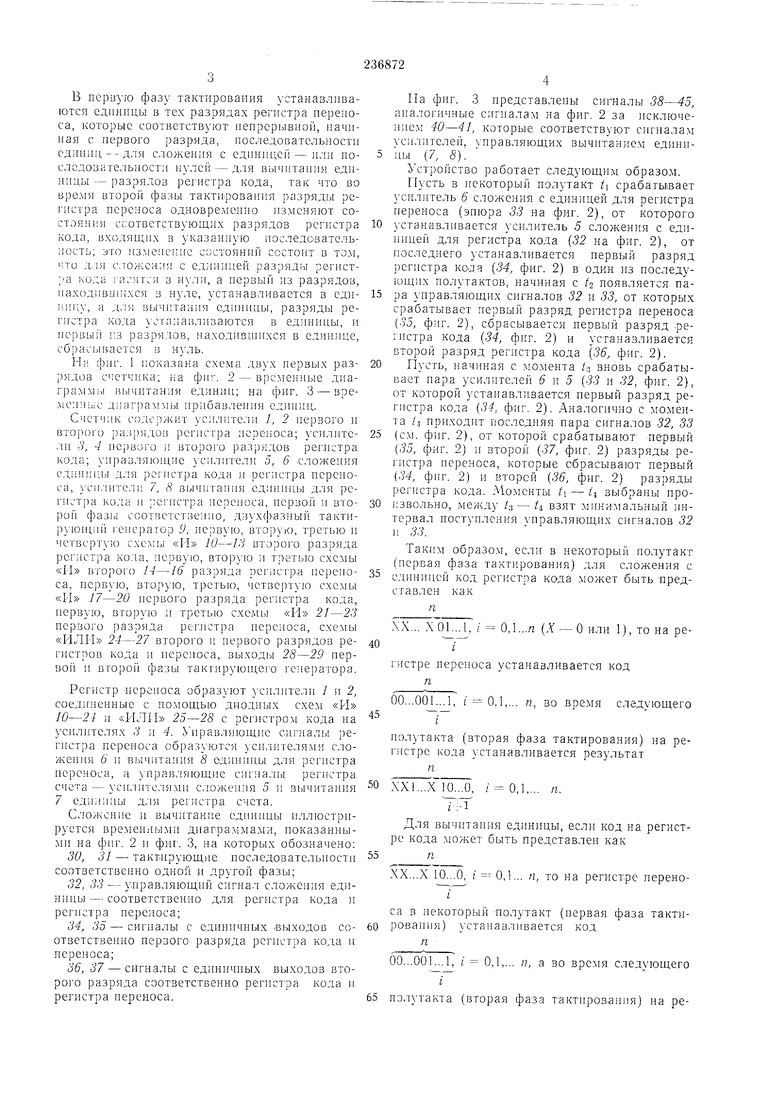

На фиг. 1 показана схема двух первых разрядов счетчика; на фиг, 2 - врсме;П ые диаграмм1 | вычитапия единиц; па фиг. 3 - временнь;с диаграммы ирибавления единиц.

Счетчик соде:1/к1-гг ус;глители /, 2 первого и второго ра: рядо1 регистра нереноса; усилители 3, 4 Hei)Boro и вторО 0 разрядов регистра кода; унразляюнгне усилители 5, 6 сложения e.uniiiiud для регистра кода и регистра цереноса, силители 7, 8 вьипггаиия едииицы для регистра кода и регистр.а переноса, нерво и вто|)ой фазы соответет15енно, двухфазиый тактируюпци геисрагор 9, нервую, вто|)у1О, третью и четвертую «И 10-13 второго разряда регистра ко.та, первую, вто|)ую и третьк схемы «II второго 14-16 разряда per-icTpa переноса, первую, вторую, третью, четвертую схе.мы «И 17-20 иервого разряда регистра кода, первую, вторую и третью схемы «И первого разряда регпстра переноса, схемы «ИЛИ 24-27 второго и нервого разрядов рег 1стров кода и перепоса, выходы 28-29 перBoii п .второй фазы такгнруюп его генератора.

Регистр цереноса образуют усилители / и 2, соединенные с номогцью диодных схем «И 10-21 и «ИЛИ 25-28 с регистром кода на усилителях 3 и 4. Управляющпе сигналы регистра переноса образуются успл ггелями сложе1П1я 6 и вьлчитання 8 едииииы для регистра переноса, а упра15; яющие сигиалы регистра счета - усилителями сложеиия 5 и вычитания 7 еддпииы д;1я регистра счета.

Сложение п вычнтан 1е едпппцы пллюстрпруется временнымп дпаграммамн, показаппымп на фиг. 2 и фиг. 3, па которых обозначепо;

30, 31 - тактнруюи|ие последовательпоети соответственно одной и другой фазы;

32, 33 - унравляюпдий енгнал еложепня едпницы - соответственно для регистра кода и регистра иерепоса;

34, 35 - спгпалы с едцппчпых выходов еоответствепно первого разряда репгстра кода и нерепоеа;

На фнг. 3 цредетавлепы сигналы 38-45,

аналогичные еигналам на фиг. 2 за исключеиие.м 40-41, которые еоответствуют сигналам

усилнтелей, унравляющих вычнтапием едпнииы (7, 8.

Уетройство работает следующим образом. Пуеть в некоторый полутакт t срабатывает чгилнтель 6 еложепня е единнцей для регистра переноса (эпюра 33 па .фиг. 2), от которого

устанавливается усилитель 5 сложения с едпннцей для регистра кода (32 на фиг. 2), от последнего устанавливается первый разряд 1)егпетра кода (34, фпг. 2) в один нз поеледукшгих нолутактов, начиная е /2 появляется пара управляющнх спгналов 32 и 33, от которых срабатывает нервый разряд региетра переноеа (о5, фнг. 2), сбрасывается первый разряд регистра кода (34, фпг. 2) ц устанавливается второй разряд регнстра кода (36, фиг. 2).

Пусть, начиная с момента /л вновь срабатывает нара усилителей 6 и 5 (33 п 32, фпг. 2), от которой устапавл 1вается первый разряд регпетра кода (34, ф.иг. 2). Аналогпчпо с мо.мента /. приходит последпяя пара еигналов 32, 33

(см. фиг. 2), от которой срабатывают первый (35, фиг. 2) и второй (37, фиг. 2) разряды регистра переноса, которые сбрасывают первый (34, фиг. 2) и второй (36, фиг. 2) разряды |)егиетра кода. Моменты t - /4 выбраны произвольпо, между /.з - 4 взят .минимальный иптервал поступления управляЕопднх еигналов 32 и 33.

Таким образо.м, еели в некоторый нолутакт (иервая фаза тактирования) для еложения с единицей код регистра кода .мо/кет быть представлеп как

.XX... Х01...1, / 0,1...л (А -О или 1), то на ре40 С

гиетре переноса устанавливается код п

00...001...1, г 0,1,... п, во вре.мя еледующего г

полутакта (вторая фаза тактирования) па реriicTpe кода устанавливается результат п

50 XX...X 10...О, / 0,1,... п. Ti

Для вычитания единицы, если код на региетре кода .может быть предетавлен как 55п

XX...X 10...О, ( 0,1... п, то па регистре переноi

са в пекоторый полутакт (первая фаза тактпровапия) устанавливается код п

гистре кода устанавливается результат

ХХГ.ЗГОД i 0,1,... п. i

Схемы «И и «ИЛИ реализуют эту логическую функцию следующим о-бразом.

Если /-разряд регистра переноса в нуле, а (/-1)-разряд регистра переноса в единице, то при сложении с единицей;

/-разряд регистра кода устанавливается в единицу;

если /-разряд регистра переноса в единице, то при вычитании единицы /-разряд регистра кода устанавливается в единицу;

если (/- 1)-разряд регистра переноса в нуле, то он поддерживает единичное состояние /-разряда регистра кода.

Предмет изобретения

Реверсивный двоичный счеТчик, содержащий регистр кода, логические элементы «И и «ИЛИ, управляющие усилители сложения и вычитания и генератор импульсо в, отличающийся тем, что, 1C целью сокращения времени работы, он содержит регистр кода и регистр переноса, выполненные на парафазных элементах с управлением от двухфазного тактирующего генератора, причем единичный выход каждого разряда регистра кода соединен со входами двух (первой и второй) из четырех

схем «И, связанных через схему «ИЛИ со входом эт0:го же разряда, а также соединен в этом и более старщих разрядах регистра переноса со входом второй схемы «И, одной из трех, связанных через схему «ИЛИ со входс.м этого разряда; нулевой выход каждого разряда регистра кода соединен со входом третьей схемы «И того же и более старших разрядов регистра переноса; единичный выход каждого

разряда регистра переноса соединен со входом первой схемы «И данного разряда, а также со входами третьей схемы «I-i в этом разряде регистра кода и четвертой схемы «И в следующем; нулевой выход регистра переноса соединен со входом четвертой «И того же разряда и 1входом второй схемы «И следующего разряда регистра кода; выход усилителя сложения единицы одной фазы соединен со входом четвертой схемы «И калчдого разряда регистра кода, а выход усилителя сложения единицы другой фазы - со входом второй схемы «И каждого разряда регистра переноса; аналогично выход усилителя вычитания единицы одной фазы соединен со входом третьей

схемы «И регистра «ода, а выход усилителя другой фазы - со входом третьей схемы «И регистра переноса; выход тактирующего генератора одной фазы соединен с одним из входов всех схем «И регистра «ода, кроме нервой, и со входом первой схемы «И регистра переноса, а выход генератора другой фазы соединен с одним из входов всех остальных схем «И счетчика.

а Rsass ss

г сосо с со

о-,

е

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬ ФУНКЦИЙ СИНУСА И КОСИИУСА | 1971 |

|

SU419896A1 |

| ДВОИЧНО-ДЕСЯТИЧНОЕ СУММИРУЮЩЕЕ УСТРОЙСТВО | 1968 |

|

SU220631A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| СПЕЦИАЛИЗИРОВАННОЕ ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU408304A1 |

| Устройство управления доступом | 1986 |

|

SU1423816A1 |

| Реверсивный двоичный счетчик с контролем | 1978 |

|

SU752339A1 |

| Устройство для измерения перемещений | 1990 |

|

SU1784836A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1242936A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

Авторы

Даты

1969-01-01—Публикация