1

Предложение относится к автоматике л вычислительной технике и нредназначено для вычислительных устройств последовательного действия.

Известен иоследовательный преобразователь двоично-десятичното кода в двоичный, содержащий регистры, сумматоры, элементы задержки н логические элементы. Устройство основано на исиользовании алгоритма

+ ,... , + +

+ ,...,a, ,

где q - основание системы счисления; L - номер разряда;

разрядов целой части числа;

п - число разрядов дробной части чиш - число

ела; О; - целые положительные числа от иуля до q-1, показываюгцие сколько

едииии г-ого разряда содержится в

числе.

Предложенный преобразователь отличается тем, что в нем выход первого сумматора, один вход которого служит входом преобразователя, через элемент совпадения, соединенный со входом управления циркуляцией, связан с регистром сдвига и через элемент совпадения, соединенный со входом унравления преобразoвaIIиe, подключен к иервому входу второIo сумматора, а через указанный элемент совпадения и элемент задержки - ко второму входу второго сумматора, выход которого 5 присоединен также к регнстру сдвш-а, иодключснному ко второму входу первого сумматора.

Это поззоляет упростить устройство и повысить быстродействпе.

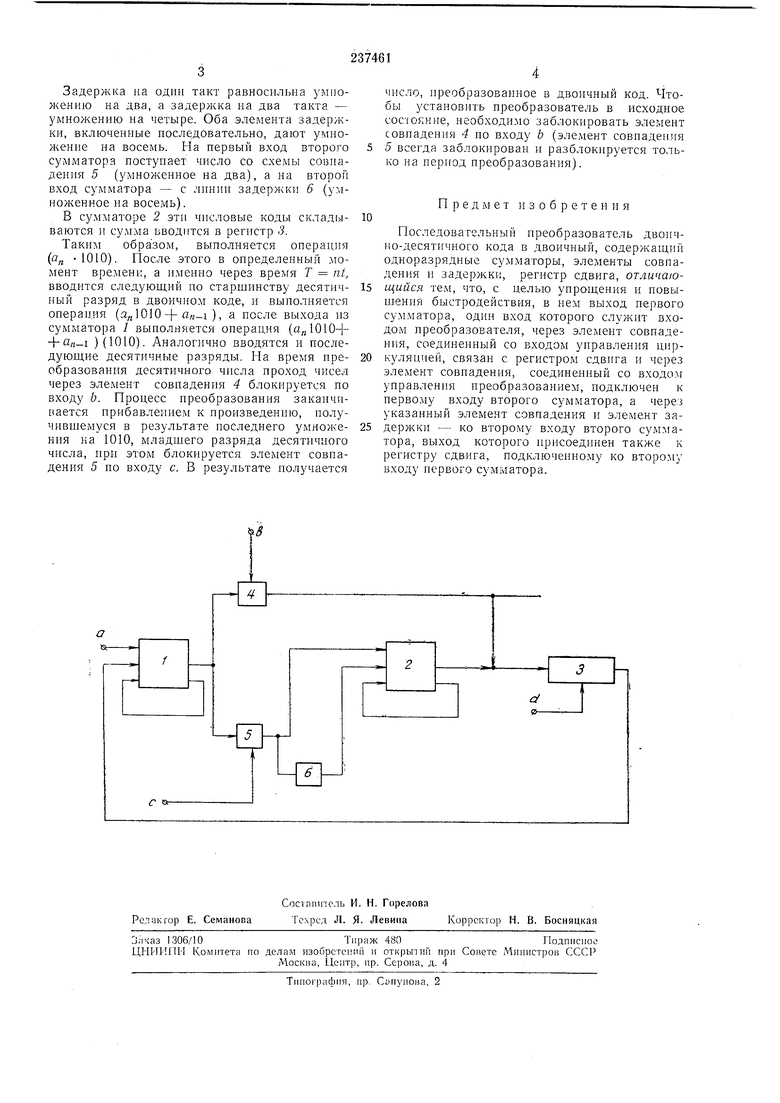

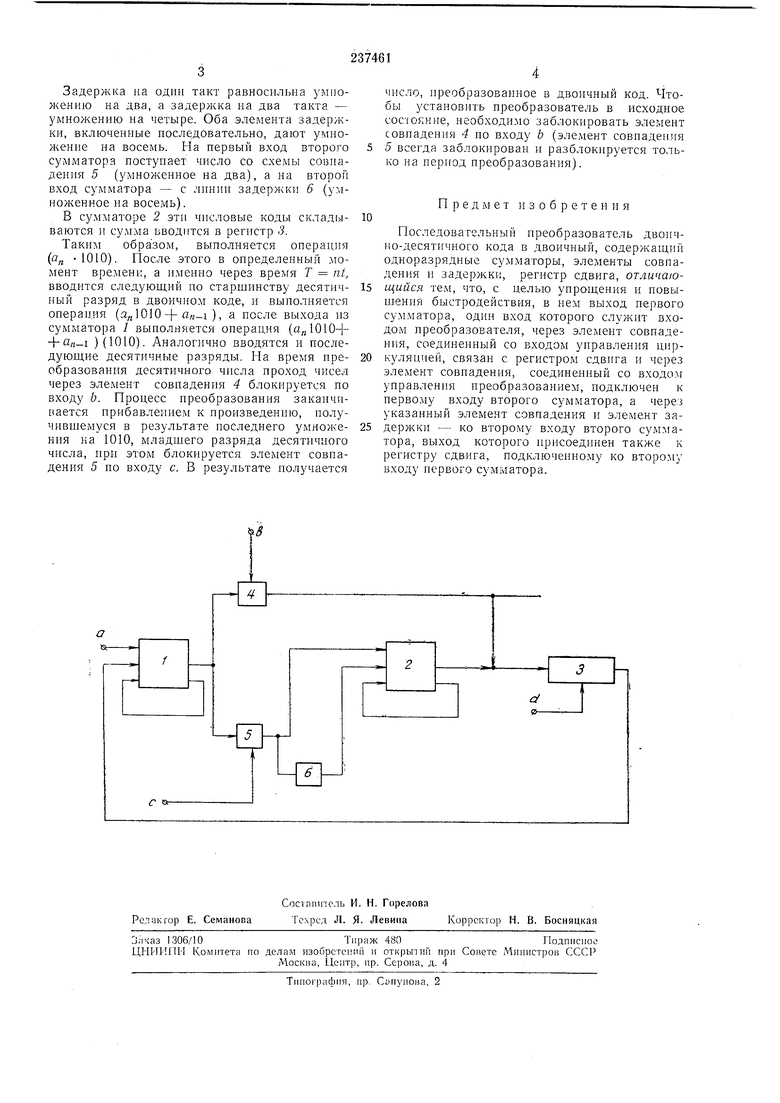

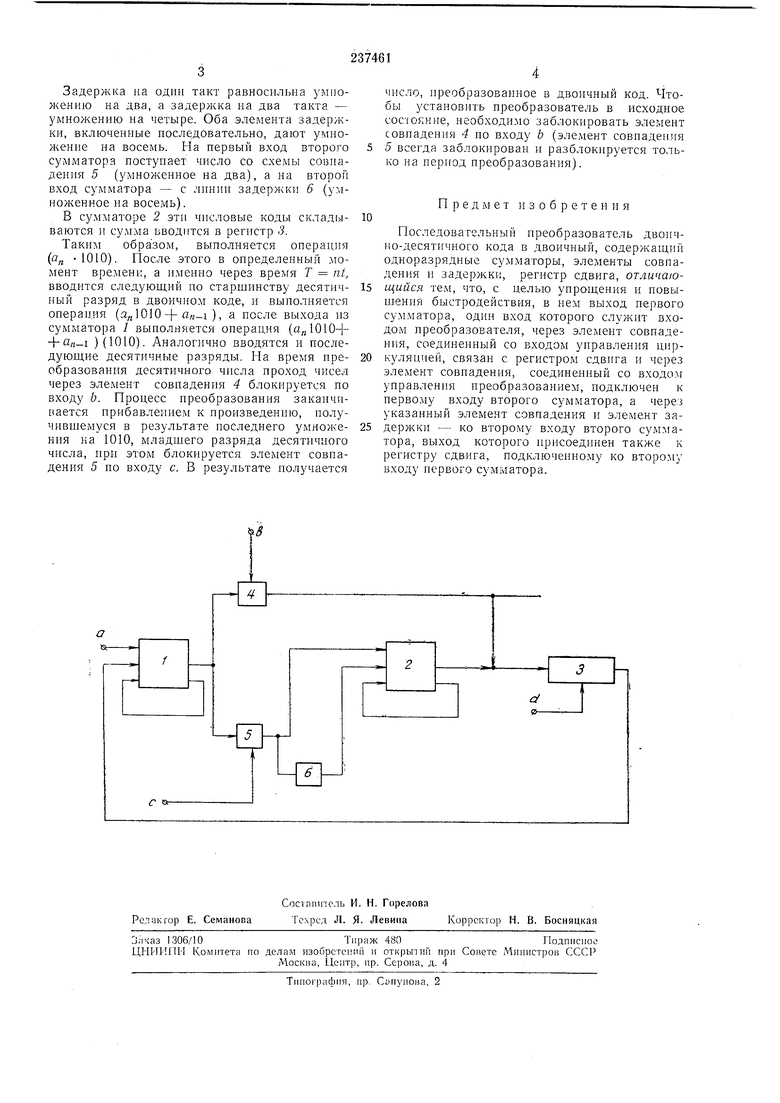

0 На чертеже изображеиа схема предложенного преобразователя.

Преобразователь содержит одноразрядные сумматоры 1 и 2, регистр 3 сдвига, элементы совиадения - и 5 и элемент задержки 6. Па

5 вход а подаются разряды десятичного числа, на вход b - сигналы управления циркуляциeii числа в преобразователе, на вход с - сигналы управления преобразованием числа и на вход d - импульсы сдвига.

0 Перед началом работы сумматоры, элемеиты совиадения и регистр сдвига устаиавливаются в исходное состояние. Работа начинается с иодачи в преобразователь на вход а старшего разряда десятичного числа в двоичном

5 коде. Ма вывода числа из су.мматора / поставлены элемент совиадения 5, разрен а1оmuii преобразование и одновременно выполняющий роль задержки на одци гакт, элемент задержк 6, задерживающий число на два

Задержка на один такт равносильна умножению на два, а задержка на два такта - умножению на четыре. Оба элемента задержки, включенные иоследовательно, дают умножение на восемь. На первый вход второго сумматора постунает число со схемы совпадения 5 (умноженное на два), а па второй вход сумматора - с лпнпп задержки 6 (умноженное на восемь).

В сумматоре 2 эти числовые коды складываются н сумма вводится в регистр 3.

Таким образом, выполняется операция (Од -1010). После этого в определенный момент времени, а нменно через время Т nt, вводится следующий по старшинству десятичный разряд в двоичном коде, н выполняется операция ( + ), а после выхода цз сумматора 1 выполняется операция (а„1010Н+ )(1010). Аналогично вводятся и последующие десятичные разряды. На время преобразовапия десятичного числа проход чисел через элемент совпадения 4 блокпруется по входу Ь. Нроцесс преобразования закапчивается прибавлением к произведению, иолучивше1муся в результате иоследнего умножения на 1010, младшего разряда десятичного числа, при sTOiM блокируется элемент совиадения 5 по входу с. В результате получается

число, преобразованное в двоичный код. Чтобы установить преобразователь в исходное состо57нне, необходимо заблокировать элемент совиадения 4 по входу b (элемент совпадения 5 всегда заблокирован и разблокируется только на нериод преобразования).

Предмет изобретения

Последовательный преобразователь двоичFio-десятнчного кода в двоичный, содержащий одноразрядные сумматоры, элементы совпадения и задержки, регистр сдвига, отличающийся тем, что, с целью упрощения и повыnjeHHH быстродействия, в нем выход первого сумматора, один вход которого служит входом преобразователя, через элемеит совпадеиия, соединенный со входом управления циркуляцией, связан с регистром сдвига и через элемент совиадения, соединенный со входом управления преобразованием, подключен к первому входу второго сумматора, а через указанный элемент совпадения п элемент задержки - ко второму входу второго сумматора, выход которого присоединен также к регистру сдвига, подключеппому ко втором} входу первого сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР С ПЕРЕКЛЮЧАЕМОЙЛОГИКОЙ | 1969 |

|

SU256014A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU723567A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU699520A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА ПРАВИЛЬНОЙ ДРОБИ В ДВОИЧНО-ДЕСЯТИЧНЫЙ КОД | 1971 |

|

SU302714A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ | 1972 |

|

SU356642A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ В ДВОИЧНЫЕ | 1970 |

|

SU269598A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1962 |

|

SU717754A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь позиционного кода с одним основанием в позиционный код с другим основанием | 1977 |

|

SU734667A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

Авторы

Даты

1969-01-01—Публикация