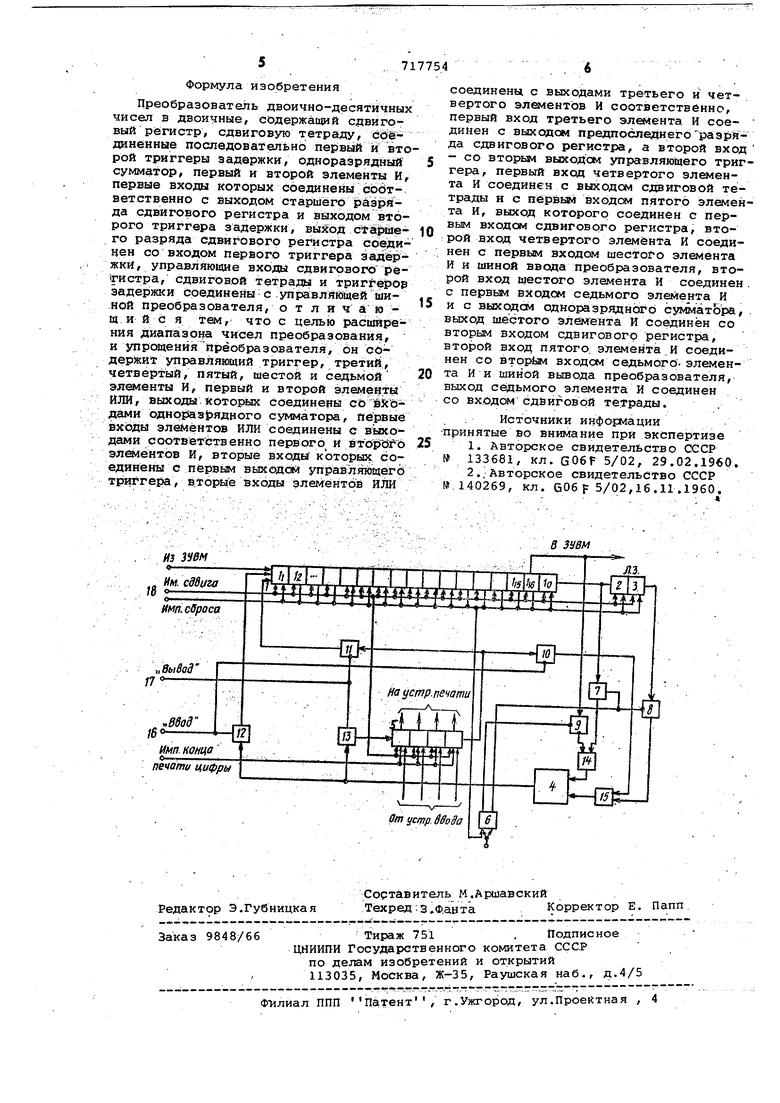

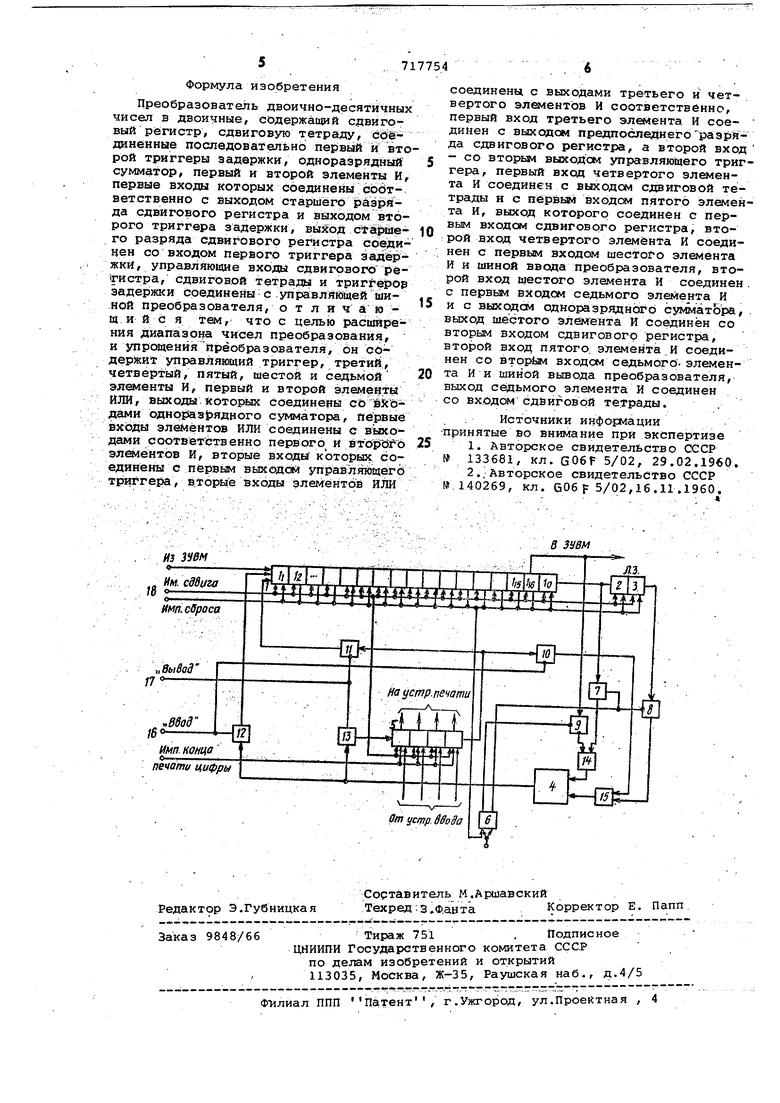

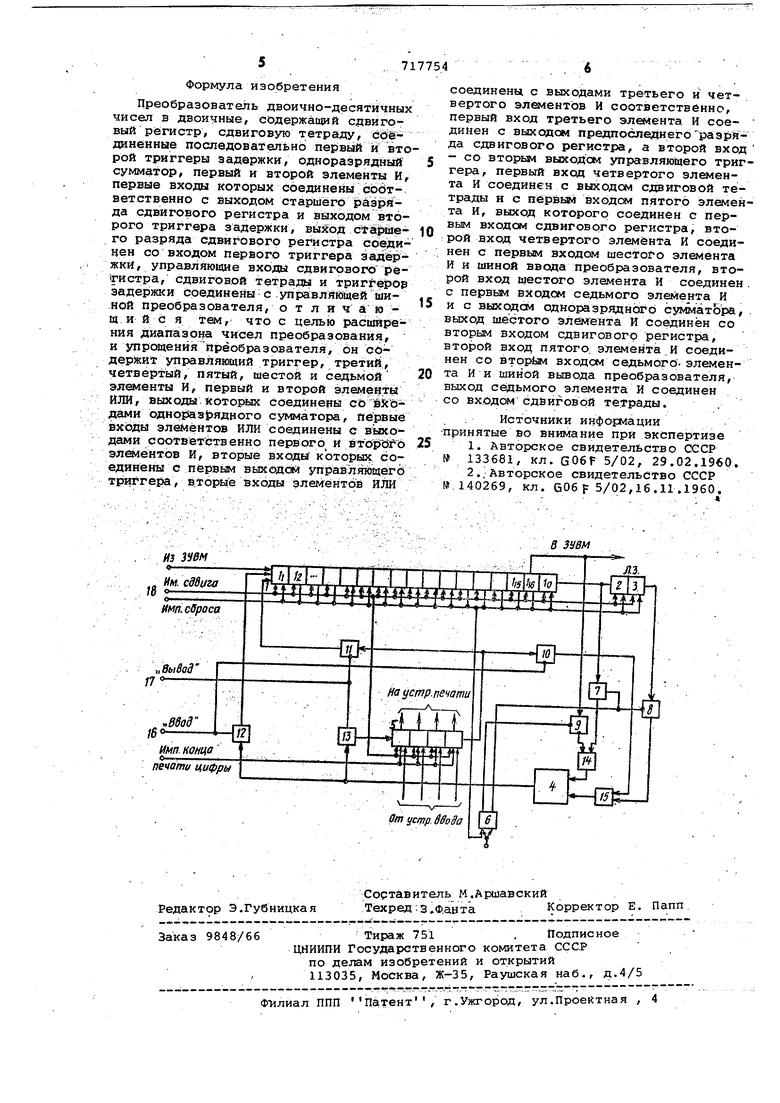

(54) ПРЕОБРАЗОВАТЕЛЬ | ВОИЧНО-ДЕСЯТМ1Ш ЧИСЕЛ В ДВОИЧНЫЕ входы элементов ИЛИ соединены с выходами соответственно первого и второго, элементов И, вторые входы которых соединены с первым выходом управляющего триггера, вторые входы Элем нтов ИЛИ соединены с выходами третье и четвертого элементов И соответстве но , первый вход третьего элемента И соединен с выходом предпоследнего ра ряда сдвигового регистра, а второй , вход - со вторым выходом управляющего триггера, первый вход четвертого элемента И соединен с заыходом сдвиговой тетрады и с первым входом пя-. того элемента И, выход которого соединен с первым входом сдвигового регистра, второй вход четвертого эле мента И .йоединей с первым йХбдом шес того элемента И и шиной ввода преобразователя, второй вход шестого элемента И соединен с первым входом седьмого элемента И и с выходом одноразрядного сумматора, выход шестого элемента И соединен со вторым вхо дом сдвигового регистра, второй вход 1;пятрго элёмейта И соединен со вторым входом седьмого элемента И и шиной вывода преобразователя, выход седьмого элемента И соединен со входом : сдвиговой тетрады-. . . . . . . , Блок-схема пр г а емогр устройства представлена на чертеже со следу ющими позициями. Сдвиговый регистр 1, триггеры задержки 2,3, одноразрядный сумматор 4 сдвиговая тетрада 5, управляющий триг гер 6, элементы И 7 - 13, элементы ИЛИ 14 - 15, шина ввод -.16 шй-; на вывод -т 17, шина импульсов , сдвига - 18. ... .:,:--%,--:.;; .;:;,;;:;: :;.г -;;::,;: : Первый выход сдвигового регистра 1 соединен со входом первого триггера задержки 2 и входом первогр элемента И 7. Выход второго триггера задержки соединен со входом, второго элемента И 8. Второй выход сдвигового регистра 1 соединен со входом .-трёт его элемента И 9, Первые.йхолы четвертогр и пятого элементов И 10 11 соединены с выходом сдвиговой teтрада. -Входы шестого и седьмого элементов И 12 - 13 соединены с выходом . одноразрядного сумматора 4, входы которого соединены с выходами первого и второго-элементов ИЛИ 14-154 Г Перевод целых десятичных чисел- в двоичные производится согласно слёдунзщёto выражения - ;-- Мп-°° -«-1°° где N двоичное число, а цифра i-го разряда двоично-десятичного -числа, п- - номер разряда. Предлагаемое устройство работает следующим образом. -- -. - -: Сигналом по шине ввод16 откр в|1ются элементы И 4,12. При помощи устройства ввода (на чертеже не показано) в сдвиговую тетраду 5 заносится значений старшего разряда двоично-десятичного числа. Посредством импульсов сдвига число из сдвиговой тетрады 5 через элемент И 10 и элемент ИЛИ 15 подается на вход одноразрядного сумматора 4.На второй вход сумматора череэ элемент И 9, открытый потенциалом с выхода триггера б, и элемент ИЛИ 14, подается содержимое сдвигового регистра {periidxp перед началом преобразования обнуляется) . С выхода сумматора число поступает через элемент И 12. на вход сдвигового регистра 1. В следующем цикле производится умножение занесенного в регистр 1 числа наЮЮ. Для ЭТОГО управляющий триггер 6 переводится в состояние нуля и открывает элементы И 7,8, через которые число из регистра подается в .сумматор по двум цепям со сдвигом на один и три разряда. Сложение в сумматоре 4 . сдвинутых таким.образом чисел равносильно умножению на 1010. Далее описанный процесс повторяется для последуюида;х Цифр числа. После ввода последней цифры числа происходит блокировка умножения на ЮДО (цеп11 блокировки на чёр-тежё йе7показаны) . - ; : ..-., Преобразование двоичной дроби в двоично-десятичную происходит при поступлении сигнала вывод по шине 17, который открывает элементы И 11, 13. Сначала двоичная дробь заносится в сдвиговый регистр 1. Затем при помощи импульсов сдвига она поступает в одноразрядный сумматор 1, при этом, производится умножение на 1010. Получаемый результат с выхода сумматора 4 через элемент И 13 поступает в сдвигающую тетраду и через элемент И 11 с выхода тетрады вход регистра. После окончания сдвига в тетраде фиксируется эквивалент первой десятичной ЦИфрЫ. . ,.;,., Процесс преобразования продолжается до получения нужного числа разрядов. Циклический процесс перевода чисел позволяет использовать для построения преобразователей наряду со статическими так же и диналдаческие регистры. В этом случае осуществляется непрерывное Циркулирование преобразуёШгокода по цепи регистр, триггеры задержки, сумматор при выработке импульсов выбора тетрад, и импульсов сдвига ... ., Таким образом, предложенное устройство позволяет производить как перевод двоично-десятичных чисел в двоичные, так и обратное преобразование двоичной дроби в двоично-десятичную форму. Предлагаемое устройство позволяет также сократить объем аппаратуры двоично-десятичных преобразователей, поскольку исключает один из сумматоров известных устройств. Формула изобретения Преобразователь двоично-десятичных чисел в двоичные, содержащий сдвиговый регистр, сдвиговую тетраду, соединенные последовательно первый и вто рой триггеры задержки, одноразрядный сумматор, первый и второй элементы И, первые входы которых соединены собтветственно с выходом старшего раэрйда сдвигового регистра и выходом второго триггера задержки, стЖЬше го разряда сдвигового регистра соединен со входом первого триггера aajjiepжкй, управляющие входы сдвигового ре гистра, сдвиговой тетрады и триггеров задержки срединейы с .уп йвляйщей шиной преобразователя, о т л и ч а ю И и и с я тем, что с целью расширения диапаз оча чисел преобразования, и упрощения преобразователя, он содержит управлякздий триггер, третий, четвёртый, пятый, шестой и седьмой элаленты И, первый и второй элементы ИЛИ, выходы йоторых соединены со sk6дами однргй13| ядиого сумматора, первые Входы эл(й ёнтов ИЛИ соединены с выходами соответственно первого, и втОрозГО элалёнтов И, вторые входы которых соединены с первым выход 4 управляйщегб триггера, B.ToptJe входы элемёнтбй ИЛИ соединены с выходами третьего и четвертого элементов И соответственно, первый вход третьего элемента И соединен с выходом предпоследнегоpaspiHда сдвигового регистра, а второй вход - со вторьм выходом управляющего триггера, первый вход четвертого элемента и соединен с выходом сдвиговой тетрады и с первым входсм пятого элемента и, выход которого соединен с первым входом сдвигового регистра, второй вход четвертого элемента И соединен с первым входом шестого элемента И и шиной ввода преобразователя, второй вход шестого элемента И соединен . с первым входом седьмого элемента И и с выходсм одноразрядного сунадатЬра, выход шестого элемента И соединён со вторьм входом сдвигового регистра, второй вход пятого, элемента ,и соединен со вторЬм входом седьмого, элемента И и шиной вывода преобразователя, выход седьмого элемента И соединен со входом сдвиговой тетрады. Источники информации принятые во внимание при экспертизе 1.Авторское свидетельство CGCP № 133681, кл. G06F 5/02, 29.02.1960. 2.Авторское свидетельство СССР №.140269, кл. G06F 5/02,16.11.I960.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичных чисел в двоичные | 1978 |

|

SU742924A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для преобразования двоичныхчиСЕл B дВОичНО-дЕСяТичНыЕ | 1979 |

|

SU809153A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1975 |

|

SU634267A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

Авторы

Даты

1980-02-25—Публикация

1962-08-13—Подача