Изобретение относится к вычислительной технике и предназначено для преобразования кодов.

Известен преобразователь двоичного кода правильной дроби в двоично-десятичный код, содержащий сдвиговый регистр, одноразрядный двоичный сумматор, схему задержки, регистр свободных разрядов, элементы и «Запрет и распределитель, число разрядов которого зависит от числа разрядов преобразуемого кода.

Предложенное устройство отличается тем, что распределитель содержит четыре разряда, причем выходы всех разрядов соединены с одннм из входов элемента «И и с запрещающим входом элемента «Запрет, со вторыми входами которых соединен выход одноразрядного двоичного сумматора, а выход элемента «Запрет через регистр свободных разрядов соединен со входом сдвигового регистра.

Это позволяет упростить схему устройства и расщирить его функциональные возможности.

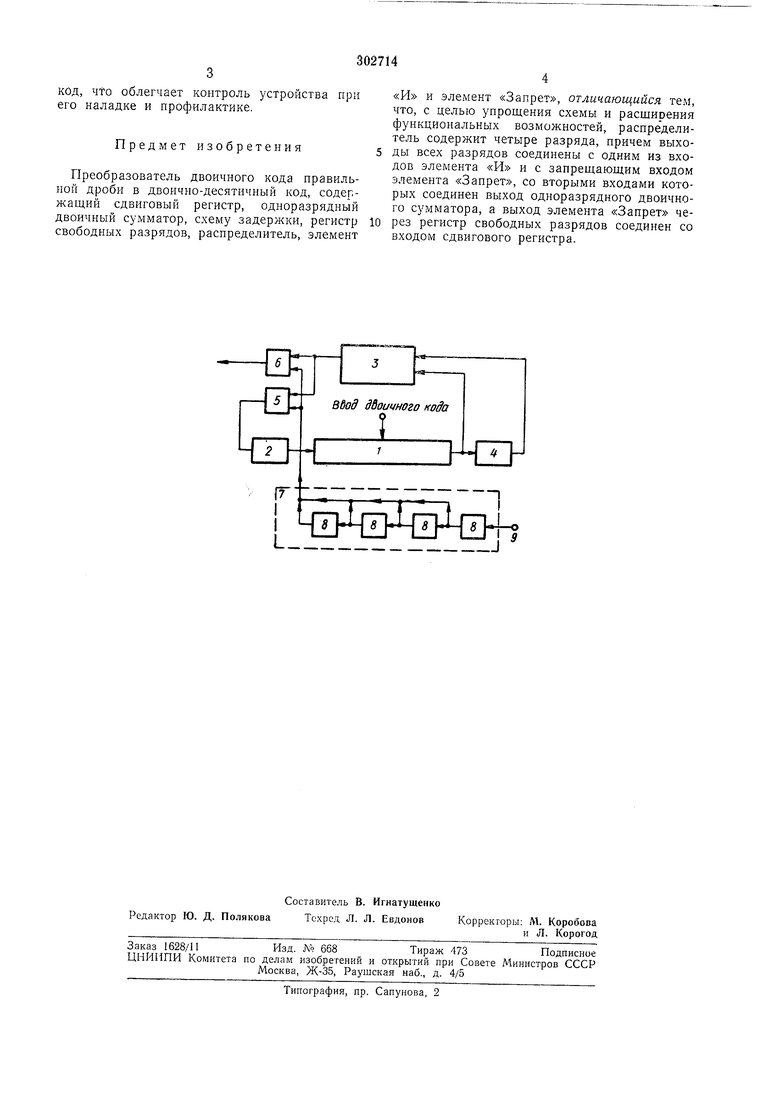

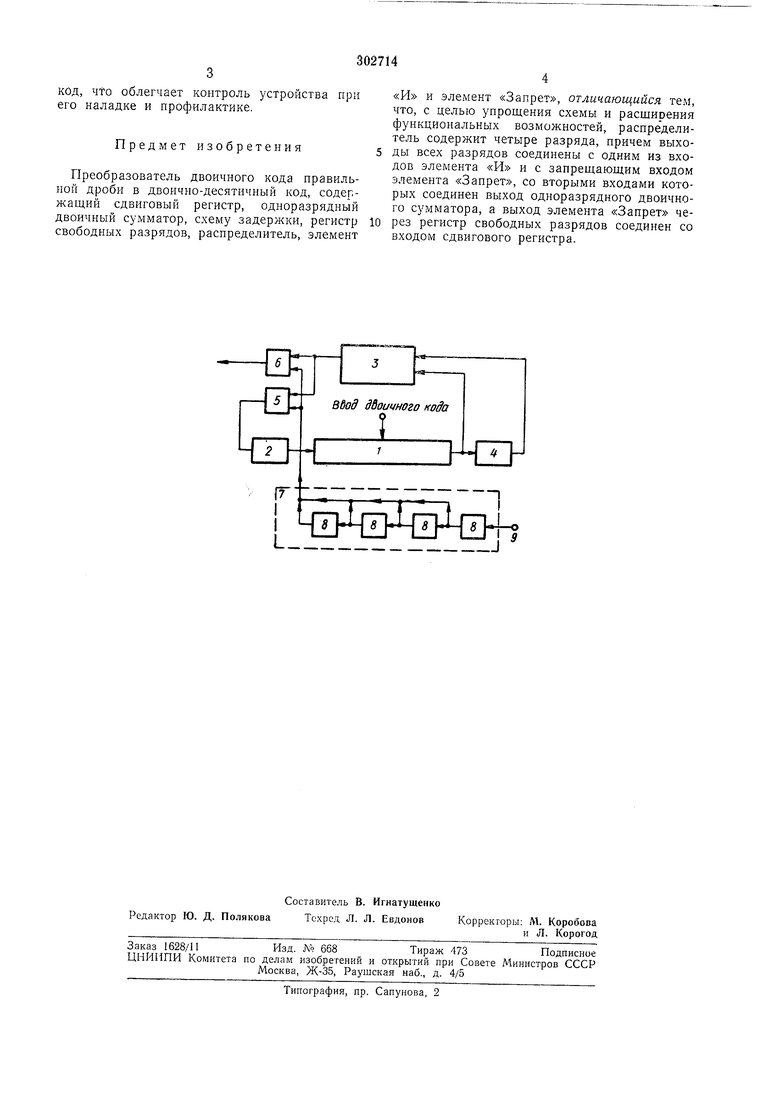

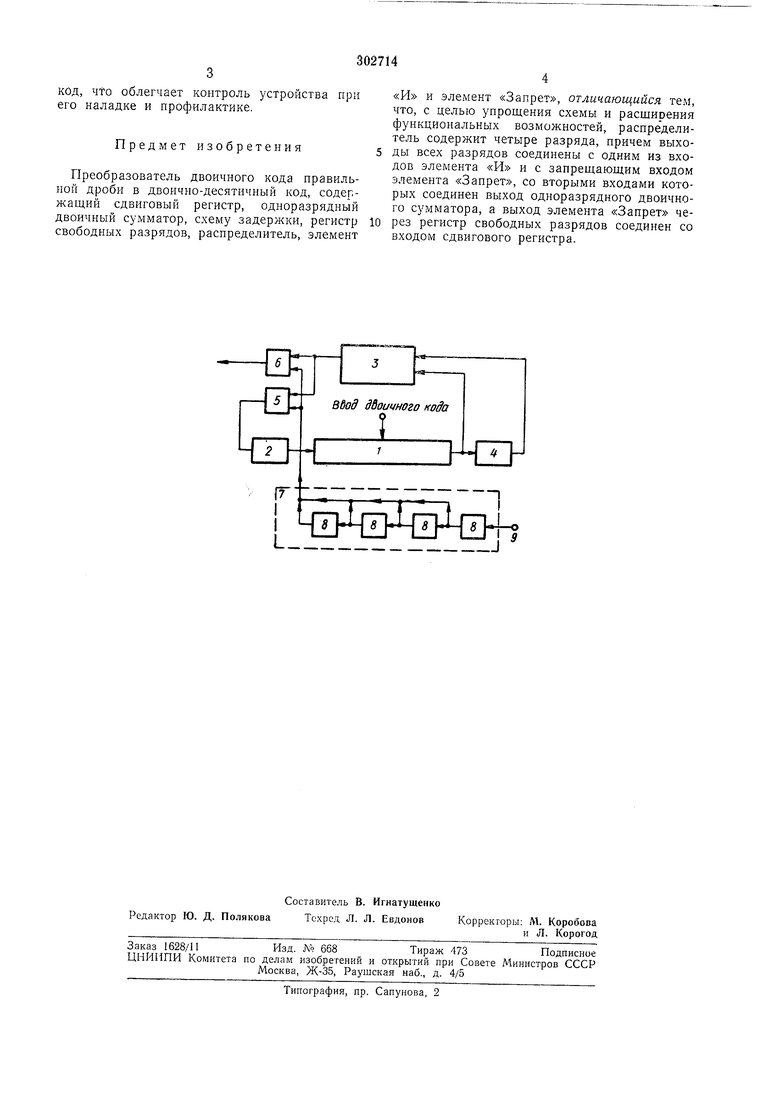

Схема устройства показана на чертеже.

Устройство содержит сдвиговый регистр 1, регистр 2 свободных разрядов, одноразрядный двоичный сумматор 3, схему 4 задержки кода на два разряда (такта), элемент «Запрет 5 (отрицание импликации), элемент «И 6, распределитель 7 управляющих импульсов, выполненный на четырех разрядах 8, в качестве которых могут быть использованы любые накопительные элементы, с щнной 9 управления.

Принцип работы устройства основан на умножении мантиссы преобразуемого числа (а в дальнейщем - остатка) на десять (в двончHGM выражении-1010). Умножение выполняется с помощью одноразрядного двоичного

сумматора 3 и схемы 4 задержки, осуществляющей сдвиг кода на два разряда. Преобразованные двончко-десятичные разряды снимаются с выхода элемента «И 6, а возвращение преобразуемого кода в регистр 1 через

регистр 2 осуществляется с помощью элемента «Запрет 5.

Такое построение схемы позволяет использовать четырехразрядный распределитель 7 управляющих импульсов (при любом числе

разрядов мантиссы), который серией из четырех импульсов управляет элементами 5 и 6. При этом на элементах «И 6 происходит выделение двоично-десятичного разряда, а на элементе «Запрет 5 - стирание его (запрсщение), и затем код остатка и вводится обратно в регистр /. Кроме того, после окончания преобразования, когда распределитель 7 управляющих импульсов перестает генерировать импульсы управления, в числовом регистре /

код, что облегчает контроль устройства при его наладке и профилактике.

Предмет изобретения

Преобразователь двоичного кода правильной дроби в двоично-десятичный код, содержащий сдвиговый регистр, одноразрядный двоичный сумматор, схему задержки, регистр свободных разрядов, распределитель, элемент

«И и элемент «Запрет, отличающийся тед1, что, с целью упроасения схемы и расширения функциональных возможностей, распределитель содержит четыре разряда, причем выходы всех разрядов соединены с одним из входов элемента «И и с запрещающим входом элемента «Запрет, со вторыми входами которых соединен выход одноразрядного двоичного сумматора, а выход элемента «Запрет через регистр свободных разрядов соединен со входом сдвигового регистра.

«, ввод дбоичного кода

H-DtZH

Даты

1971-01-01—Публикация