Предложение относится к области ВЬГЧЕСЛЕгельной техники и предназначено для преобразования кодов.

Известен преобразователь двоичного кода в двоично-десятичный, содержащий сдвиговый регистр, (Последовательный сумматор, схаму задержки на два разряда и схему управления. Время преобразо1ва«ия д-разрядного двоичного кода равно

T N()t,

где Л - количество двоично-де сятич,ных тетрад; . t - длительность одного такта.

Предложенное устройство отличается тем, что выход каждого (п- -1-3/с)-го разряда (я+1)-разрядного сдвигового perHiCTpa (где , 1,2, 3,...) через соответствующий элемент «И ооединен со входом первой собирательной схемы, выход которой соединен с первым входом одноразрядного последовательного сумматора, выход каждого (п.-2-3/с)-го разряда (п-2)-разрядного сдвигового регистра через соответствующий элемент «И соединен со входо М второй собирательной схемы,, выход Которой соединен ico вторым входом одноразрядного последовательнаго сумматора. Входы элементов «И соединены с выходами соответствующих разрядов распределителя, ЧТО позволяет уменьшить время преобразования кодов.

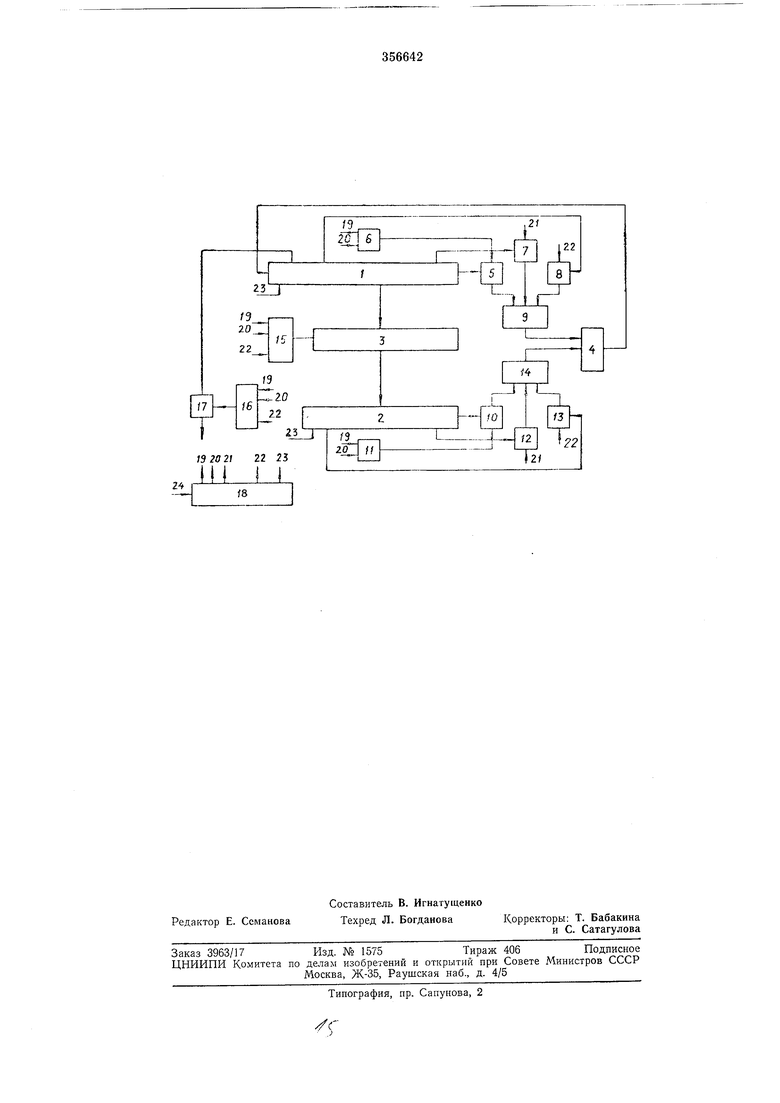

Н.а чертеже изображена схема устройства.

Устройство содержит (и+1)-разрядный сдвиговый регистр 1, (п-2)-разрядный сдвиговый регистр 2, вентили записи 3, одноразрядный последовательный сумматор 4, элементы «И 5-8, собирательную схему 9, элементы «И 10-13, собирательн|ую схему 14, элементы «ИЛИ 15 и 16, выходные вентили 17, распределитель 18 с выходами 19-23 и со входом 24 команды «преобразование.

Работа предложенного устройства основана на алгоритме, в котором при нреобразовании двоичного числа

А a/fe-2 + ft-i + ,..., + Ci -24- а, -2

В десятичное число производится последовательное умножение числа А и его остатков (после выделения целой части числа) на основание 10 в двоичной системе счисления, т. е. на 1010. Образующиеся при эточм целые

части будут тетрадами двоично-десятичного кода.

Устройство работает следующим Обр:азом.

В исходном состоянии преобразуемое, пПо сигналу со входа 24 (команда «преобразование) за1пу:ска1ется распределитель 18, который начинает выра1батывать имяульсы улравления. iOo первому импульсу у/правления с выхода 19ЧИСЛО из регистра 1 через вентили записи 3 переписывается в регистр 2 сдвинутый на два разряда влраво (,в сторону младших разрядов). Серия из (п+) импульсов сдвигает числа в регистрах / и 2 через элементы 5 и 10, собирательные схемы 9 я 14 н.а входы сумматора 4. Сумма записывается в регистр 1 в разряды с первого ло (д+1)-й. Первая тетрада, т. е. первый разряд выходного двоИЧ,но-десятичного кода, считывается через вы-15 ходные вентили 17, лосле чего происходит установка IB нуль триггеров этой тетрады. nio второму И1М1пульсу управления с въиода 20оставшаяся часть числа (без четырех старших разрядов) переписывается в регистр 220 через вентили записи 3. Серия из (я+1) п-2 импульсов сдвигает числа из регистров / и 2 через те же элементы «И 5 и 10, собирательные схемы 9 н 14 на входы тора 4, а результат записывается в регистр /25 в разряды с лервого но (п-2)-и. Первая тетрада вновь лолученной су1ммы считывает ся ;через вентили 17, а серия из (п-5) имяульсов сдвигает содержимое рег-истр.а / (без четырех старших разрядов) и. ре-30 гистра 2 через элементы «И 7 и 12, а результат сум.мирования запишется в регистр 1 в разряды с первого по (п-5)-и. В (Последующие такты будет вырабатываться (п-8), (п-1),..., ( к) импуль-35 сов (, 1, 2, 3 ...), т. е. в каждом лоследующем такте на три импульса сдвига меньте, чем в предыдущем такте. В последнем такте будет вырабатываться четыре импульса сдвига, если число разрядов40 преобразуемого кода четное, или лять имлульсов сдвига, если число разрядов преобразуемого кода нечетное. Время преобразования «-разрядного двоичного кода T - (N - 1)3/ :: Nt(n - 3) + 3. Предмет изобретения Преобразователь двоичиого иода в двоично-десятичный, содерж-ащий («4-1)-,разрядный сдвиговый регистр при преобразовании «-разр|Ядного кода, выход каждого i-ro разряда этого регистра (KpiOMe двух младших разрядов) соедиден через соответствующий вентиль записи со входом (t-2)-гО разряда (п-2)-разрядного сдвигового регистра, а выходы старших четырех разрядов (/г+1)-ра,зрядного сдвигового регистра соединены с выходными вентилями, другие входы которых соединены с выходом первого элемента «ИЛИ, входы которого соединены с выходами распределителя, соединенными также со входами второго элемента «ИЛИ, выход которого соединен со вторыми входами вентилей записи, а вход (/г+1)-разрядного одвигового регистра соединен с выходом одноразрядного лo cлeдoвaтeльнl0гo сумматора, отличающийся тем, что, с целью уменьшения времени преобразования, выход каждого (п+1-3/с)-го разряда (и+1)-разрядного сдвигового регистра (где , 1,,2, 3...) через соответствуюший элемент «И соединен со входом первой собирательной схемы, выход которой соединен с первым входом одноразрядного последовательного су)мматора, выход каждого (п-2-3«:)-го разряда (п-2)-разрядного сдвигового регистра через соответствующий элемент «И соединен со входом второй собирательной схемы, выход которой соединен оо вторым входом однор-азрядного последовательного сумматора, входы элементов «И соединены с выходами соответствующих разрядов распределителя.

Даты

1972-01-01—Публикация