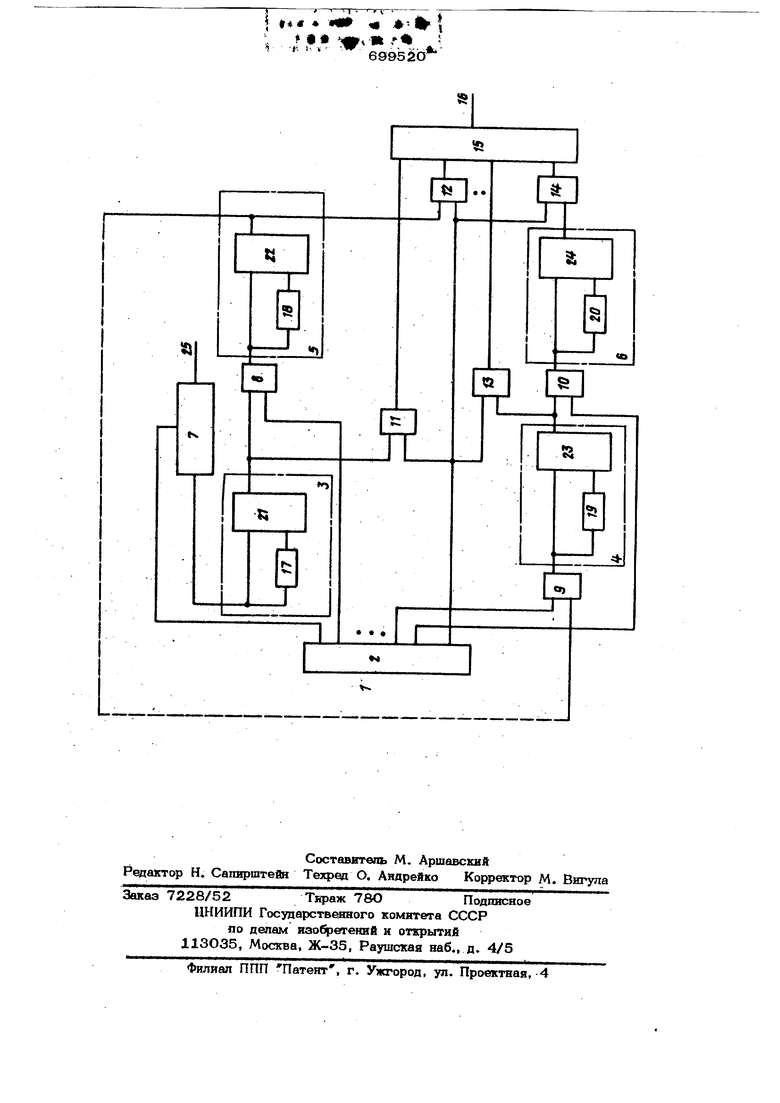

Изобретение касается автоматики и цифровой вычислительной техники,и может быть использовано при построении устройств преобразования информации. Известно устройство для преобразования двоичного кода в двоично-десятичный, содержащее одноразр5адный двоичный сумматор, регистр сдвига, вход которого соединен с выходом сумматора, а выход со входом сумматора, блок управления, выход которого соединен со входом регист ра сдвига, регистр двоично-десятичного числа, элемент И вьщеления тетрады, выход которого соединен со входом регистрра двоично-десятичного числа l. .Однако, в этом устройстве низко быстродействие, т.к. время преофазования прямо пропорционально числу разрадов двоично-десятичного числа и преофазование повторяется И циклов. Наиболее близким по технической сущности к предложегшому является преобразователь, содержащий регистр сдвига, пер вый одноразрядный блок умножения на десять, вход которого соединен с выходом регистра сдвига, блок управления, первый вькод которого соединен со входом регистра сдвига, первый элемент И вьщеления остатка, первый вход которого соединен со вторым выходом блока управления, первый элемент И вьщеления тетрады, первый вход которого соединен с выходом первого одноразрядного блока умножения на десять и вторым входом элемента И выделения остатка, а второй вход --С третьим выходом блока управления, регистр двоично-десятичного числа, первый вход которого соединен с выходом первого элемента И вьщеления тетрады 2. Недостатком этого устройства является относительно невысокое быстродействие, связанное с необходимостью И циклов преофазования для получешш h -разрядного результата. Цель изобретения - увеличение быстродействия прео азователя. Для этого он дополнительно содержит ( И -1) одноразрядный блок умножения на десять (где ц - число разрядов двоично-десятичного кода), ( Ц -2) элемента И вьщеления остатка, { h-l) элемент И выд(У1ения тетрады, первые входы которых соединены с выходами соответствующ одноразрядных блоков умножения на десять, вторые входы соединены с третьим выхо дом блока управления, а выходы - с соответствующими входами регистра двоично-десятичного числа, первый вход i -г ( i 2-(п-1) элемента И вьщеления остатка соединен с ( i +2)-м выходом блока управления, второй вход соединен с выходом 1 -го одноразрядного блока умножения на дес5пъ, а выход соединен со входом ( V+l)-ro одноразрадного блока умножения на десять. На чертеже изо ажена структурная схема преобразователя. Устройство содержит управляющую ши ну. 1, блок 2 управления, одноразрядные блоки умножения на дес5пъ 3-6, регистр 7 сдвига, элементы И 8-10 вьщеления остатка, элементы И 11-14 вьщеления тетрады, регистр 15 двоично-десятичног числа, выходные шины 16, элементы 17-20 задержки, одноразрядные сумматоры 21-24, входную шину 25. Управляющая шина 1 предназначена для пуска преобразователя. Блок управления 2 вырабатывает psgi последователь ностей импульсов, по и,- - и в ка дой, для вьщеления остатка О и одну последовательность импульсов для вьщеления тетрад двоично-десятичного числа, где i - число разрядов пре образованного числа, П- число разрядов преобразуемого двоичного числа. Элементы задержки 17-2 О на два такта смещают влево информащпо, поступаю щую с предыдущего сумматора. Элементы И выделения остатка 8-10 преднаэначены для вьщеления младших разрядов произведения. Одноразрядньге сумматоры 21-24 суммируют информацию, поступающую на первые и вторые их - входы i регистр 7 сдвига хранит и сдвигает преобразуемое двоичное число. Элементы И 11-14 вьщеления тетрады предназначены для вьщеления i тетрад двоично-десятичного числа одновременно, входная шина 25 предназначена для записи исход ного двоичного числа. Регистр 15 двоич но-десятичного числа хранит преобразованное двоично-десятичное число. Выходные шины 16 предназначены для выдачи преобразованной двоично-десятичной дроби. Для определения тетрад двоично-десятичной дроби в преобразователе используется метод последовательного умножения двоичной дроби на постоянную величину 1О/16, т.е. ОДОЮ, вьщеления-из полученного произведения старших четырех разрядов, представляющих тетраду старшего разряда двоично-десятичной дроби, а младшие разряды произведения вновь умножаются на 0,1010. Предлагаемый преобразователь работает следующим образом. Двоичная дробь, подлежащая преобразованию, вводится в регистр 7 сдвига по входной шине 25 (последовательным или пареллельным кодом), старший разрад У -разрядной двоичной дроби находится во втором справа разряде сдвигающего регистра, младщий разряд в край н&л левом разраде регистра, а первый разрад (справа) регистра, находится в нулевом состоянии. Сигнал, поступающий по управляющей шине 1, запускает устройство управления 2, которое вырабатывает i последовательностей сдвигающих импульсов, поступающие на элементы И 8-1О вьщеления остатка и одну последовательность вьщеления тетрады, поступающую на элементы И 11-14 выделения тетрады. При этом число импульсов в последовательности сдвигакяпих импульсов на каждый последукмций элемент И вьщеления остатка на один меньше и начинается эта последовательность на такт позже последовательности импульсов, поступающих на каткдый предыдущий элемент И вьщеления остатка. Таким образом, последовательность импульсов определяется для каждого элемента И выделения остатка соотношением ПН Последовательность импульсов, портупакхцая на управляющие входы элемента И выделения тетрады 11-14, одна и содержит четьфе импульса ,,, С выхода регистра 7 сдвига разряды , преобразуемой двоичной дроби поступают на вход первого одноразрядного блока 3 умножения на десять, состоящего из двоичного сумматора 21 л первого элемента задер)дси 17. С выхода элемента 17 задержки задержанный на два разряда код двоичной дроби поступает на второй вход того же сумматора 21, С выхода каждого, предьщущего сумматора инфопмапия поступает на первый вход непосредственно и задержанная на два такта - на второй вход последующего одноразрядного сумматора. Поступление информации на каждый последующий сумматор производится на один такт позже (что обусловлено задержкой предыдущего сумматора). С выхода каждого сумматора разрады полученные таким образом сумм соответствуют разрядам произведений преобразуемой двоичной дроби (в первом одноразрядном сумматоре 21) либо остатков QI в последующих на ОДОЮ Через ( 1-1) тактов сдвига происходит выделение последнего остатка произведения. Выделенные элементами И 11-14, начиная со старшей тетрады, записываются в регистр 15 двоично-десятичного числа по соответствующим импульсам из послед оватеяьности .На этом процесс преобразования заканчивается. Вьщача результата производится по выходным шинам 16. В соответствии с вьпыеизложенным слецует, что время преофазования двоичной дроби в двоично- 1есятичную дробь в предлагаемом устройстве определяется соотношетшем

T-i-M

где t - длительность тактирующего импульса.

Следовательно, оно в i раз меньше времени преобразования известного устройства 2. Формула изобретения Преобразователь двоичного кода в двоично-десятичный, содержащий регистр сдвига, первый одноразрядный блок умножения на десять, вход которого соединен с выходом регистра сдвига, блок управления, первый выход которого соединен со входом регистра сдвига, первый элемент

И вьиеления остатка, первый вход которого соединен со вторым выходом блока управления, первый элемент И выцеления тетрады, первый вход которого соединен с выходом первого одноразрядного блока умножения на десять и вторым входом первого элемента И выделения остатка, а второй вход - с третьим выходом блока управления, регистр двоично-десятичного числа, первый вход которого соединен с выход(Ж1 первого элемента И вьщеления тетрады, отличающийся тем, что, с целью увеличения быстродействия преобразователя он дополнительно содержит (п-1) одноразрядный блок умножения на десять (где И - число разрядов двоично-десятичного кода), ( 11-2) элемента И выделения остатка, ( h -1) элемент И выделения тетрады, первые входы которых соединены с выходами соответствующих одноразр51дных блоков умножения на десять, вторые входы соединены с третьим вьрсодом блока управления, а выходы - с соответствующими входами регистра двоичйо-десятичного числа, первый вход i -го ( { 2 ( Ц -1) элемента И вьшепення остатка соединен с ( i + 2) -м выходом блока управления, второй вход соединен с выходом i -го однора ядного блока умножения на десять, а выход соединен со входом ( 1 +1)-го одноразрядного блока умножения на десять. Источники информации, принятые во внимание при экспертизе 1.Сухомлинов М. Н., Выхованец В. И. Перевод десятичных целых чисел в двоичные н двоичной дроби в десятичную. MaTQviaTH4ecKoe моделирование и электрические цепи . Киев, 1967, вьш. 1. 2.Авторское свидетельство СССР Kk 226258, Kn.Q Об F 5/02, 1968.

1 Ji iT i

f t4««« «

« r . 1-. f - .- i699520

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1962 |

|

SU717754A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1975 |

|

SU634267A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоичной дроби в двоично-десятичную дробь | 1978 |

|

SU723568A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU723567A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

Авторы

Даты

1979-11-25—Публикация

1977-07-18—Подача