Техническое решение относится к радиотехнике, радиолокации и может быть использовано в станциях сопровождения для измерения дальности до объектов локации и измерительных приборах для измерения временного положения сигналов.

Известен временной дискриминатор [1, Патент РФ №2042148, 20.08.1995]. Устройство содержит генератор опорных сигналов, три перемножителя, три интегратора, блок вычитания, три сумматора, бинарный квантователь, инвертор, ключи, умножитель и блок деления.

Недостатком устройства является отсутствие блоков преобразования выходного сигнала в цифровой код, что не дает возможности напрямую сопрягать устройство с блоками цифровых следящих систем.

Известен также цифровой дискриминатор задержки [2, Патент РФ №2059254, 27.04.1996], состоящий из согласованного фильтра, аналого-цифрового преобразователя (АЦП), блока задержки, сумматора, блока выделения огибающей сигнала и решающего устройства.

Недостатком устройства является то, что АЦП не включен в замкнутый контур следящей системы, а сигнальный вход дискриминатора нецелесообразно делать цифровым, так как это потребует высокоточного аналого-цифрового преобразователя «временной интервал-код», не включенного в замкнутый контур следящей системы [3, Лихарев В.А. Цифровые методы и устройства в радиолокации. М.: «Советское радио», 1973, стр.243]. Также при изменении закона движения цели, когда возникают динамические ошибки слежения, ошибка слежения может выйти за пределы статической характеристики дискриминатора, и может произойти срыв слежения, что не учтено в данном устройстве.

Наиболее близким к предлагаемому решению по технической сущности и достигаемому эффекту является цифровой временной дискриминатор [3, стр.244, рис.3.8], который и выбран в качестве прототипа. Цифровой временной дискриминатор содержит первую и вторую схемы «И», первые входы которых соединены и являются входом устройства, а вторые входы подключены к выходу генератора импульсов, последовательно соединенные генератор строба и первый блок задержки, выход которого подключен к третьему входу первой схемы «И», реверсивный счетчик, подключенный первым входом к выходу первой схемы «И», а вторым - к выходу второй схемы «И», при этом на третий вход реверсивного счетчика подается сигнал нулевой установки, а выход генератора строба подключен к третьему входу второй схемы «И».

Недостатком прототипа являются ограниченные размеры рабочего участка дискриминаторной характеристики, что при интенсивном изменении закона движения цели приводит к размыканию кольца обратной связи и, соответственно, - к срыву слежения.

Техническим результатом заявляемого технического решения является эквивалентное расширение квазилинейного рабочего участка дискриминаторной характеристики за счет оперативной коррекции сигнала отрицательной обратной связи следящей системы, поступающего на дискриминатор в качестве опорного цифрового кода.

Это достигается тем, что цифровой временной дискриминатор, содержащий первую и вторую схемы «И», первые входы которых соединены и являются входом устройства, а вторые входы подключены к выходу генератора импульсов, последовательно соединенные генератор строба и первый блок задержки, выход которого подключен к третьему входу первой схемы «И», реверсивный счетчик, подключенный первым входом к выходу первой схемы «И», а вторым - к выходу второй схемы «И», при этом на третий вход реверсивного счетчика подается сигнал тактовой нулевой установки, а выход генератора строба подключен к третьему входу второй схемы «И», отличается тем, что в него дополнительно введены последовательно соединенные фильтр, блок сравнения, второй блок задержки, первый сумматор и цифроаналоговый преобразователь, а также второй сумматор, первый вход которого подключен к выходу реверсивного счетчика, второй вход - к выходу второго блока задержки, а выход - к первому входу фильтра, на второй вход которого поступает сигнал установки нуля при начале сопровождения цели, который поступает также на второй вход второго блока задержки, на второй вход блока сравнения подается сигнал порога, на второй вход первого сумматора подается опорный сигнал, а выход цифроаналогового преобразователя соединен с входом генератора стробов.

Суть заявляемого устройства поясняется чертежами.

На фиг.1 представлена функциональная схема предлагаемого цифрового временного дискриминатора;

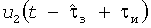

На фиг.2 - функциональная схема фильтра;

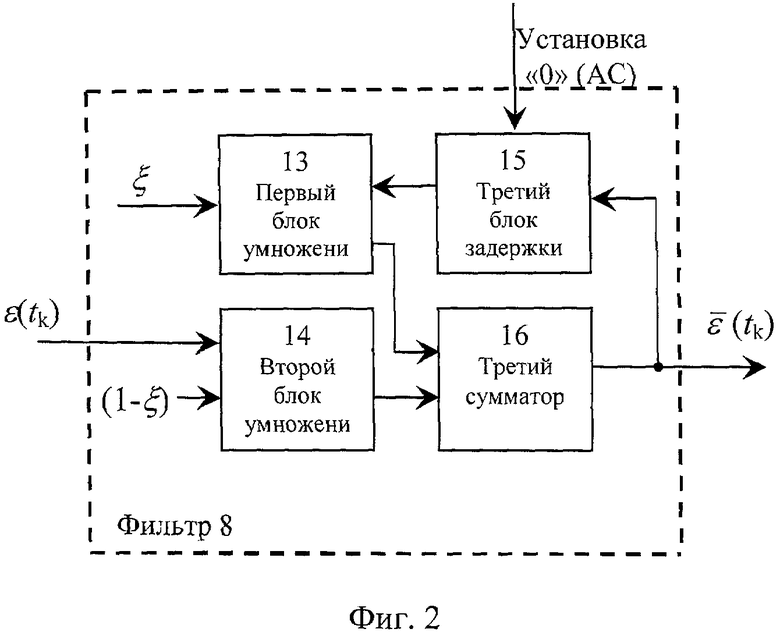

на фиг.3 - функциональная схема блока сравнения;

на фиг.4 - статическая характеристика прототипа  ;

;

на фиг.5 - статическая характеристика  блока сравнения;

блока сравнения;

на фиг.6 - временная диаграмма работы предлагаемого цифрового временного дискриминатора;

на фиг.7 - преобразование структуры предлагаемого устройства;

на фиг.8 - построение результирующей статической характеристики  предлагаемого устройства.

предлагаемого устройства.

Цифровой временной дискриминатор (фиг.1) содержит первую и вторую схемы 1 и 2 «И», первые входы которых соединены и являются входом устройства, а вторые входы подключены к выходу генератора 3 импульсов, последовательно соединенные генератор 4 строба и первый блок 5 задержки, выход которого подключен к третьему входу первой схемы 1 «И». Реверсивный счетчик 6 в составе устройства подключен первым входом к выходу первой схемы 1 «И», а вторым - к выходу второй схемы 2 «И». При этом на третий вход реверсивного счетчика 6 подается сигнал тактовой нулевой установки, а выход генератора 4 строба подключен к третьему входу второй схемы 2 «И». Кроме этого в состав устройства входят цифроаналоговый преобразователь (ЦАП) 7, последовательно соединенные фильтр 8, блок 9 сравнения, второй блок 10 задержки и первый сумматор 11, а также второй сумматор 12, первый вход которого подключен к выходу реверсивного счетчика 6, второй вход - к выходу второго блока 10 задержки, а выход - к первому входу фильтра 8, на второй вход которого поступает сигнал установки нуля при начале сопровождения цели. Данный сигнал поступает также на второй вход второго блока 10 задержки. На второй вход блока 9 сравнения подается сигнал порога. ЦАП 7 подключен выходом к входу генератора 4 строба, а входом - к выходу первого сумматора 11, на второй вход которого подается опорный сигнал.

В состав фильтра 8 (фиг.2) входят первый и второй блоки 13 и 14 умножения, третий блок 15 задержки и третий сумматор 16, выход которого соединен с третьим блоком 15 задержки и является выходом фильтра 8, входом которого является первый вход второго блока 14 умножения. На первый вход первого блока 13 умножения и второй вход второго блока 14 умножения подаются значения сигналов сглаживания ξ и (1-ξ) соответственно. Выходы блоков 13 и 14 умножения соединены с первым и вторым входами третьего сумматора 16. Второй вход первого блока 13 умножения подключен к выходу третьего блока 15 задержки.

В состав блока 9 сравнения (фиг.3) входят первый и второй компараторы 17 и 18, подключенные соответственно к первому и второму входам схемы 19 «ИЛИ», выход которой соединен с первым входом блока 20 схем «И», количество которых равно количеству разрядов кода  , поступающего на вход блока 9 сравнения. Первый и второй входы блока 9 сравнения являются соответственно первыми и вторыми входами первого и второго компараторов 17 и 18. Первый вход первого компаратора 17 соединен с вторым входом блока 20 схем «И».

, поступающего на вход блока 9 сравнения. Первый и второй входы блока 9 сравнения являются соответственно первыми и вторыми входами первого и второго компараторов 17 и 18. Первый вход первого компаратора 17 соединен с вторым входом блока 20 схем «И».

Цифровой временной дискриминатор работает следующим образом.

Дискриминатор измеряет в дискретные моменты времени tk невязку

между истинным τз и ожидаемым  временами задержки сигнала от цели. При передаче цели на автосопровождение состояния блоков устройства импульсом установки «0» (АС) приводятся в исходное состояние, в том числе обнуляются элементы памяти фильтра 8 (третьего блока 15 задержки) и второго блока 10 задержки.

временами задержки сигнала от цели. При передаче цели на автосопровождение состояния блоков устройства импульсом установки «0» (АС) приводятся в исходное состояние, в том числе обнуляются элементы памяти фильтра 8 (третьего блока 15 задержки) и второго блока 10 задержки.

При сопровождении цели в начале каждого такта зондирования (см. фиг.6) реверсивный счетчик 6 импульсом тактовой установки «0» устанавливается на 0. Определенный в соответствии со значением  код опорного сигнала uоп(tk), определяющий момент выработки стробов сопровождения, подается через первый сумматор 11 и ЦАП 7 на вход генератора 4 строба, на выходе которого формируется первый строб

код опорного сигнала uоп(tk), определяющий момент выработки стробов сопровождения, подается через первый сумматор 11 и ЦАП 7 на вход генератора 4 строба, на выходе которого формируется первый строб  . Соответственно на выходе первого блока 5 задержки (с временем задержки τи) формируется второй строб

. Соответственно на выходе первого блока 5 задержки (с временем задержки τи) формируется второй строб  . Перемножения принятого импульса

. Перемножения принятого импульса  и двух опорных

и двух опорных  и

и  производятся в двух схемах 1 и 2 «И» с заполнением временных интервалов импульсами масштабной частоты от генератора 3 импульсов. Период повторения генератора 3 импульсов Тд=τи/n, n≥8 [3, стр.243]. Функции интеграторов и вычитающего устройства выполняет реверсивный счетчик 6, формирующий сигнал рассогласования

производятся в двух схемах 1 и 2 «И» с заполнением временных интервалов импульсами масштабной частоты от генератора 3 импульсов. Период повторения генератора 3 импульсов Тд=τи/n, n≥8 [3, стр.243]. Функции интеграторов и вычитающего устройства выполняет реверсивный счетчик 6, формирующий сигнал рассогласования  в дискретные моменты времени tk.

в дискретные моменты времени tk.

Ширина дискриминаторной характеристики (фиг.4) равна 2τи, причем ширина рабочего квазилинейного участка составляет τи.

Сигнал измеренной невязки  с выхода второго сумматора 12 поступает в фильтр 8, на выходе которого формируется сглаженный сигнал невязки

с выхода второго сумматора 12 поступает в фильтр 8, на выходе которого формируется сглаженный сигнал невязки  , пропорциональный математическому ожиданию невязки

, пропорциональный математическому ожиданию невязки  . Сигнал сглаженной невязки

. Сигнал сглаженной невязки  определяется по выражению [4, Кузьмин С.З. Основы теории цифровой обработки радиолокационной информации. - М.: Советское радио, 1974, стр.400]:

определяется по выражению [4, Кузьмин С.З. Основы теории цифровой обработки радиолокационной информации. - М.: Советское радио, 1974, стр.400]:

где ξ - задаваемый весовой коэффициент.

Структура фильтра 8, соответствующая выражению (2), приведена на фиг.2 [4, стр.400, рис.4.19]. Время задержки сигнала в третьем блоке 15 задержки равно одному такту работы Тт следящей системы.

С выхода фильтра 8 сигнал  подается на первый вход блока 9 сравнения (фиг.3), на второй вход которого подается код порога сравнения uп. Первый и второй компараторы 17 и 18 в составе блока 9 сравнения могут быть построены по схемам цифровых компараторов [5, Боит К. Цифровая электроника. Пер. с немец. - М.: Техносфера, 2007. - 321].

подается на первый вход блока 9 сравнения (фиг.3), на второй вход которого подается код порога сравнения uп. Первый и второй компараторы 17 и 18 в составе блока 9 сравнения могут быть построены по схемам цифровых компараторов [5, Боит К. Цифровая электроника. Пер. с немец. - М.: Техносфера, 2007. - 321].

Если модуль сигнала  не превышает уровня заданного порога uп (фиг.4), то сигналы «

не превышает уровня заданного порога uп (фиг.4), то сигналы « » с выхода первого компаратора 17 и «

» с выхода первого компаратора 17 и « » с выхода второго компаратора 18, а также схемы 19 «ИЛИ» принимают нулевые значения. На выходе блока 20 схем «И», количество которых равно количеству разрядов кода

» с выхода второго компаратора 18, а также схемы 19 «ИЛИ» принимают нулевые значения. На выходе блока 20 схем «И», количество которых равно количеству разрядов кода  , также формируется код «0», который через блок 10 задержки поступает на второй вход второго сумматора 12 и первый вход первого сумматора 11. Следовательно, коды измеренных невязок на выходе реверсивного счетчика 6 и второго сумматора 12 совпадают (фиг.6, а).

, также формируется код «0», который через блок 10 задержки поступает на второй вход второго сумматора 12 и первый вход первого сумматора 11. Следовательно, коды измеренных невязок на выходе реверсивного счетчика 6 и второго сумматора 12 совпадают (фиг.6, а).

Если же модуль сигнала  превышает уровень заданного порога uп (фиг.6, б), то в зависимости от знака сигнала

превышает уровень заданного порога uп (фиг.6, б), то в зависимости от знака сигнала  на одном из выходов первого либо второго компараторов 17, 18 и, соответственно, на выходе схемы 19 «ИЛИ» формируются сигналы, разрешающие блоку 20 схем «И» сформировать на выходе блока 9 сравнения сигнал

на одном из выходов первого либо второго компараторов 17, 18 и, соответственно, на выходе схемы 19 «ИЛИ» формируются сигналы, разрешающие блоку 20 схем «И» сформировать на выходе блока 9 сравнения сигнал  . Следовательно, статическая характеристика блока 9 сравнения имеет вид, изображенный на фиг.5. В следующем такте работы следящей системы (фиг.6, в) этот сигнал

. Следовательно, статическая характеристика блока 9 сравнения имеет вид, изображенный на фиг.5. В следующем такте работы следящей системы (фиг.6, в) этот сигнал  сформируется на выходе второго блока 10 задержки (время задержки - один такт) и будет подан на первый вход первого сумматора 11 и второй вход второго сумматора 12. Код сигнала uоп(tk) будет скорректирован величиной

сформируется на выходе второго блока 10 задержки (время задержки - один такт) и будет подан на первый вход первого сумматора 11 и второй вход второго сумматора 12. Код сигнала uоп(tk) будет скорректирован величиной  так, что стык стробов будет приближен к середине входного импульса от цели. Соответственно, рабочая точка устройства на дискриминаторной характеристике сместится к середине ее квазилинейного участка, что предотвратит срыв слежения. В свою очередь, благодаря сигналу

так, что стык стробов будет приближен к середине входного импульса от цели. Соответственно, рабочая точка устройства на дискриминаторной характеристике сместится к середине ее квазилинейного участка, что предотвратит срыв слежения. В свою очередь, благодаря сигналу  на втором входе второго сумматора 12, на его выходе будет сформирована истинная невязка

на втором входе второго сумматора 12, на его выходе будет сформирована истинная невязка  (фиг.6, в).

(фиг.6, в).

Покажем, что в предлагаемом устройстве происходит эквивалентное расширение квазилинейного участка дискриминаторной характеристики. На фиг.7а приведена структурно-алгоритмическая схема предлагаемого устройства. Здесь функции  и

и  отражают характеристики, приведенные на фиг.4 и фиг.5 соответственно. Данное устройство функционирует с малыми значениями сформированных на выходе реверсивного счетчика измеряемых ошибок Uд(ε1). Учитывая это и перенося сумматор Σ1 через элемент сравнения, структуру, приведенную на фиг.7а, можно преобразовать к виду - фиг.7б. Построим обобщенную статическую характеристику соединений элементов на фиг.7б.

отражают характеристики, приведенные на фиг.4 и фиг.5 соответственно. Данное устройство функционирует с малыми значениями сформированных на выходе реверсивного счетчика измеряемых ошибок Uд(ε1). Учитывая это и перенося сумматор Σ1 через элемент сравнения, структуру, приведенную на фиг.7а, можно преобразовать к виду - фиг.7б. Построим обобщенную статическую характеристику соединений элементов на фиг.7б.

На фиг.8, а приведено построение характеристики ε*=ε*(ε1) параллельного соединения пропорционального звена и звена с коэффициентом передачи

На фиг.8, б приведено построение последовательного соединения характеристик ε*=ε*(ε1) и F1(ε*). На фиг.8, в приведено построение параллельного соединения предыдущих звеньев и звена с коэффициентом передачи

Сравнительный анализ дискриминаторных характеристик  предлагаемого технического решения и прототипа Uд(ε) показывает, что заявляемое устройство позволяет достичь технического результата, заключающегося в эквивалентном расширении квазилинейного рабочего участка дискриминаторной характеристики, что в свою очередь приводит к уменьшению возможности срыва слежения цели, то есть - расширению области динамической устойчивости следящей системы, в состав которой и входит устройство.

предлагаемого технического решения и прототипа Uд(ε) показывает, что заявляемое устройство позволяет достичь технического результата, заключающегося в эквивалентном расширении квазилинейного рабочего участка дискриминаторной характеристики, что в свою очередь приводит к уменьшению возможности срыва слежения цели, то есть - расширению области динамической устойчивости следящей системы, в состав которой и входит устройство.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ СЛЕДЯЩИЙ ИЗМЕРИТЕЛЬ | 2012 |

|

RU2492506C1 |

| СЛЕДЯЩИЙ ИЗМЕРИТЕЛЬ | 2010 |

|

RU2435172C1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И ЦИФРОВАЯ ТЕЛЕВИЗИОННАЯ СЛЕДЯЩАЯ СИСТЕМА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2010 |

|

RU2440691C1 |

| ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА | 2010 |

|

RU2444038C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| ВРЕМЕННОЙ ДИСКРИМИНАТОР | 1987 |

|

RU2042148C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| Цифровой временной дискриминатор | 1978 |

|

SU744913A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

Техническое решение относится к радиотехнике, радиолокации и может быть использовано в станциях сопровождения для измерения дальности до объектов локации и измерительных приборах для измерения временного положения сигналов. Техническим результатом заявленного решения является эквивалентное расширение квазилинейного рабочего участка дискриминаторной характеристики за счет оперативной коррекции сигнала отрицательной обработки связи следящей системы, поступающего на дискриминатор в качестве опорного цифрового кода; что в свою очередь приводит к уменьшению возможности срыва слежения цели, то есть - расширению области динамической устойчивости следящей системы, в состав которой входит устройство. Результат достигается за счет того, что в цифровой временной дискриминатор введены последовательно соединенные фильтр, блок сравнения, второй блок задержки, первый сумматор и цифроаналоговый преобразователь, а также второй сумматор. Первый вход второго сумматора подключен к выходу реверсивного счетчика, второй вход - к выходу второго блока задержки, а выход - к первому входу фильтра. На второй вход фильтр поступает сигнал установки нуля при начале сопровождения цели, который поступает также на второй вход второго блока задержки. На второй вход блока сравнения подается сигнал порога. На второй вход первого сумматора подается опорный сигнал, а выход цифроаналогового преобразователя соединен с входом генератора стробов. 8 ил.

Цифровой временной дискриминатор, содержащий первую и вторую схемы «И», первые входы которых соединены и являются входом устройства, а вторые входы подключены к выходу генератора импульсов, последовательно соединенные генератор строба и первый блок задержки, выход которого подключен к третьему входу первой схемы «И», реверсивный счетчик, подключенный первым входом к выходу первой схемы «И», а вторым - к выходу второй схемы «И», при этом на третий вход реверсивного счетчика подается сигнал тактовой нулевой установки, а выход генератора строба подключен к третьему входу второй схемы «И», отличающийся тем, что в него дополнительно введены последовательно соединенные фильтр, блок сравнения, второй блок задержки, первый сумматор и цифроаналоговый преобразователь, а также второй сумматор, первый вход которого подключен к выходу реверсивного счетчика, второй вход - к выходу второго блока задержки, а выход - к первому входу фильтра, на второй вход которого поступает сигнал установки нуля при начале сопровождения цели, который также поступает на второй вход второго блока задержки, на второй вход блока сравнения подается сигнал порога, на второй вход первого сумматора подается опорный сигнал, а выход цифроаналогового преобразователя соединен с входом генератора стробов.

| ВРЕМЕННОЙ ДИСКРИМИНАТОР УСТРОЙСТВА ТАКТОВОЙ СИНХРОНИЗАЦИИ | 2006 |

|

RU2314646C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| ВРЕМЕННОЙ ДИСКРИМИНАТОР | 1987 |

|

RU2042148C1 |

| SU 669877 A1, 10.02.1996 | |||

| US 3688201 A, 29.08.1972. | |||

Авторы

Даты

2012-03-20—Публикация

2011-03-02—Подача