Изобретение относится к области вычислительной техники и может быть применено в электронных вычислительных машинах с плавающей занятой.

Известные устройства для умножения чисел., представленных произвольным кодом, в машинах с плаваюш,ей запятой обязательно предполагают обработку порядков сомножителей для определения порядка произведения.

В машинах с плавающей запятой обработка порядков может производиться на основном сумматоре. В этом случае экономится оборудование, необходимое для организапии сумматора порядков, однако расходуется дополнительное время на выполнение операции умножения, связанное с обработкой порядков. Недостатком указанных устройств является наличие специального устройства для обработки порядков сомножителей (либо расходование дополнительного времени- на обработку порядков при совмещении сумматора чисел и сумматора порядков).

В предложенном устройстве эти недостатки устранены, при этом устройство позволяет определить порядок произведения без предварительной обработки порядков сомножителей.

равления содержит дополнительно триггер анализа запятой, вход которого соединен с регистром множителя, а выход - с регистром результата.

Умножение начинают обычным способом по любому из существующих и известных ранее способов умножения. В момент, когда в анализирующем разряде множителя появляется разряд с запятой, на сумматор отсылается множимое для очередного суммирования, а запятую множимого переписывают в тот разряд частичного произведения, который в данное время складывается с разрядом множимого, содержащим запятую. Эта запятая, участвуя в дальнейших сдвигах частичного произведения, в конечном итоге и определяет порядок произведения.

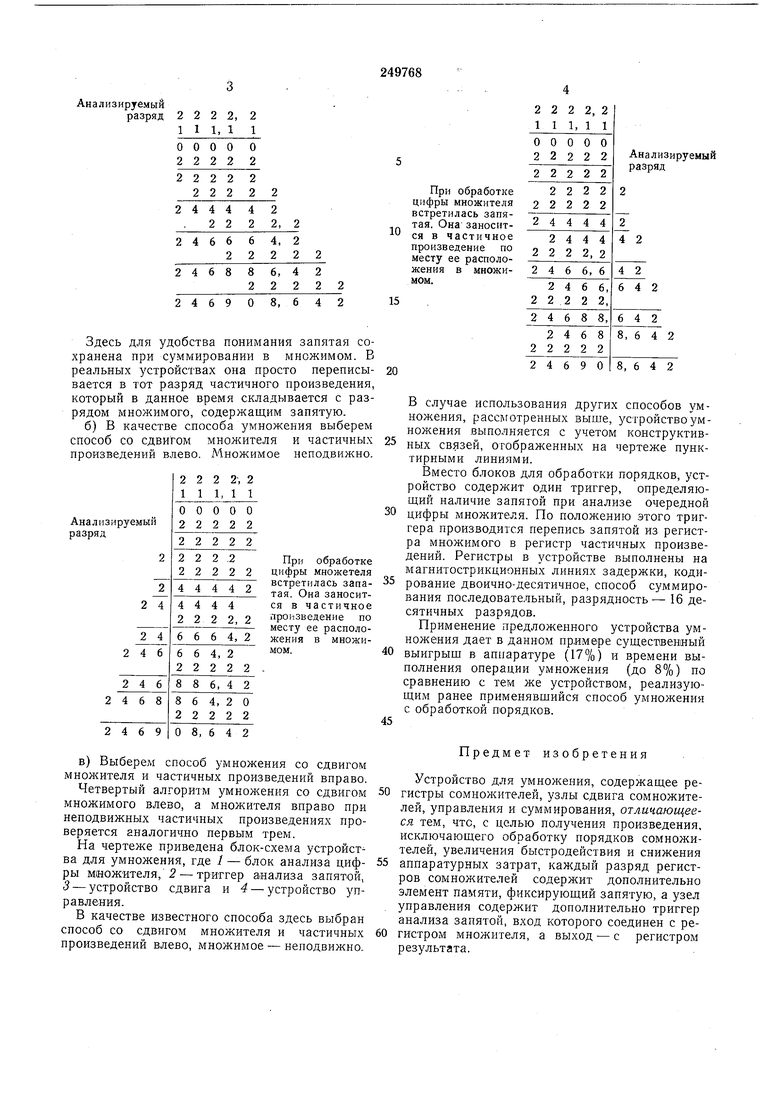

Рассмотрим несколько примеров выполнения операции умножения по предложенному способу.

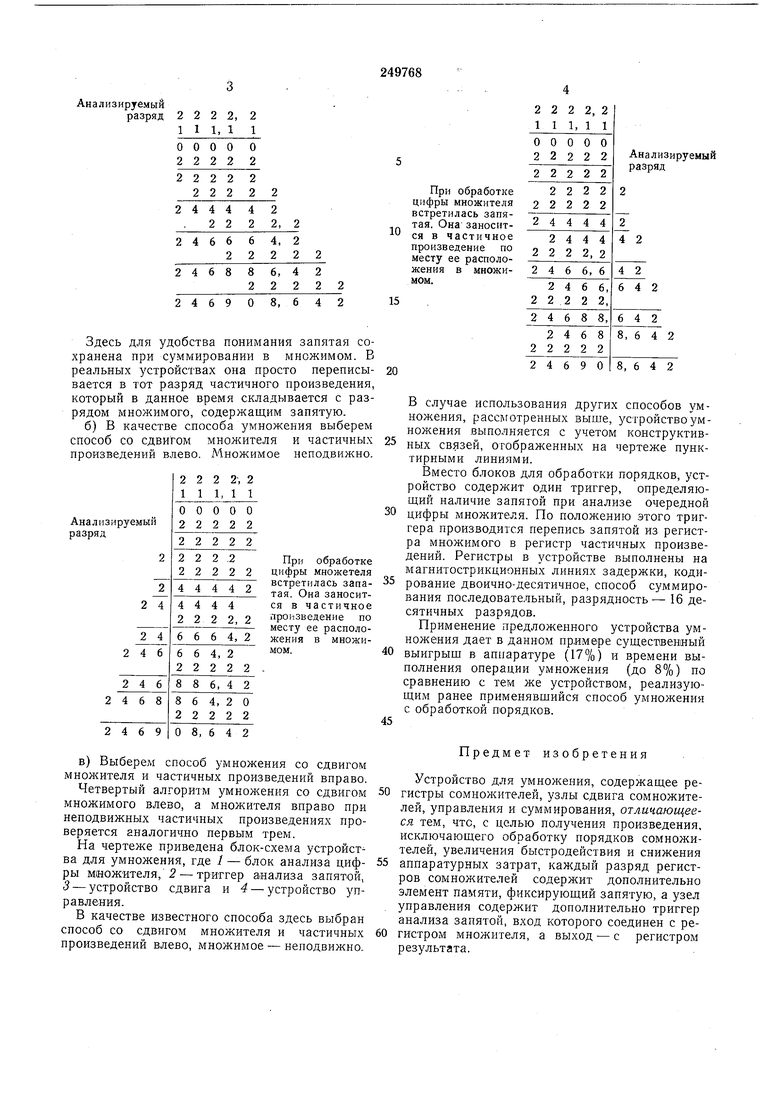

а) Умножим два числа 2222,2 (множимое) на 111,11 (множитель), выбрав в качестве способа умножения способ, при котором множитель сдвигается влево, а множимое - вправо. Частичное произведение неподвижно.

Анализируемый разряд

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1971 |

|

SU302002A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ | 1973 |

|

SU397910A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

2469 О 8, б 4 2

Здесь для удобства понимания запятая сохранена при суммировании в множимом. В реальных устройствах она просто переписывается в тот разряд частичного произведения, который в данное время складывается с разрядом множимого, содержащим запятую.

б) В качестве способа умножения выберем способ со сдвигом множителя и частичны.ч произведений влево. Множимое неподвижно.

При обработке цифры множетеля встретилась запатая. Она заносится в частичное произведение по месту ее расположения в множимом.

в) Выберем способ умножения со сдвигом мнол ителя и частичных произведений вправо.

Четвертый алгоритм умнол :ения со сдвигом .множимого влево, а множителя вправо при неподвижных частичных произведениях проверяется аналогично первым трем.

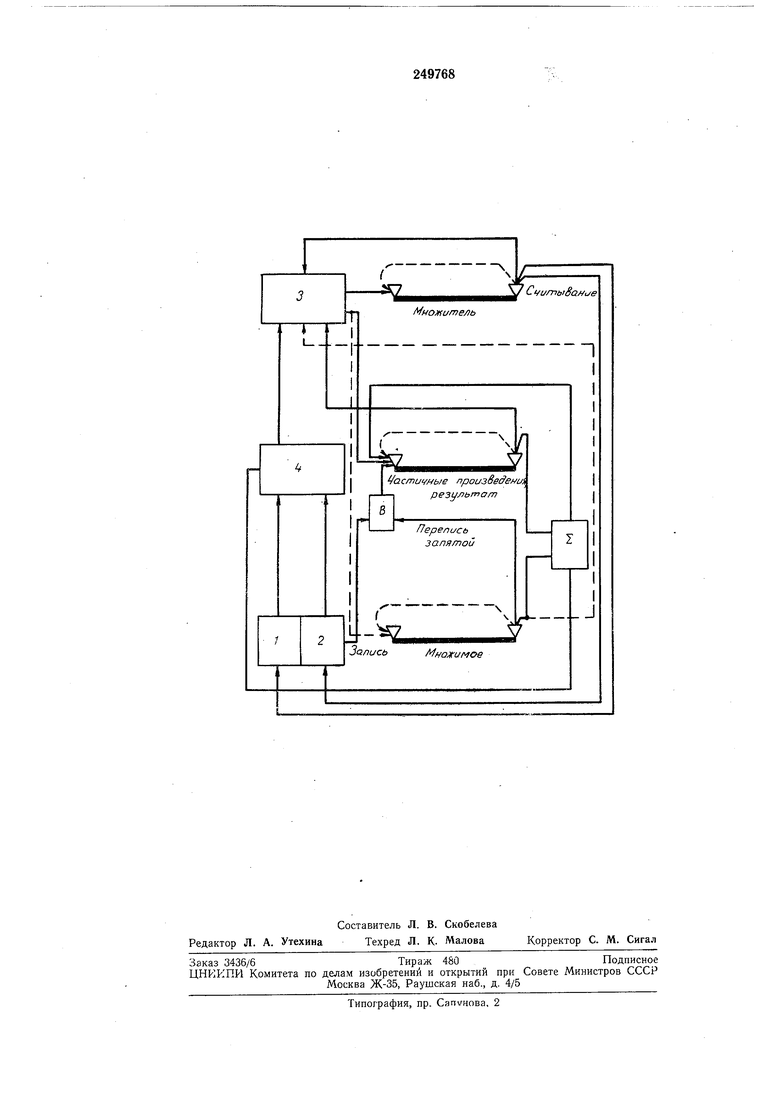

На чертеже приведена блок-схема устройства для умножения, где / - блок анализа цифры множителя, 2 - триггер анализа запятой, 3 - устройство сдвига и 4 - устройство управления.

В качестве известного способа здесь выбран способ со сдвигом множителя и частичных произведений влево, множимое - неподвижно.

При обработке цифры множителя встретилась запятая. Она заносится в частичное произведение по месту ее расположения в множимом.

В случае использования других способов умножения, расс1 готрениых выше, устройствоумножения выполняется с учетом конструктивных связей, отображенных на чертеже пунктирными линиями.

Вместо блоков для обработки порядков, устройство содержит один триггер, определяющий наличие запятой при анализе очередной

цифры множителя. По положению этого триггера производится перепись запятой из регистра множимого в регистр частичных произведений. Регистры в устройстве выполнены на магнитострикционных линиях задержки, кодирование двоично-десятичное, способ суммирования последовательный, разрядность- 16 десятичных разрядов.

Применение предложенного устройства умножения дает в данном примере сущест(венлый

выигрыш в аппаратуре (17%) и времени выполнения операции умножения (до 8%) по сравнению с тем же устройством, реализующим ранее применявшийся способ умножения с обработкой порядков.

Предмет изобретения

Устройство для умножения, содержащее регистры сомножителей, узлы сдвига сомножителей, управления и суммирования, отличающееся тем, что, с целью получения произведения, исключающего обработку порядков сомножителей, увеличения быстродействия и снижения аппаратурных затрат, каждый разряд регистров сомножителей содержит дополнительно элемент памяти, фиксирующий запятую, а узел управления содержит дополнительно триггер анализа запятой, вход которого соединен с регистром множителя, а выход - с регистром результата.

CvumbiSa/ tje

Множитель

VacmuvHb/e произведена результат

Даты

1969-01-01—Публикация