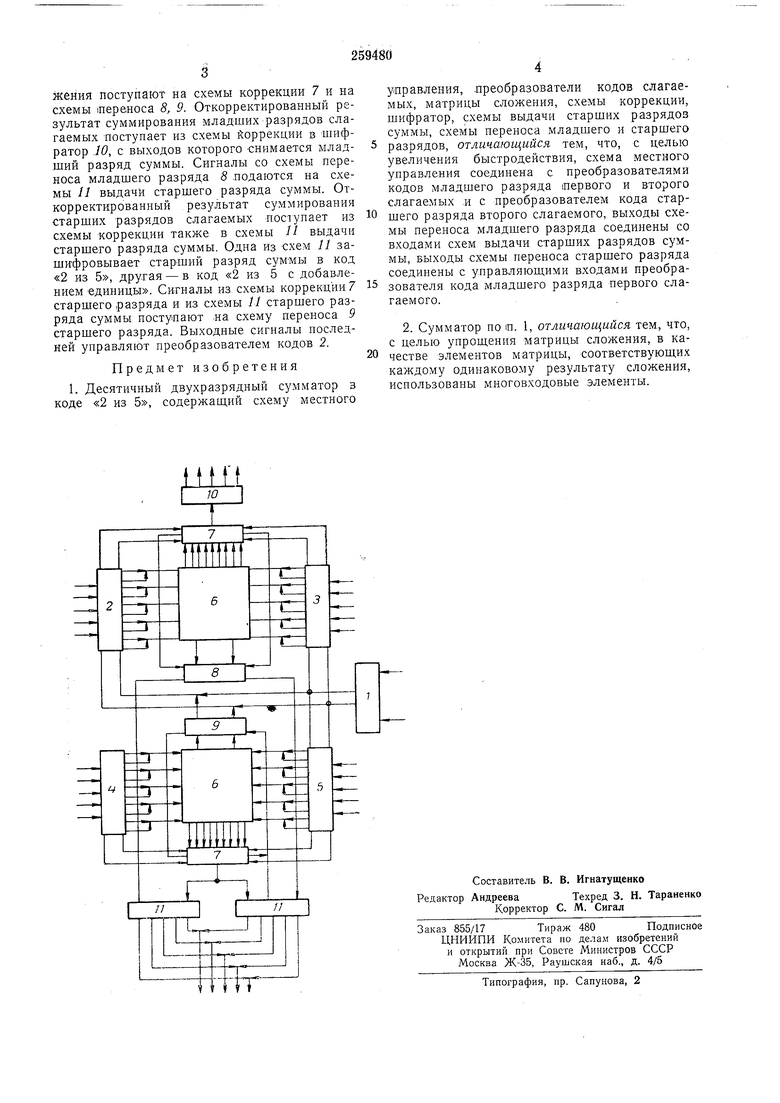

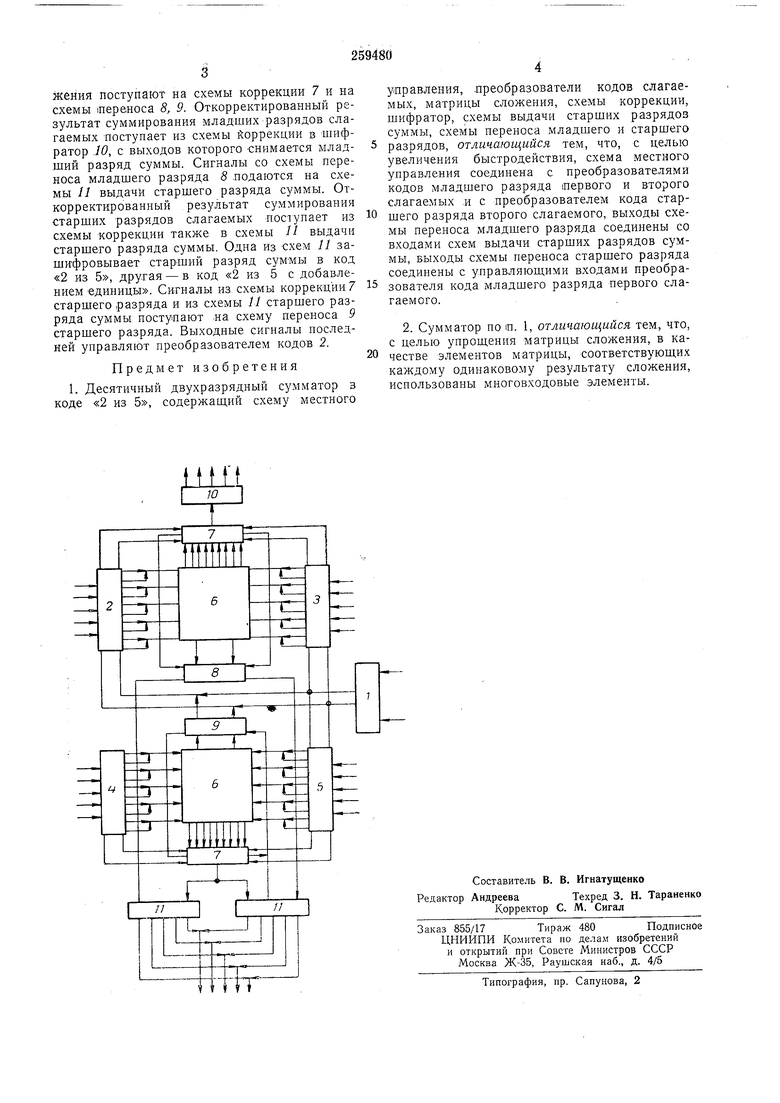

Изобретение относится к области вычислительной техники и предназначено для сложения и вычитания чисел, представленных в коде «2 из 5. Известен десятичный одноразрядный сумматор в коде «2 из 5, содержащий преобразователи кодов слагаемых, матрицу сложения размером 5X5 элементов, схему коррекции результата, схему переносов. Выходы преобразователей кодов слагаемых соединены со входами матрицы сложения и схемы коррекции результата, выходы матрицы сложения соеди,нены со входами схемы коррекции и через схему переносов с преобразователями кода первого слагаемого. Сложение (вычитание) одного разряда выполняется за четыре такта. Для быстродействия в предлагаемом сумматоре схема местного управления соединена с преобразователями кодов младшего разряда первого и второго слагаемых и с преобразователем кода сгаршего разряда второго слагаемого, выходы схемы переноса младшего разряда соединены со входами схем выдачи старших разрядов суммы, выходы схемы переноса старшего разряда соединены с управляющимц входами преобразователя кода младшего разряда первого слагаемого; кроме того, в качестве элементов матрицы, соответствующих каждому одинаковому результату сложения, использованы многовходовые элементы. Это позволяет выполнять сложение или вычитание в обоих разрядах сумматора за три такта, а также позволяет уменьшить количество элементов в матрице сложения до минимально возаможного (до девяти элементов). Схема сумматора изображена на чертеже. Он содержит схему местного управления 1, преобразователи кодов 2-5 соответственно младшего разряда первого слагаемого, младшего разряда второго слагаемого, старшего разряда первого слагаемого и старшего разряда второго слагаемого, матрицы сложения 6, схемы коррекции 7, схемы .переноса 5 и Р младшего и старшего разрядов, шифратор Ю и схемы 11 выдачи старшего разряда суммы. Сумматор работает следуюшим образом. Сигналы, соответствующие командам «сложить или «вычесть, поступают через схему местного управления на управляющие входы преобразователей кодов 2, 3 и 5. Преобразователи 2-5 расшифровывают подаваемые на них слагаемые в код «1 из 10 и посылают их на матрицы сложения 6. Одновременно указанные преобразователи посылают сообщения в схемы коррекции 7 о четности или нечетности прошедших через них слагаемых. Матрицы сложения 6 выполняют суммирование или вычитание слагаемых. Сигналы с матриц еложения поступают па схемы коррекции 7 и на схемы inepenoca 8, 9. Откорректированный результат суммирования младших разрядов слагаемых поступает из схемы Коррекции в шифратор .10, с выходов которого снимается младший разряд суммы. Сигналы со схемы переноса младшего разряда 8 .подаются на схемы 11 выдачи старшего разряда суммы. Откорректированный результат суммирования старших разрядов слагаемых поступает из схемы коррекции также в схемы 11 выдачи старшего разряда суммы. Одна из схем 11 зашифровывает старший разряд сум-мы в код «2 из 5, другая - в код «2 из 5 с добавлением единицы. Сигналы из схемы коррекции 7 старшего .разряда и из схемы 11 старшего разряда суммы поступают ла схему переноса 9 старшего разряда. Выходные сигналы последней управляют преобразователем кодов 2.

Предмет изобретения

1. Десятичный двухразрядный сумматор в коде «2 из 5, содержащий схему местного

управления, .преобразователи кодов слагаемых, матрицы сложения, схемы коррекции, шифратор, схемы выдачи старших разрядов суммы, схемы переноса младшего и старшего 5 разрядов, отличающийся тем, что, с целью увеличения быстродействия, схема местного управления соединена с преобразователями кодов младшего разряда первого и второго слагаемых .и с преобразователем кода старшего разряда второго слагаемого, выходы схемы переноса младшего разряда соединены со входами схем выдачи старших разрядов суммы, выходы схемы переноса старшего разряда соедииены с уиравляюш,ими входами преобразователя кода младшего разряда первого слагаемого.

2. Сумматор по п. 1, отличающийся тем, что,

с целью упрощения матрицы сложения, в качестве элементов матрицы, соответствующих

каждому одинаковому результату сложения,

исиользованы м.ноговходовые элементы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор в коде "м из N | 1979 |

|

SU873238A1 |

| Двухразрядный сумматор в коде "М из N | 1981 |

|

SU980092A1 |

| ОДНОТАКТНОЕ ЦИФРОВОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU330450A1 |

| Сумматор в коде "М из N | 1981 |

|

SU985781A1 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| СПОСОБ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ "1 ИЗ 4" И СУММАТОР В ЭТОМ КОДЕ | 2003 |

|

RU2251143C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Преобразователь двоично-десятичного кода в двоичный | 1984 |

|

SU1221758A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ | 1973 |

|

SU393740A1 |

| Двухразрядный сумматор в коде"M из | 1978 |

|

SU798828A1 |

Ш-Lt,

и 1

1 г

Авторы

Даты

1970-01-01—Публикация