Изобретение относится к области менения вычкс пи тельной техники в системах оперативного управления многообъектными комплексами, состоящими из объектов погрузки, разгрузки и безрельссюых транспортных средств.

Известна специализированная цифровая вычиолительная машина для выбора оптимальных адресов следования безрельсовьк транспортных средств, содержашая арифметическое устройство, логическое устройство, устройство ввода (вывода), устройство управления, долг яара енное и оперативное запомйнаюшие устройства.

Недостатком известных машин является их дороговизна и сложность.

иель изобретения - упрощение конструкции..

В логическом устройстве выходы ре- . бистра организационно-технического состояния управляемой системы подключены ко входам логических схем формирования критериев оптимальности, выходы которых подключены к потенциальным входам

вентилей записи и отбора. Импульсные входы вентилей записи соединены с пер- выми выходами распределителей решения и вентш15ами возобнсюления отбора, импульсные входы веншлей отбора связаны с выходами вентилей продолжения отбора и возобновления отбора. Выходы вентилей записи отбора соединены соответственно с единичными и нулевьп и входами триггеров регистра оптимальных адресе, а выходы триггеров оптимальных адресов связаны через схему анализа количества выделенных- адресов с потенциальными входами вентильных скем возобновления отбора, продолжения отбора, выдачи оптимального адреса, выделения минимума из ряда дискретных величин формирования неоснсеных решений. Первый выход схемы формирования управляющих импульсов соединен со входом запуска основного распределителя логического устройства, вход запрета которого соединен с выходом схемы запрета формирования управляющих импульссв основного решения, входы которой подключены к выходам вентилей вьщачи оптимального адреса и выделения минимума ряда дискретных величин. Вторые входы основного и допЬпнит«пьного распределителей подсо- единены к импульсным входам вентилей формирования неосновных решений, выходы которык соединены со входами дополнятепьвых распределителей, входы запрета кото{млх связаны со схемами форм роюання неуправляющих импульсов неоснсюного решения, входы схем формирования подключены к выходам вентилей выдачи оптимального адреса и выделения минимума ряда дискретных величин, остапьные выходы оснсжного и дополнительных распределителей соединены с импуль сными входами схем возобновления отбора, продолжения отбора, выдачи оптималь ного адреса, выделения минимума ряда дискретных величин. Выход триггера ана ка сумматора арифметического устройсгва подключен к потенциальному входу вен тиля сброса, импульсный вход которого соединен с одним из выходов схемы формирсжания управляющих импульсов устройн ства управления, а выход вентиля сброса соединен с нулевыми входами всех триггеров сумматора. В устройства ввода-выво да выходы регистра номеров транспортны средств соединены со входами схемы формирсиания импульса начала цикла, выход которой .соединен со входами запуска распределителя импульсов корректировки, причем первый выход последнего связан с импульсными входами вентилей занесения, потенциальные входы которых подсоединены к выходам опрашиваемого адреса, а выходы вентилей схемы занесения соединены с единичными входами триггеров младших разрядов сумматора; второй выход распределителя импульсов корректи ровки подсоединен к кодовой части регистра команд устройства управления и к импульсным входам первых вентилей фо{ мирования адресной части команды, потен циальные входы которых соединены с вы содами регистра номеров транспортных средств, а выходы - с адресной частью регистра команд. Третий выход распред лителя импульсов корректировки связан с импульсным входом вентиля, потенциальный вход которого соединен со схемой анализа сумматора на ноль, а его выход подключен ко входу запуска распределителя. Первый выход распределителя подсоединен к регистру команд устройства управления и к импульсным входам второй вентильной схемы формирования адресной части команд, потенциальные входы которой соединены со входами входного регистра арифметического устройства, причем выходы вентилей формирования адресной части команд соединены со входами адресной части регистра команд устройств управления; второй выход распределителя связан со счетными входами всех триггеров сумматора; третий выход распределителя подключен ко входам кодовой части регистра команд устройства управления; четвертый выход - к регист ру команд устройства управления и к импульсному входу третьих вентилей формирования адресной части команд, потенциальные входы которых соединены с выходами регистра опрашиваемого адреса, а выходы - со входами адресной части регистра команд устройства управления; пятый выход подключен к счетному входу триггера младшего разряда, сумматора, последний выход распределителя соединен со входом кодовой части регистра команд устройства управления. Выход схемы формирования импульса запуска рас пред елителя записи ответа устройства ввода-вьшода подсоединен ко входу распределителя записи ответа, выход кото- , рого соединен со входом кодовой части регистра команд устройства управления, с импульсным входом вентилей запоминания оптимального адреса и с импульсными входами схемы формирсзеания адресной части команд устройства ввода-вывода. Потенциальные входы схемы запоминания оптимального адреса подключены ко входам регистра оптимального ответа, а ее выходы связаны со схемой записи запоминающего устройства; потенциальные входы схемы формирования адресной части команд подключены ко входам буферного регистра номеров транспортных средств, а ее выходы соединены с адресной частью регистра команд устройства управления. Кроме того, с целью контроля возникающих неисправностей в арифметическом и логическом устройствах при выделении минимальной ,из ряда величин, схема логического контроля содержит вентиль контроля, потенциальный вход которого связан с одним из выходов схемы анализа количества выделенных адресов, а импульсный вход - с одним из выходов схемы формирования управляющих импульсов устройства управления. Выход вентиля контроля соединен со входом запуска основного распределителя логического устройства, со схемой сигнализации неисправности и счетчиком повторений, последняя разрядная ячейка которого подключена к схеме сигнализации и к схеме запрета формирования управляющих импульсов основного решения.

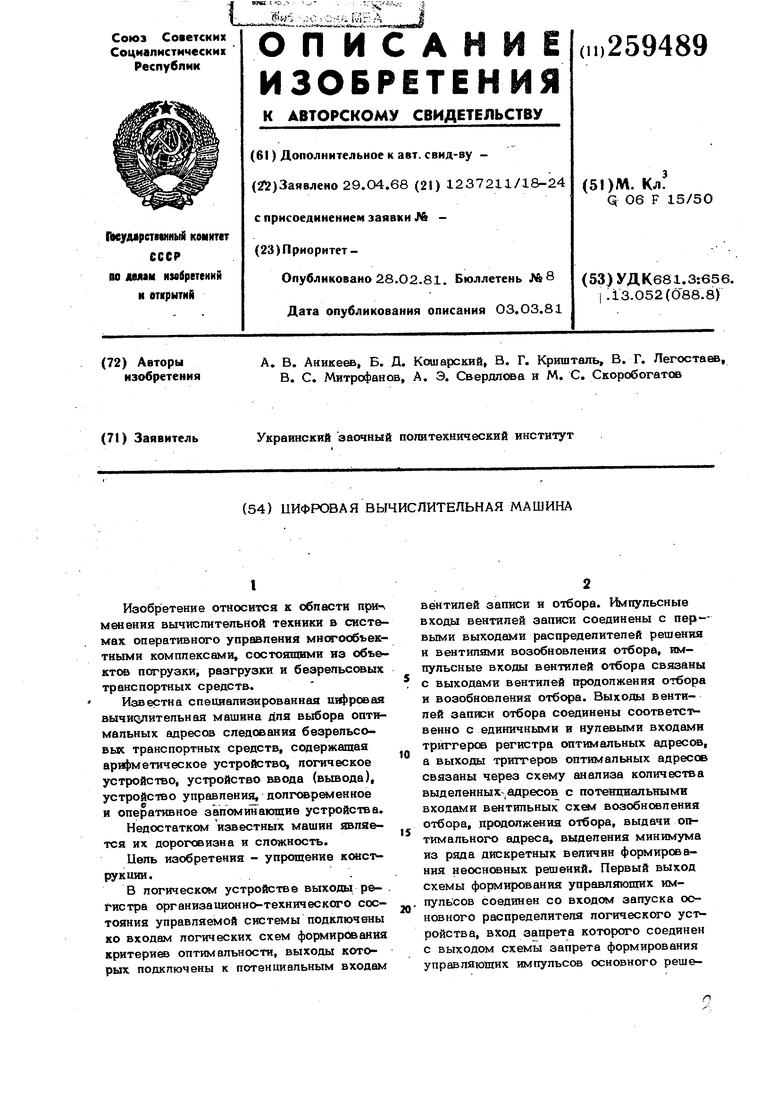

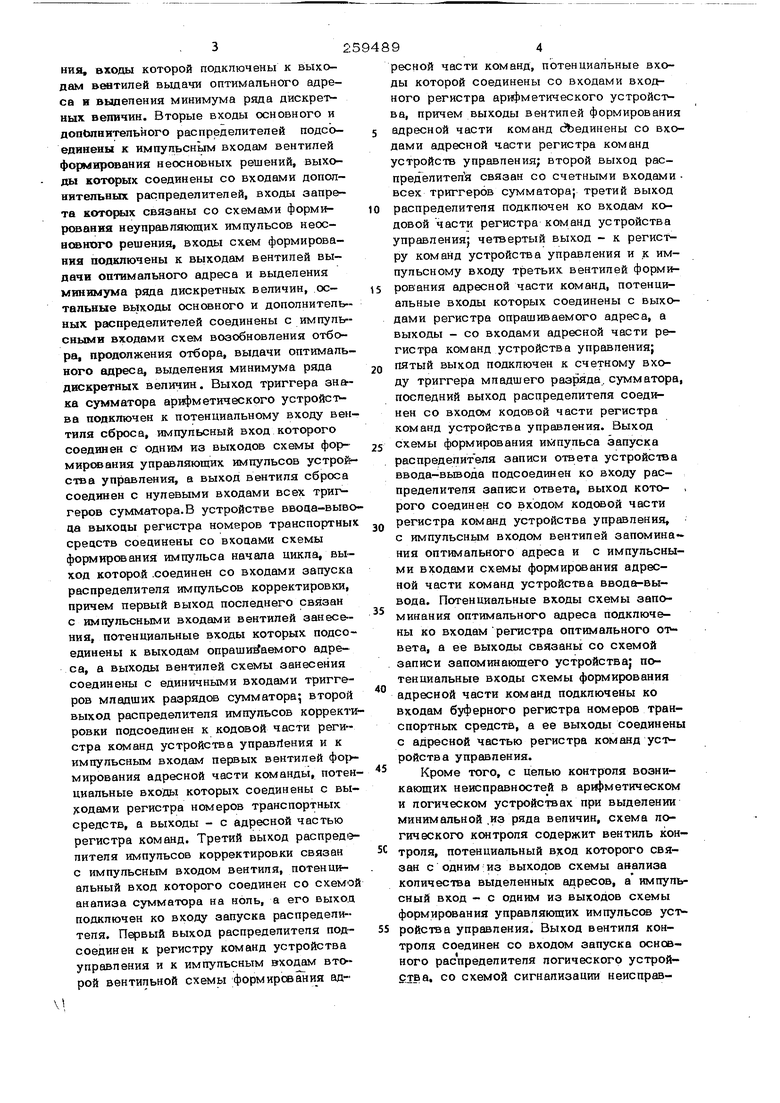

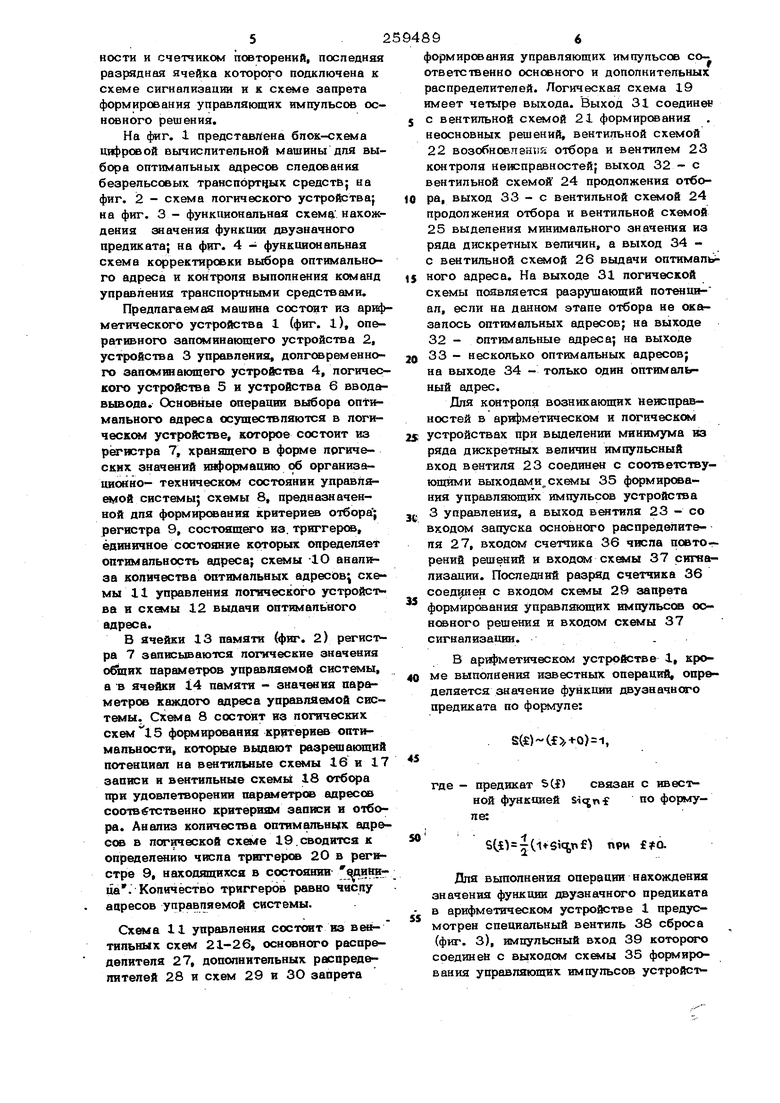

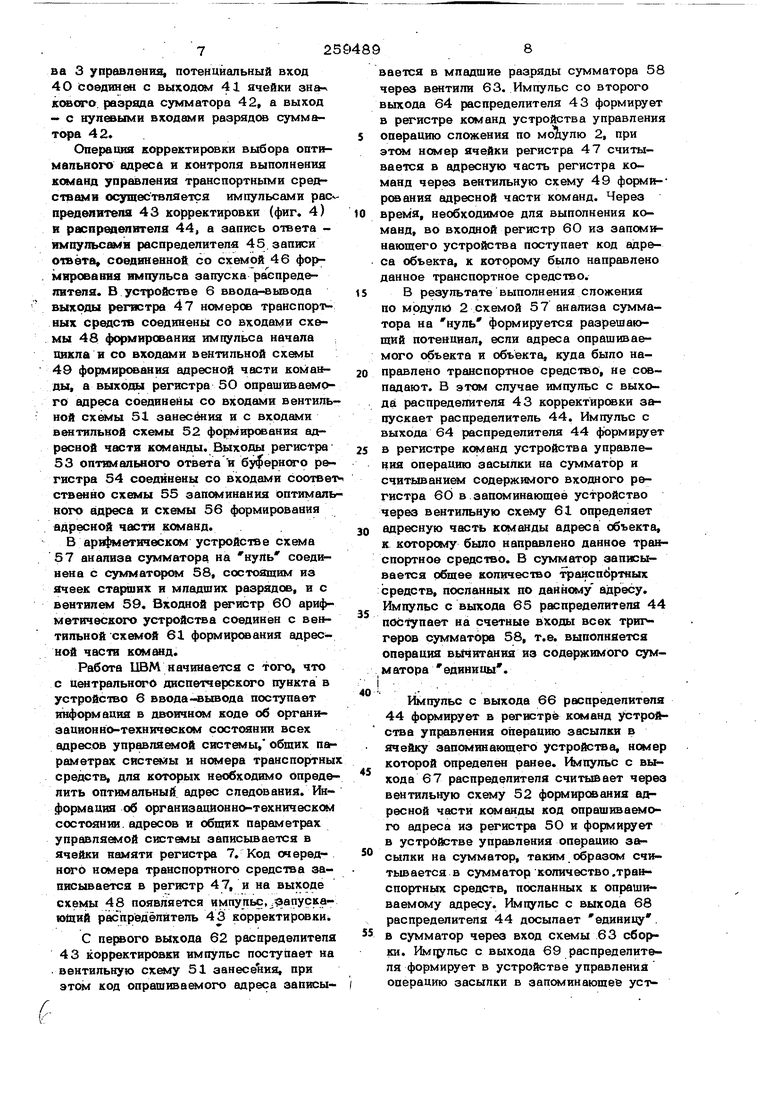

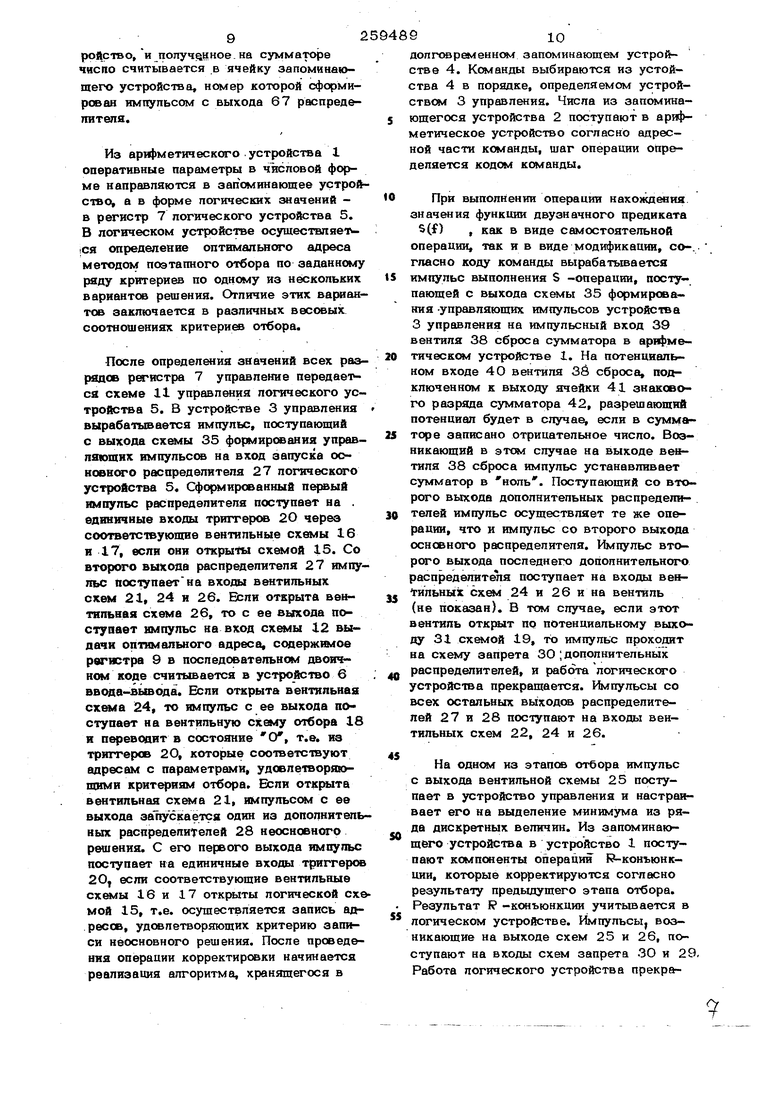

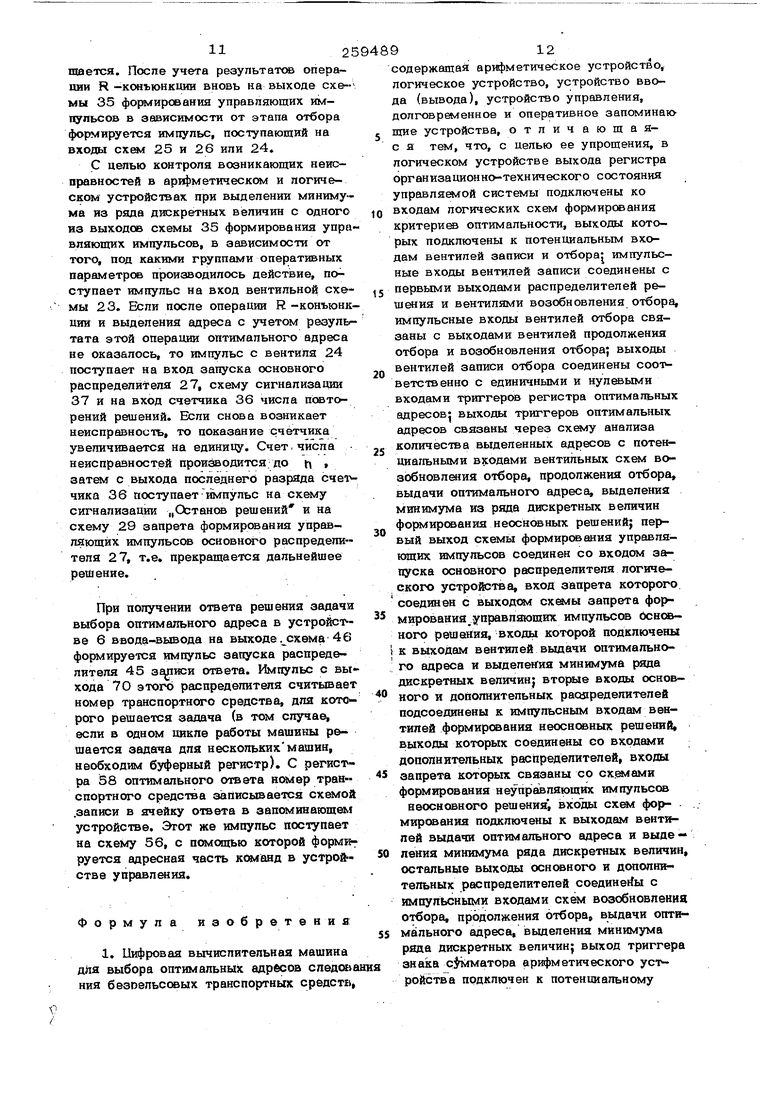

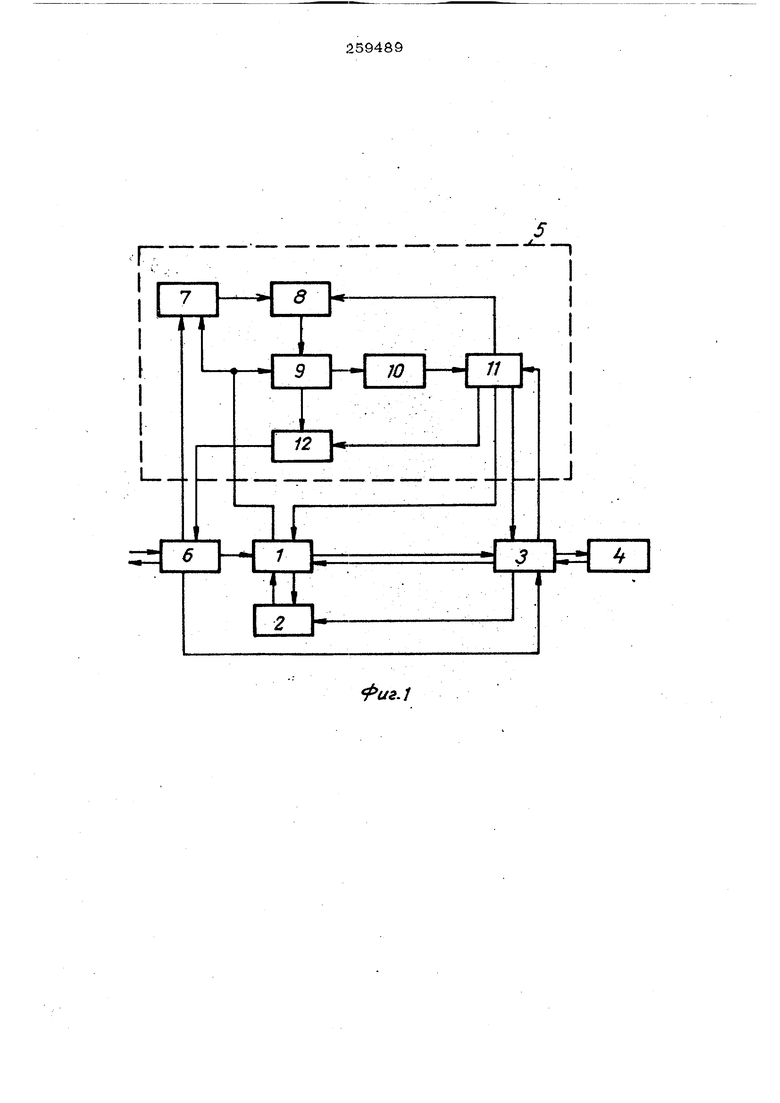

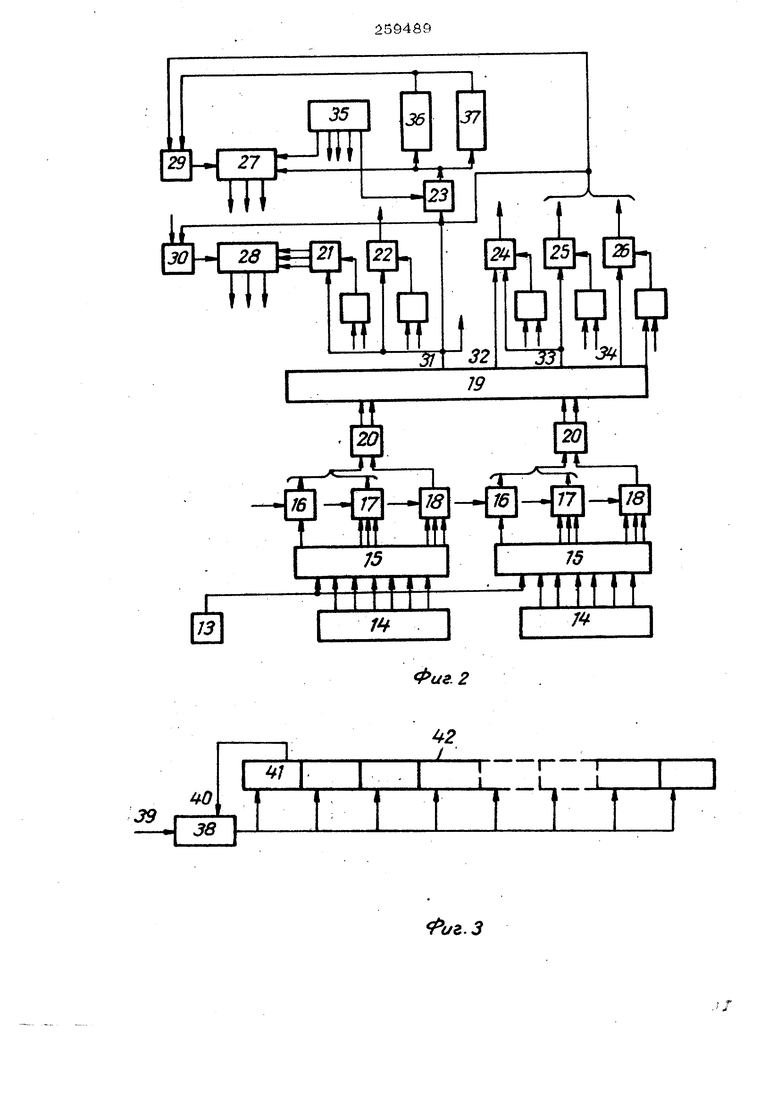

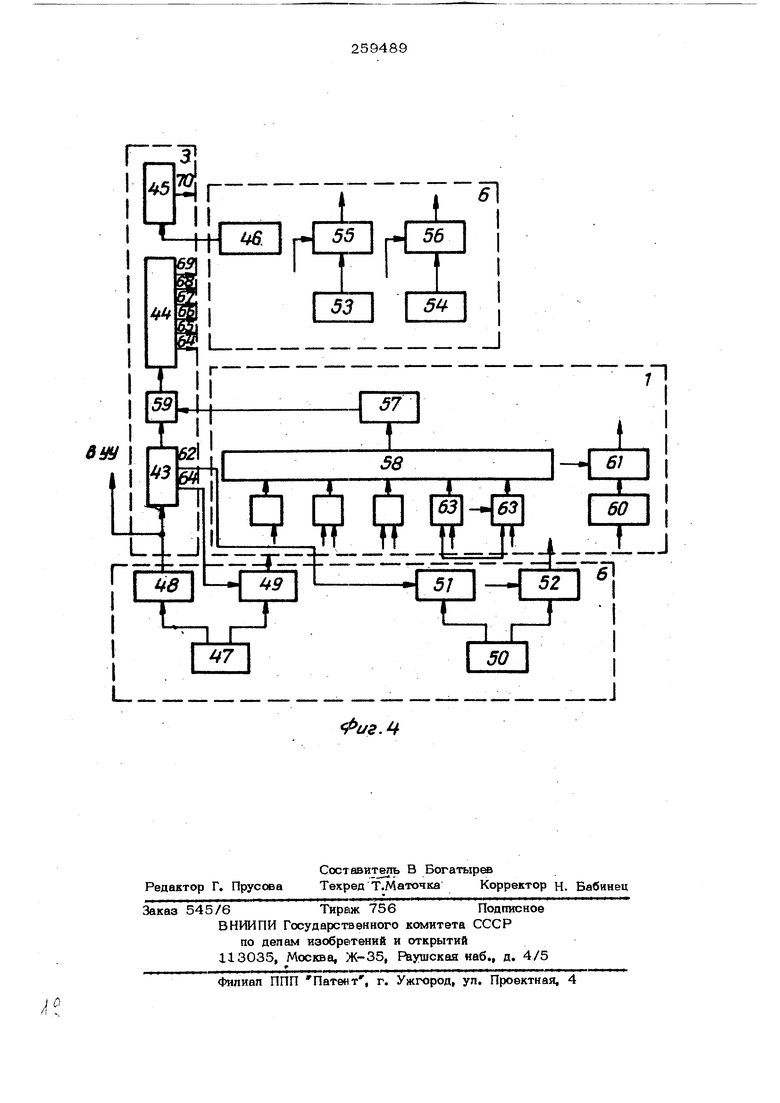

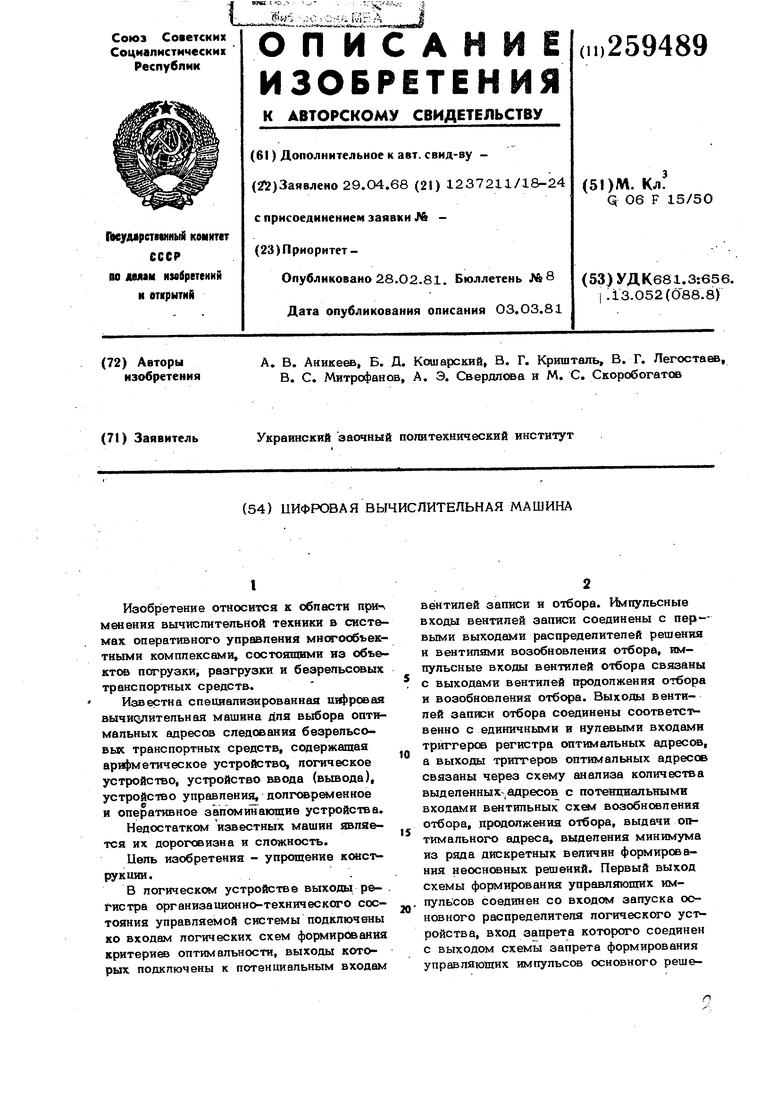

На фиг. 1 представпена бпок. шфрсжой вычислительной машины для выбора оптимальных адресов следования безрельсовых транспортчых средств; на фиг. 2 - схема логического устройства} на фиг. 3- функциональная схем нахождения значения функции двузначного предиката; на фиг. 4 - функциональная схема корректировки выбора оптимального адреса и контроля выполнения команд управления транспортными средствами.

Предлагаемая машина состоит из ар1фметического устройства 1 (фиг. 1), оперативного запоминающего устройства 2, устройства 3 управления, долге ременного запомтающего устройства 4, логического устройства 5 и устройства 6 вводавывода. Оснсквные операции выбора оптимального адреса осуществляются в логнческом устройстве, которое состоит из регистра 7, хранящего в форме логических значений информацию об организационно- техническом состоянии управляемой системы схемы 8, предназначенной для формир жания критериев отбора ; регистра 9, состоящего из. триггеров, единичное состояние которых опреде1гает оптимальность адреса; схемы -Ю анализа копвчесгаа оптимальных адресов схемы 11 управления логического устройства и схемы 12 выдачи оптимального адреса.

В ячейки 13 памяти (фиг. 2) регистра 7 записываются логические значения параметров управляемой системы, а в ячейки 14 памяти - значения параметров каждого адреса управляемой системы. Схема 8 состоит из попгаескнх формирования крртериев оптимальности, которые выдают разрешающий потенциал на вентильные схемы 16 и 17 записи и вентильные схемы 18 отбора при удовлетворении параметров адресе соответственно критериям записи и отбора. Анализ количества оптимальных адресе в логической схеме 19.сводится к определению числа триггере 20 в регистре 9, находящихся в состоянян единица. Количество триггеров равно чиспу ацресов управляемой системы.

Схема 11 управления состоят из вевтильных схем 21-26, осндаиого распределителя 27, дополнительных распределителей 28 и схем 29 и 30 запрета

формир(ания управляющих импупьссв соответсттвенно основного и дополнительных распределителей. Логическая схема 19 имеет четыре выхода. Выход 31 соединен с вентильной схемой 21 формирсеания неосновных решений, вентильной схемой 22 возобнсжления отбора и вентилем 23 контроля неисправностей; выход 32 - с вентильной схемой 24 продолжения отбоpa, выход 33 - с вентильной схемой 24 продолжения отбора и вентильной схемой 25 выделения минимального значения из ряда дискретных величин, а выход 34 с вентильной схаъ(ой 26 ВЕядачи оптималь

кого адреса. На выходе 31 логической схемы появляется разрушающий потенциал, если на данном этапе отбора не окенза лось оптимальных адресов; на выходе 32 - оптимальные адреса; на выходе

33 - несколько оптимальных адресов; на выходе 34 - только один оптимальный адрес.

Цля ксжтроля возникающих неисправностей в ари|)метическОм и логическом

устройствах при выделении минимума вз ряда дискретшлх величин импульсный вход вентиля 23 соединен с соответствующими выходами, схемы 35 формирсшания управляющих импульсов устройства 3 управления, а выход Бет1типя 23 - со входом запуска основного распределителя 27, входом счетчика 36 числа повтогрений решений и входом схемы 37 сигнализации. Последний разряд счетчика 36 с вкоаам схемы 29 запрета формирс ания управляющих импульсов решения и входом схемы 37 сигнализации.

В ари})метическс 1 устройстве 1, кроме выполнения известных операций, определяется значение функции двузначного предиката по формуле:

S()() 1,

45

где - предикат SCf) связан с ивестной функцией sitjn по формуле:

50

SC),r ПРИ .

1ля выполнения операции нахождения значения функции двузначного предиката в арифметически устройстве 1 предусмотрен специальный вентиль 38 сброса (фиг. 3), импульсный вход 39 которетч) соединен с выходом 35 формирования управляющих импульсов устройства 3 управпения, потенциальный вход 40 соединен с выход ы 41 ячейки зна ксшого. раэр5ша сумматора 42, а выход с нулевыми входами разряде сумматора 42. Операция корректировки выбора оптимального адреса и контроля выполнения команд упра вления транспортными средствами осуществляется импульсами рас предепитепя 43 корректировки (фиг 4) R распрепелвтеля 44, а запись ответа импупьсш я распределителя 45. записи О1ввта соединенной со схемой 46 фор. мировавия импульса запуска распределителя. В устройстве 6 ввода-вывода выходы регистра 4 7 намечав транспортных cpeaciB соединены со входами схемы 48 формирования импульса начала цикла и со входами вентильной схемы 49 (ания адресной части команды, а выходы регистра 50 опрашиваемого адреса соединены со входами вентиль ной схемы 51 занесения и с входами вк1типьной схемы 52 формирования адресной части команды. Выходы регистра 53 оптимального ответа и буферного ре гистра 54 соединены со входами соотве ственно схемы 55 запоминания оптималь ного адреса и схемы 56 формирования адресной час-га команд. В арнЦметическом устройстве схема 57 анализа сумматора на нуль соединена с сумматором 58, состоящим из ячеек старших и младших разрядов, и с вентилем 59. Входной рет-истр 60 арифметического устройства соединен с вентильной схемой 61 формирования адресной части комшд. Работа 11ВМ начинается с того, что с центрального диспетчерского пункта в устройство 6 ввода--вывода поступает информация в двоичнсж коде об организационно-техническом состоянии всех адресов управляемой системы, общих пее раметрах системы и н(м«1ера транспортны средств, для которых необходимо Опред лить оптимальный адрес следования. Информация об организационно-техническом состоянии, адресов и общих параметрах управляемой системы записывается в Ячейки памяти регистра 7. Код онередного номера транспортного средства записьюается в регистр 47, и на выходе схемы 48 появляется импульс, Запускающий распределитель 43 корректировки. С пе(юого выхода 62 распределителя 43 корректировки импульс поступает на вентильную 51 занесения, при этом код опрашиваемого адреса записывается в младшие разряды сумматора 58 через вентили 63. Импульс со второго выхода 64 распределителя 43 формирует в регистре команд устройства управления операцию сложения по мсшупю 2, при этом номер ячейки регистра 47 считывается в адресную часть регистра команд через вентильную схему 49 форми-р ания адресной части команд. Через время, необходимое для выполнения команд, во входной регистр 60 из запоминающего устройства поступает код адреса объекта, к которому было направлено данное транспортное средство. В результате выполнения сложения по модулю 2 схемой 57 анализа сумматора на нуль формируется разрешающий потенциал, если адреса опрашиваемого объекта и объекта, куда было направлено транспортное средство, не совпадают. В этом случае импульс с выхода распределителя 43 корректирсжки запускает распределитель 44. Импульс с выхода 64 распределителя 44 формирует в регистре команд устройства управления операцию засыпки на сумматор и считыванием содержимого входного регистра 6О в запоминающее устройство через вентильную схему 61 определяет адресную часть команды адреса объекта, к которому было направлено данное транспортное средство. В сумматор записывается общее количество транспбртных средств, посланных по данному адресу. Р пульс с выхода 65 распределителя 44 поступает на счетные входы всех триггеров сумматора 58, т.е. выполняется операция вычитания из содержимого сумм атора единицы. Шпульс с выхода 66 распределителя 44 формирует в регистре команд устройства управления операцию засылки в ячейку запсминающего устройства, нсмер которой определен ранее. Импульс с выхода 67 распределителя считывает через вентильную 52 формирсизания адресной части ксвуланды код опрашиваемого адреса из регистра 50 и формирует в устройстве управления операцию засылки на сумматор, таким О15разом счптьюается в сумматор количество .транспортных средств, посланных к опрашиваемому адресу. Импульс с выхода 68 распределителя 44 досылает единицу. в сумматор через вход схемы 63 . liMiynbC с выхода 69 распределителя формирует в устройстве управления операцию засылки в запоминающей устройство, и по лучинное, на сумматоре число считывается в ячейку запоминающего устройства, номер которой сформирован импульсом с выхода 67 распредетгатепя.

Из арифметического .устройства 1 оперативные параметры в числовой форме направляются в запоминаюшее устройство, а в форме логических значений в регистр 7 логического устройства 5. В логическом устройстве осуществляет iCH определение оптимального адреса методом поэтапного отбора по заданному ряду критериев по одному из нескольких варианте решения. Отличие этих вариантов заключается в различных весовых соотношениях критериев отбора.

После определения значений всех разродов ретистра 7 управление передается схеме 11 управления логического устройства 5. В устройстве 3 управления вырабатывается импульс, поступающий с выхода схемы 35 формирования управляющих импульсов на вход запуска ооиовнсиО распределителя 27 логического устройства 5. Сформированный импульс распределителя поступает на . единичные входы триггер 20 через соответсчвующие вентильные схемы 16 и 17, если они открыты схемой 15. Со второго выхода распределителя 27 импупьс пос1упаетна входы вентитшных схем 21, 24 и 26. Бели открыта вентипьная схема 26, то с ее выхода поступает импульс на вход схемы 12 выдачи оптимального адреса, содержк юе регистра 9 в последовательном двоичном коде считывается в устройство 6 ввода-вывода. Если открыта вентильная схема 24, то импульс с ее выхода поступает на вентильную схему отбора 18 и перевоаит в состояние О, т.е. из триггеров 2О, которые соответствуют адресам с параметрами, удовлетворяющими критериям отбора. Вели вентильная схема 21, импульсом с ее выхода заЪускается один из дополнительных распределителей 28 неосновного решения. С его первого выхода импульс поступает на единичные входы триггера 2О| если соответствующие вентильные схемы 16 и 17 открыты логической схемой 15, т.е. осуществляется запись адресов, удовлетворяющих критерию записи неосновного решения. После проведения операции корректировки начинается реализация алгоритма, хранящегося в

допговременнся запоминающем устройстве 4. Кслланды выбираются из устойства 4 в порядке, определяемом устройством 3 управления. Числа из запоминающегося устройства 2 поступают в арифметическое устройство согласно адресной части команды, шаг операции определяется кодом команды.

При выполнении операции нахождения значения функции двузначного предиката

S(f) , как в виде самостоятельной операции, так и в виде модификации, согласно коду команды вырабатьюается импульс выполнения S -операции, поступающей с выхода схемы 35 формирования -управляющих импульсов устройства 3 управления на импульсный вход 39 вентиля 38 сброса сумматора в арифметическом устройстве 1. На потенциальном входе 40 вентиля 36 сброса, подключенном к выходу ячейки 41 знакового разряда сумматора 42, разрешающий потенциал будет в случае если в сумматоре записано отрицательное число. Возникающий в этом случае на выходе вентиля 38 сброса импульс устанавливает сумматор в ноль. Поступающий со второго выхода дополнительных распределителей импульс осуществляет те же операции, что и импульс со второго выхода основного распределителя. Импульс второго выхода последнего дополнительного распределителя поступает на входы вевгильных 24 и 26 и на венталь (не показан). В том случае, если этот вентиль отк{илт по потенциальному выходу 31 (ой 19, тЪ импульс проходит на схему запрета 30 ; дополнительных распределителей, и работа логического устройства прекращается. Импульсы со всех остальных выходе распределителей 27 и 28 поступают на входы вентильных схем 22, 24 w 26.

На оаяом из этапе отбора импульс с выхода вентильной схемы 25 поступает в устройство управления и настраивает его на выделение минимума из ряда дискретных величин. Из запоминающего устройства в устройство 1 поступают компсженты операций { -конъюнкции, которые корректируются согласно результату предыдущего этапа отбора. Результат К -ксжъюнкции учитьюается в логическом устройстве. Импульсы, возникающие на выходе схем 25 и 26, поступают на входы схем запрета ЗО и 29 Работа логического устройства прекращается. После учета результатов операции R -конъюнкции вновь на выходе сх9мы 35 фо{ ирсвания управляющих имцульсов в зависимости от этапа отбора формируется импупьс, поступающий на входы сха 25 и 26 или 24. С цепью контроля возникающих неисправностей в арифметическом и логическом устройствах при выделении минимума из ряда дискретных величин с одного из выходов схемы 35 формирования ynp вляющих импульссю, в зависимости от того, под какими группами оперативных параметров производилось действие, поступает импульс на вход вентильной сх&мы 23. Если после операции R-конъюнк ции и выделения адреса с учетом резуль тата этой операции оптимального адреса не оказалось, то импупьс с вентиля 24 поступает на вход запуска основного распределителя 27, схему сигнализации 37 и на вход счетчика 36 числа повторений решений. Если снова возникает неисправность, то показание счетчика увеличивается на единицу. Счет, числа неисправностей производится; до h затем с выхода последнего разряда сче чика 36 поступает1алпульс на схему сигнализации „Останов решений и на схему 29 запрета формирования управляющих импульсов основнотО распределителя 27, т.е. прекращается дальнейшее решение. При получении ответа решения задачи выбора оптимального адреса в устройстве 6 ввода-вывода на выходе .схема 46 формируется импупьс запуска распределителя 45 записи ответа. Импульс с выхода 70 этого распределителя считывает номер транспортного средства, для которого решается задача (в том случае если в одном цикле работы машины ре шается задача для несколькихмашин, необходим буферный регистр). С регистра 58 оптимального ответа транспортного средства записывается схемой .записи в ячейку ответа в запо инающ устройстве. Этот же импупьс поступает на схему 56, с помощью которой форм1 к руется адресная часть ксманд в устройстве управления. Формула изобретения содержащая ари{)мэтическое устройство, логическое устройство, устройство ввода (вывода), устройство управления, долговременное и оперативное запоминающие устройства, отлич ающая- с я тем, что, с целью ее упрощения, в логическом устройстве выхода регистра организационно-технического состояния управляемой системы подключены ко входам логических схем формирования критерии оптимальности, выходы которых подключены к потенциальным входам вентилей записи и отбора: импульсные входы вентилей записи соединены с первыми выходами распределителей решения и вентилями возобновления отбора, импульсные входы вентилей отбора связаны с выходами вентилей продолжения отбора и возобновления отбора; выходы вентилей записи отбора соединены соответственно с единичными и нулевыми входами триггерсю регистра оптимальных адресов выходы триггеров оптимальных адресов связаны через схему анализа количества выделенных адресов с потенциагшными входами вентильных схем возЬбнселения отбора, продолжения отбора, выдачи оптимального адреса, выделения минимума из ряда дискретных величин формирсяания неосновных решений; первый выход схемы формирсжания управляющих импульсов соединен со входом запуска основного распределителя логического устройства, вход запрета которого соединен с выходом схемы запрета фо мирования управляющих импульсов йсн жного реШе{{ия, входы которой подключены к выходам вентилей выдачи оптимальнотч адреса и выделения минимума ряда дискретных величин; вторые входы основного и дополнительных раоаредепителей подсоединены к импульсным входам вентилей формирования неосновных решений, выходы которых соединены со входами дополнительных распределителей, входы запрета которых связаны со cxj stами формирования неуправляющих импульсов неосновного решения вхоТцд схем формирсгаания подключены к выходам вентилей выдачи оптимального адреса и выде- пения минимума ряда дискретных величии, остальные выхощл осн(ного к дополнительных реюпределителей соединейы с импульсными входами схем возобновления о-гбора, продолжения отбора, выдачи оптимального адреса, выделения минимума ряда дискретных величин; выход триггера знака сумматора арифметического устройства подключен к потенциальному входу вентиля сброса, импульсный вход которого соединен с одним из выходе схемы формирования управляющих импутть ссе устройства управления, а выход вентиля сброса соединен с нулевыми входами всех триггеров сумматора; в устройстве ввода-вьшода выходы регистра номеров транспортных средств соединены со входами схемы формирования импульса начала цикла, выход которой соединен со входами запуска распределителя импульсе корректировки, причем первый выход последнего связан с импульсными входами вентилей занесения, потенциальные входы которых подсоединены к выходам опрашиваемого адреса, а выходы вентильной схемы занесения соединены с единичными входами триггеров младших разрадов сумматора вто рой выход распределителя импульсов корректировки подсоединен к кодовой части регистра команд устройства управ ления и к импульсным входам первых вентилей формирования адресной части команды, потенциальные входы которых соединены с выходами регистра транспортных средств, а выходы - с адресной частью регистра команд} третий выход распределителя импульсов коррект связан с импульсным входом вентиля, псугенциальный вход которого соед нен со схемой анализа сумкгатора на нуль, а его выход подключен ко входу запускараспрецелитепя: первый выхоц распреаепитепя подсоединен к регистру команд устройства управления и к импупьсным входам второй вентильной схемы формирования адресной части команд, потенциальные входы которой соединены со входами входного регистра арифметического устройства, причем выходы вентилей формирования адресной части команд соединены со входами адресной части регистра команд устройства управления; второй выход распределителя связан со счетными входами всех триггеров сумматора; третий выход распределителя подключен ко входам кодовой части регистра команд устройства управления четвертый выход - к регистру к(ланд устройства управления и к импульсному входу третьих вентилей фор 914 мирования адресной части команд, потенциальные входы которых соединены с выходами регистра опрашиваемого адреса, а выходы - со входами адресной части регистра команд устройства управления; пятый выход подключен к счетному входу триггера младшего разряда сумматора, последний выход распределителя соединен со входом кодовой части регистра ксиланд устройства управления; выход схаиы формирсжания импульса запуска распределителя записи ответа уст ройства ввода-вывода подсоединен ко входу распределителя записи ответа, выход которого соединен со входом кодовой части регистра команд устройства управления, с импульсным входс л вентилей запоминания оптимального адреса и с импульсными входами схгальц формирования адресной части команд устройства ввода-вьтода, потенциальные входы схемы запоминания оптималь ого адреса подключены ко входам ретистра оптимального ответа, а ее выходы связаны со схемой записи запоминающего устройства; потенциальные входы слемы формирования адресной части ксманд подключены ко входам буферного регистра нс лерав транспрртных средств, а ее выходы соединены с адресной частью регистра команд устройства управления, 2. Цифровая вычислительная машина по п. 1, о т л и ч а ю щ а я с я тем, что, с целью контроля возникающих неисправностей в арифметическом и логическом устройствах при выделении минимальной из ряда величин, схема логического контроля содержит вентиль контроля, потенциальный вход которого связан с одним из выходе схвиты анализа, количества выделенных адресов, а импульсный вход - с одним из выходе схемы формирования управляющих импульсов устройства управления; выход вентиля контроля соединен со входом запуска оснежного распределителя логического устройс ТВ а, со схемой сигнализации неисправности и счетчиком повторений, последняя разрядная ячейка которого подключена к схеме сигнализации и к схеме запрета формирсиаания управляющих импульсов основного решения. лппг yiftn I I I

Фи9.2 t

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА С АВТОМАТИЧЕСКИМ ПРОГРАММИРОВАНИЕМ И МИКРОПРОГРАММНЫМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1964 |

|

SU224161A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Система программного отбора игл на кругловязальных машинах | 1974 |

|

SU519515A1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Счетчик-таймер | 1975 |

|

SU711689A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

I /M II

0

J9

38

2 I

uz.3

rc.1

7

I

Pus Ч

C-LT-

V

Авторы

Даты

1981-02-28—Публикация

1968-04-29—Подача