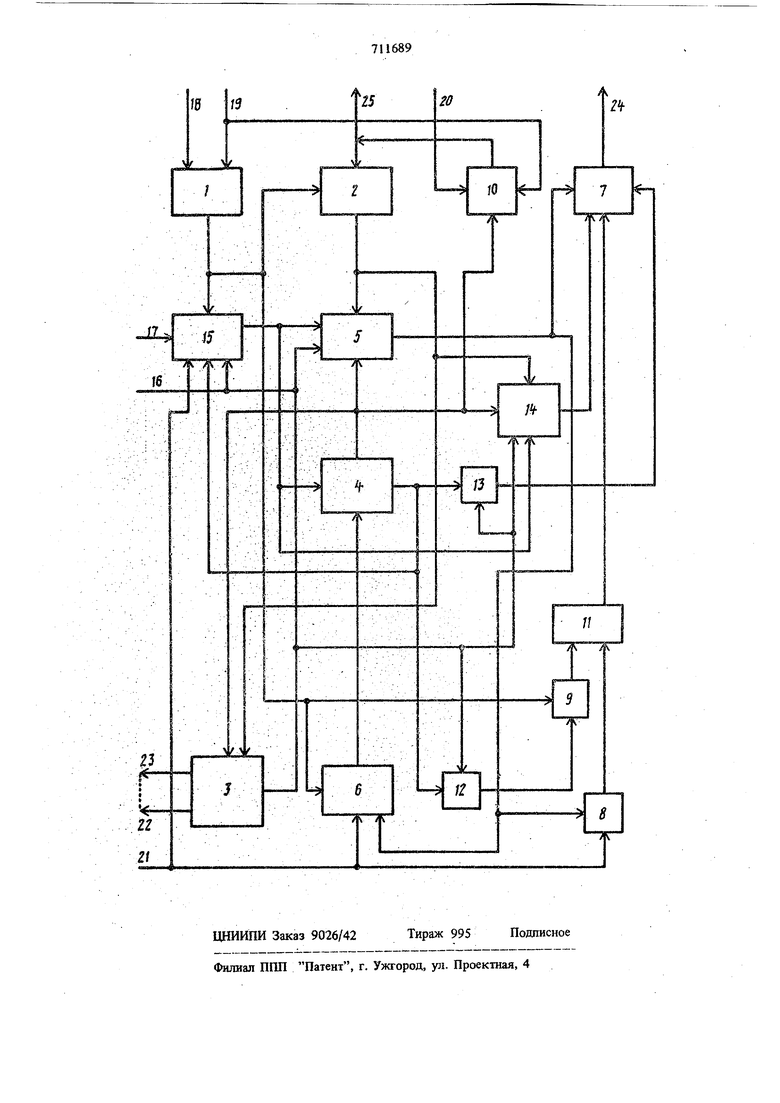

Изобретение относится к импульсной технике.. Известно устройство для счета и преобразова ния импульсною сигнала, содержащее дешифратор, арифметическое устройство, блок памяти с произвольным обращением, адресное устройство, блок сравнения, логические элементы управляющей логики, генератор, регистр, счетчики с устройствами записи и сброса 1. Недостатком данного устройства является его сложность. Наиболее близким по технической сущности к заявленному является устройство, содержащее входной логический элемент И, входы которого соединены с щинами сигналов записи и адреса, а выход которого подключен к первь1м входам регистра и логического элемента ИЛИ, второй вход которого подключен к шине сброса, третий вход соединен с выходом блока сравнения и первым входом выходного логичес кого элемента ИЛИ, второй вход которого через первый логический элемент И соединен с первым выходом счетчика и первым входом второго логического элемента И, вторые входы упомянутых логических элементов И соединены с первым входом блока сравнения, шиной сигнала управления режимом н первым входом дешифратора, второй вход которого соединен с регистром и вторым входом блока сравнения, третий вход которого подключен к третьему входу дешифратора и второму выходусчетчика, первый вход которого соединен с выходом . упомянутого логического элемента ИЛИ 1Й1.; Недостатком данного устройства является невозможность его использования в качестве широтно-импульсного модулятора и интерполятора. Целью изобретения является широтно-импульсная модуляция н интерполяция входных сигналов. Поставленная цель достигается тем, что в устройство, содержащее входной логический элемент И, входы которого соединены с шинами сигналов записи и адреса, а выход подключен к первым входам регистра и логического элемента ИЛИ, второй вход которого подключен к гшше сброса, третий вход соединен с выходом блока сравнения и первым входом выходногс логического элемента ИЛИ, второй вход которого ерез первый логический злемект И йоедине с первым выходом и первым входом второго логического элемента И, вторые, входы упомш1утых логических элементов И соединены с первым входом блока сравнения, шиной сигнала упразлекия режимом и первым входом де1Ш1фратора, второй вход которого соедлнен с регистром и вторым входом блока сравнения, третий вход которого подключен к третьему входу дешифратора и второму выходу счетчика, первый вход которо го соединен с выходом упомянутого логическо го элемента ИЛИ, введены два дополнительных логических элемента ИЛИ, триггер, логический элемент И-ИЛИ, блок вентилей и блок пуска, первый вход которого соединен с шиной счетного сигнала, второй вход - с шиной сброса, третий вход - с выходом счетчика, четвертый вход подключен к выходу иходного логнческс го элемента И, а выход-блока пуска соединен с дополнительным входом блока сравнения, вторым .входом счетчика и первым входом логического элемента И--ИЛИ, второй вход которого сое.динен с шиной сигнала управления режимом, третий вход подключён к выходу регистра. Четвертый вход соединен со вторым вы ходом счетчика и первым входом блока вентилей, второй вход которого соединен с шзшой сигнала адреса, третий вход - с шиной сигнала считывания, а выход подключен ко второму входу регистра, причем первьн вход одного до полнителыюго логического элемента ИЛИ соединен с шиной сброса, BTOpoji его вход соединен с выходом блока сравнения, а выход упомянутого дополнительного логического элемента ИЛИ соединен с первым входом триггера, выход которого подключен к третьему входу выходного логическ-ого элемента ИЛИ, четвертьн1 вход которого соединен с выходом /lorssческого элемента И-ИЛИ, при этом второй вход триггера соединен с выходом аторого допо;н1ительного логшеского элемента ИЛИ,- первый вход которого соединен с выходом входного логического элемента И, а на второй вход подключен к выходу второго из упомянутых логических элементов И, причем ять1Й вход блока пуска соединен с ищной сигнала управления режимом. Структурная электрическая схема описываемого устройства приведена на чертеже. Устройсгао содержит логический элемент И 1, регистр 2, дешифратор 3, счетчик 4, блок сравнения 5, логические элементы ИЛИ 6-9, блок вентилей 10, триггер 11, логические элементы И 12, 13, логический элемент И-ИЛИ 14, блок пуска 15. На входные шины 16, 17 поданы соответственно сигнал управления режимом и счетный сигнал, на цшнь 18, 19 поданы сигаал записи и сигнал адреса, на шину 20 подан сигнал сч15тьша шя, на ш.ину 21 подан сигнал сброса, с выходов 22, 23 снимаются информационные сигналы, с выхода 24, 25 снима1от.ся выходны.е управляющие сигналы. Устройство может работать в одном из основных режимов и представлять собой: а)делитель, распределитель, накопитель импульсов;б)регистр с дешифратором; в)формирователь задержки; г)модулятор (широтно-импу)); д)юггерполя ор. Выбор режима осуществляется подачей того или иного кодового потенциального сигнала на шину 16. Этот сигнал включает те цепи, которые должны сработать в выбранном режиме. Импульсы входной частоты поступают через входную и.шну 17 на вход блока пуска 15, который запускается от логического элемента И 1 при сигнале операции Запись, поступающему на вход по шинам 18, 19. По команде Запись и 1формация записьшается в регистр 2. Смысл кода в регистре 2зависит от режима работы. Так в режиме а он определяет коэффициент деления счетчика, в режиме б - информацию, передаваемую на выходы 22, 23 через ден1ифратор 3, в режимах в и г - длительность интервала времени, причем в режиме г обеспечивается цикличная работа, Б режим д регистр 2 хранит параллельный код, преобраэуемь Й в нитарный. Счетчик -1. и блок сравнения 5 обеспечивают соотаетстне;а О счет импульсов и сравнение их количества с содержимым регистра 2, т. е. с заданным кодом числа. Счетч-ик 4 сбрасьшается при операции Запись во всех реясимах. Со счетчика 4 параллельный код может быть считш НЕ выход 25 по команде Считывание, поступающей через шину 20 на логический элемеьл- И 1,. Код счетчика может бьггь также считан через дешифратор 3 на выходы 22, 23. Шина 21 обеспечивает первоначальную установку блока пуска 15, счетчика 4 через логический элемент ИЛИ 6, а также триггера 11 через логический элемент ИЛИ 8. Включение триггера 11 осуществляется через логический элемент ИЛИ 9 либо в момент команды по операции Запись, либо от логического элемента И 12, срабатывающего от импульса конца цикла счетчика (сигнал переполнения), поступающего с . переноса счетчнка. Функциональный выход 24 является выходом импульсов деления, выходом сигналов задержки, широтноимпульсной модуля ши и число-импульсного кода интерполятора. Логический элемент ИЛИ 7 транслирует сигнал либо с триггера 11, яиб 5.7 с логического злемен1-а И-ИЛИ J4 формироваШ1Я шсло-имп -льсиого кода, либо с блока сравнения 5, либо с логического элемента И 13. При работе в pe iajMe (;. имнульсы входной частоты через шину Г/ я блок isyci-ca IS поступают иа счегчнк 4 и на блозса сравнения 5, подключаемого к .логическому элементу ИЛИ 7 v. этоГЛ , появляется импульс S момент сравнегвш с кодом регистра 2, 31щисан и.1М в лего по команде Запись. Этот импульс вдет ка выход 24, а также через логический элемент ИЛИ 6 на сброс счетчика 4. Тем самым осуществляется деление на заданный коэффивдент. So всех режимах, кроме режима б, на дешифратор 3 ноступа ет импульс с параллельного выхода счетчика. В режиме б на выходы 22, 23 выводится информация с регистра 2, что при подключении к ним внешних логических элег 5ентов И либо ИЛИ (не показаны) позволяет осуществлять либо простую передачу информащш, либо передачу с дешифрацией или код1фованием. Логический элемент И 13 ; позволяет использовать в этом режиме и счетчик в качестве полнозаряд юто двоичного делителя (или накопителя). В в схема формирует интер вал времени, пропорциональный коду, записанному в регистр 2. Интервал времени снимается с триггера 11, который включается через логические элементы И 1 и ИЛИ 9, а выключает ся от логического элемента ИЛИ 8 и блока сравнения 5. В режиме г схе;ма работает так же, как и в режиме в с той разницей, что интервал вр мени генерируется с периодо.м двух импульсов который задается сигналом переполнения счетчика, поступающим через логический элемент И 12 и логический элемент ИЛИ 9 на триггер 11, обеспечивая повторные включения триггера В реядаме д логический элемент И-ИЛИ 14 обеспечивает форм1 рование весовых серий импульсов . от, счетчика 4 и их передачу на ло гический элемент ИЛИ 7 в тех разрядах, кото рые разрешены регистром 2. Логический элемент И-ИЛИ 14 обеспечивает равномерное рас пределение импульсов в-цикле. Импульсы конца 1щкпа (переполнение счетчика) сбрасывают блок пуска 15, в результате через выход 24 проходит число импульсов, рав ное коду. .Формула изобретения Счетчик-таймер, содержащий входной логический элемент И, входы которого соединены с шинами сип)алов записи и адреса, а выход подключен к первым входам регистра и логического элемента ИЛИ, второй вход которого 96 подключен к шине сороса, третий вход соедии.ен с выходом бло:са сравнен 1Я и первым входогд выходного лопг еского элемента ИЛИ, вход, которого через первый лог);ческич элемент И соединен с лервы.м в& ходом cicT4jfKa и первым входом второго логггаеского элемента И, втоpi.ie входы упомянутых логических элементов ; соединены с первым входом блока сравне:.;:ГЛ; unniv ; сигнала управления режимом и первым входом деипгфратора, второй вход которого соединен с реп-хтром и вторым входом блока сравнения, третей вход которого подключен к третьему входу дешифратора и второму выходу счетчика, первый вход которого соедиiieH с выходом упомянутого логического элемента , о т л . ч 3 ю щ н и с я тем, что, с целью широпю-импульсной модулящш и интерполяции входных сигналов, в него введены два дополнительных логических элемента ИЛИ, триггер. логический элемент И-ИЛИ, блок вентилей и блок пуска, первый вход которого соединен с шиной счетного сигнала, второй вход соедкнеи с цшной сброса, третий вход соедштен с выходом счетшка, четвертый вход подключен к выходу зходзюго лопиеского элегмента И, а выход блока нуоса соед1П1ен с дополнительным входом блока сравнеш;я, вторым входом счетчика и перЕыл входом логического элемента И-И.П.И, второй Бход которого соединен с ши;-:о;1 сип-гйла упраЕления режимом, третий вход подклгочен к выходу регистра, четвертый вход соед1п ск со втopы i выходом счетчика и первым входом :-JiOKa вентилей, второй вход которого соедане - с шшюй сигнала адреса, третий вход соединен с ь.шной сигнала считывания а выход лодкл;о«с;1 ко BTOpOiMy входу регистра, причем первыГ вход одного дополнительного логического элемента ИЛИ соединен с шиной сброса, нторой его вход с выходом блока сраБ1 е11ня. а упомянутого дополнительного логического элемента ИШЛ соединен с Первым входом триггера, которого подключен к третьему входу выходного логического элемента ИЛИ, четвертый вход которого соединен с выходом логического элемента И-ИЛИ, при эхом второй вход триггера соединен с выходом второго дополш1тельного ло- гического элемежа ИЛИ, первый вход которого соединен с выходом входного логического элемента И, а второй вход подключен к выходу второго из упомянутых логических элементов И, причем пятый вход блока пуска соединен с шиной сигнала управления режимом. Источ шки информации, npKiiHTbie во вкнмание при экспертизе 1.Патент США N 3849634, кл. 235-92 ДР, 19.11.74. 2.Патент США. № 3789195, кл. 235-92 Т, 29.01.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1196692A1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Многоканальный коммутатор аналоговых сигналов | 1988 |

|

SU1598149A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Арифметико-логическое устройство со встроенной диагностикой | 1984 |

|

SU1275426A1 |

| Аппарат магнитной записи | 1985 |

|

SU1297110A1 |

Авторы

Даты

1980-01-25—Публикация

1975-07-18—Подача