Изобретение относится к области автоматики и вычислительной техники.

Известно устройство для преобразования десятичных чисел в двоичные, реализующее алгоритм преобразования любого /г-разрядного десятичного числа в виде

(х, . + ... + Л1.10 + + Л„ (. 10 + )- 10+... + Л1. 10+Л„,

где (хз) - результат преобразования в двоичный код,

А -число единиц в i-ом разряде; разряды преобразуются по формуле

Л, .10 (Л,)-2.

Причем цифры преобразуемого числа вводятся в устройство поочередно вручную.

Предложенное устройство отличается тем, что входы четырехразрядного регистра памяти тетрад соединены с выходами двоично-десятичного регистра числа, счетчика тетрад и распределителя импульсов, а выход соединен с вентилем, соединенным по выходу с одним из входов сумматора, с которым через другой вентиль и линию задержки соединен выход регистра памяти результата, соединенный также с третьим вентилем, выход которого соединен со вторым входом сумматора, соединенным

также с выходом регистра памяти результата через четвертый вентиль и линии задерл ки; выходы сумматора соединены со входами регистра памяти результата, соединенного по входам также с выходами распределителя; схема управления соединена со чходами распределителя, вентилей и счетчика тетрад.

Это позволяет упростить схему устройства и повысить его надежность.

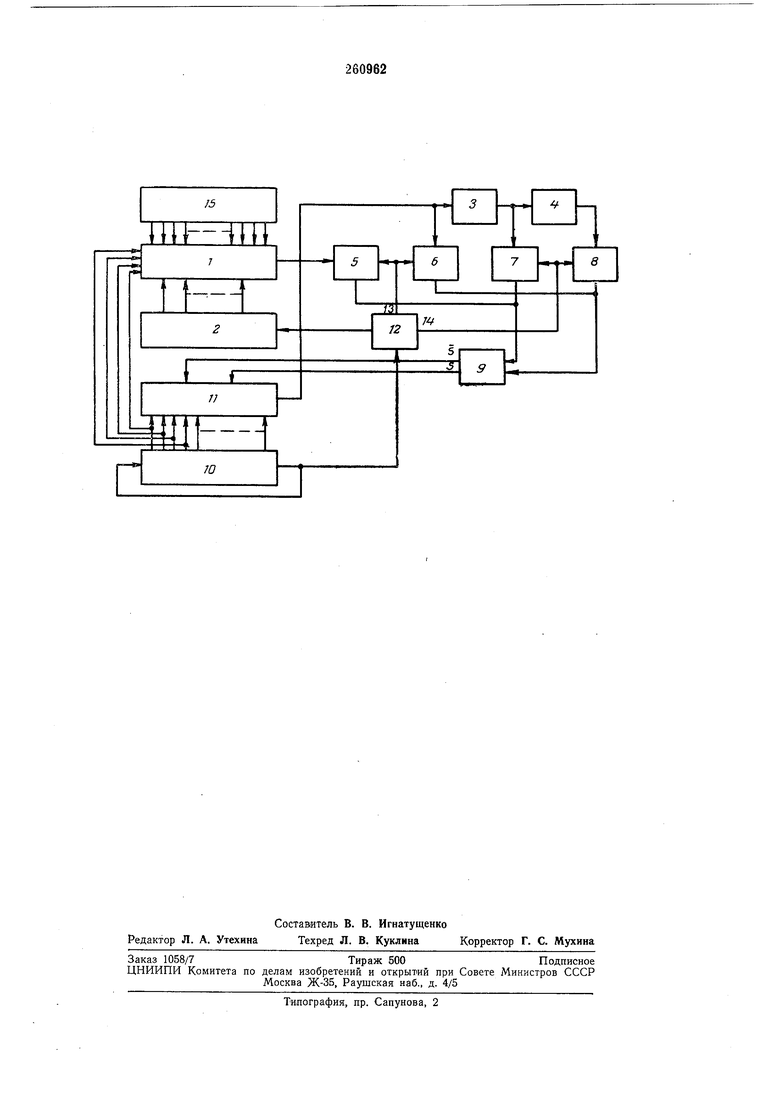

Схема устройства изображена ня чертеже.

Устройство содежит четырехразрядный регистр памяти тетрад /, счетчик тетрад 2, линию задержки 3, сдвигающую число на один двоичный разряд влево, линию задержки 4, сдвигающую число еще на два двоичных разряда влево, - вентили 5-5; од}10разрядный сумматор 9 с выходами S и 5; (т-f 1)-разрядный распределитель импульсов Ю (т- число двоичных разрядов преобразованного числа); регистр памяти результата //, содержащий т разрядов; схему управления 12 с выходами /5 и /4 и двоично-десятичный регистр числа /5.

Устройство работает следующим образом.

Схема управления 12 подает питание, производит установку схемы в исходное состояние (запись начальной «1 в распределитель импульсов 10 и счетчик тетрад 2), а также запускает генератор тактовых импульсов (на схеме не показан).

С началом работы генератора тактовых импульсов счетчик тетрад 2 через регистр памяти тетрад / производит первый опрос регистра числа 15 в результате чего в регистр памяти тетрад / заносится значение старшего разряда преобразуемого числа; одновременно с этим по выходу 13 открываются вентили 5, 5 канала сложения и начинается продвижение «1 по распределителю импульсов 10.

Выходные сигналы распределителя 10 производят считывание с предварительно очищенного регистра памяти результата 11 и с регистра памяти тетрад /.

Выходная информация регистра памяти результата // (в первом цикле работы - «О) и регистра памяти тетрад 1 поступает через открытый вентиль 6 на первый вход сумматора 9, а через вентиль 5 на второй вход сумматора. Выходной сигнал сумматора 9 задерживается по отношению ко входному на один такт.

Если в результате суммирования получается «1, то сигнал появляется на выходе сумматора 5, если же «О - на выходе S. Наличие сигнала S позволяет замкнуть цепь выходного сигнала распределителя 10 без записи «1 в регистр памяти результата 11.

В случае, если результат суммирования равен «1, то наличие сигнала 5 позволяет замкнуть цепь выходного сигнала распределителя 10 с записью «1 в регистр памяти результата 11.

В последнем такте работы распределителя 10 заканчивается цикл суммирования, в первый разряд распределителя вносится «1 для организации следующего цикла работы; схема управления 12 закрывает вентили 5 и 6, а вентили 7 и 5 открывает по выходу 14. Устройство переходит в режим умножения.

При новом цикле движения импульсов в распределителе 10 его выходные сигналы производят считывание информации с регистра памяти результата 11, выходные сигналы которого через линии задержки 3 Е 4 и вентили 7 и S поступают на вход сумматора 9.

Результат суммирования (равный Aa-i 10) вновь заносится в регистр памяти результата // аналогично описанному выше.

После окончания цикла умножения схема управления 12 закрывает вентили 7 и S открывает вентили 5 Е 6, а счетчик тетрад 2 подает сигнал на ввод следующей тетрады в регистр памяти тетрад 1.

Устройство отрабатывает следующий цикл слол :ения, но теперь складывается содержимое регистра памяти результата 11 со значением следующей цифры преобразуемого числа. Затем следует цикл умножения и т. д.

Процесс преобразования заканчивается прибавлением к произведению получившемуся в результате последнего умножения на 10, младшей цифры десятичного числа. В регистре памяти результата 11 образуется число, преобразованное в двоичный код.

Предмет изобретения

Устройство для преобразования двоично-десятичных чисел в двоичные, содержащее двоично-десятичный регистр числа, четырехразрядный регистр памяти тетрад, счетчик тетрад, регистр памяти результата, распределитель импульсов, линии задержки, вентили, одноразрядный сумматор и схему управления, отличающееся тем, что, с целью упрощения схемы и повышения ее надежности, входы четырехразрядного регистра памяти тетрад соединены с выходами двоично-десятичного регистра числа, счетчика тетрад и распределителя импульсов, а выход соединен с вентилем, соединенным по выходу с одним из входов сумматора, с которым через другой зентиль и линию задержки соединен выход регистра памяти результата, соединенный также с третьим вентилем, выход которого соединен со вторым входом сумматора, соединенным также с выходом регистра памяти результата через четвертый вентиль и линии задержки; выходы сумматора соединены со входами регистра памяти результата, соединенного по входам также с выходами распределителя; схема управления соединена со входами распределителя, вентилей и счетчика тетрад.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1972 |

|

SU437069A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1280702A1 |

| МАСШТАБИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU360661A1 |

| Н И Е ЕНИЯ | 1973 |

|

SU393739A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ | 1972 |

|

SU356642A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ В ДВОИЧНЫЕ | 1972 |

|

SU329525A1 |

Даты

1970-01-01—Публикация