Изобретение относится к устройству преобразования частоты повторения импульсов в цифровой код, предназначенному для. непрерывного кодирования текущих значений часто ты повторения импульсов. Оно может использоваться при цифровом измерении частоты, изменяющейся ио пронзвольному закону, при вводе информации от частотных датчиков в цифровую вычислительную мащину (ЦВМ) и т. д.

Известен преобразователь частоты в цифровой код, содержащий источники измеряемой и эталонной частот, делитель эталонной частоты, триггеры и вентили. Он представляет собой частотно-импульсную следящую систему с обратной связью, включающую дискриминатор частот повторения входных имнульсов и импульсов обратной связи, реверсивный счетчик импульсов разностной частоты и преобразователь цифрового кода в частоту в цепи обратной связи. Результат кодирования в реверсивном счетчике выражает текущее значение частоты и может считываться в любой момент времени.

Недостатками известного устройства являются нелинейная зависимость между результатом кодирования (числом в реверсивном счетчике) и частотой входного сигнала, относительно больщое время переходного процесса, затрудняющее применение устройства при

быстрых изменениях частоты, и неизбежп.лс автоколебання результата около установившегося значения в нределах единнцы младшего разряда.

Цель изобретения - повысить точность и быстродействие преобразователя.

Это достигается тем, что источник измеряс.мой частоты соединен с единичным входом первого триггера и имиульсиым входом вентиля,

управляемого этим триггером; выход вентиля подключен к единичному входу второго триггера и импульсному входу вентиля, управляемого вторым триггером; нулевой выход второго триггера соединен с управляемым входом

вентиля, импульсный вход которого подключен к источнику измеряемой частоты, а выход этого вентиля связан с выходом вентиля, управляемого вторым триггером; выход дeлигeлvl эталонной частоты соединен с нулевым входом первого триггера и импульсным входом вентиля, управляемый вход которого связан с нулевым выходом первого триггера, а выход этого вентиля соединен с нулевым входом второго триггера.

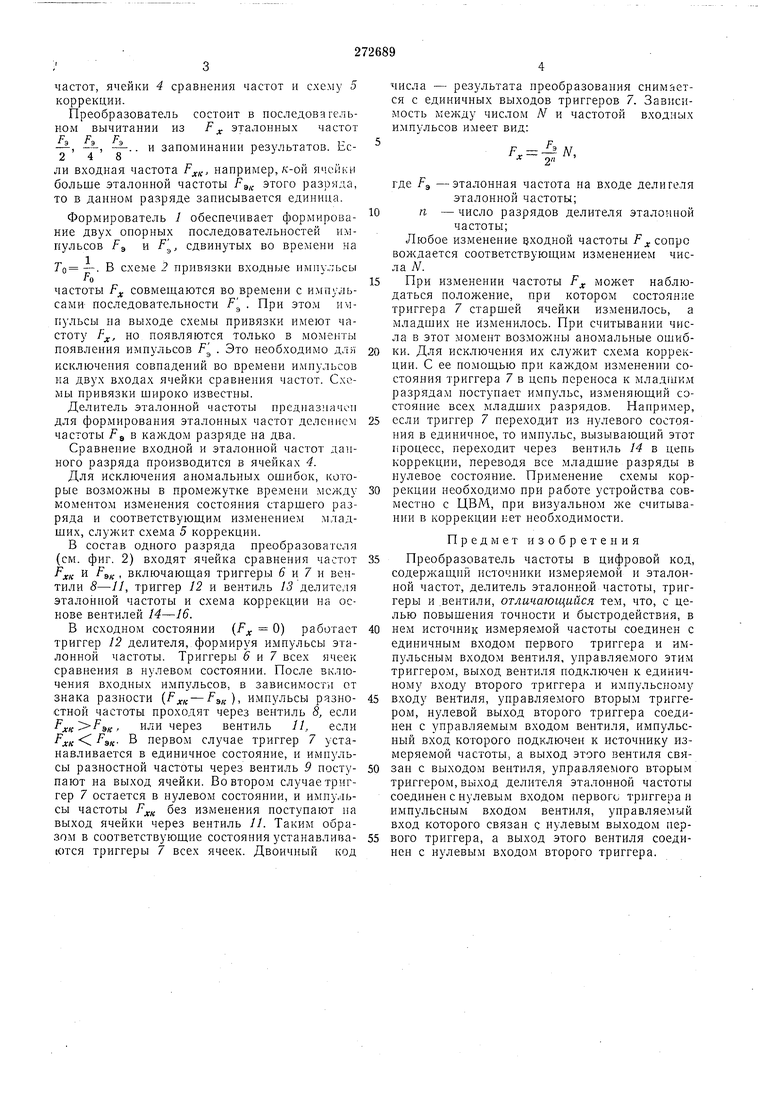

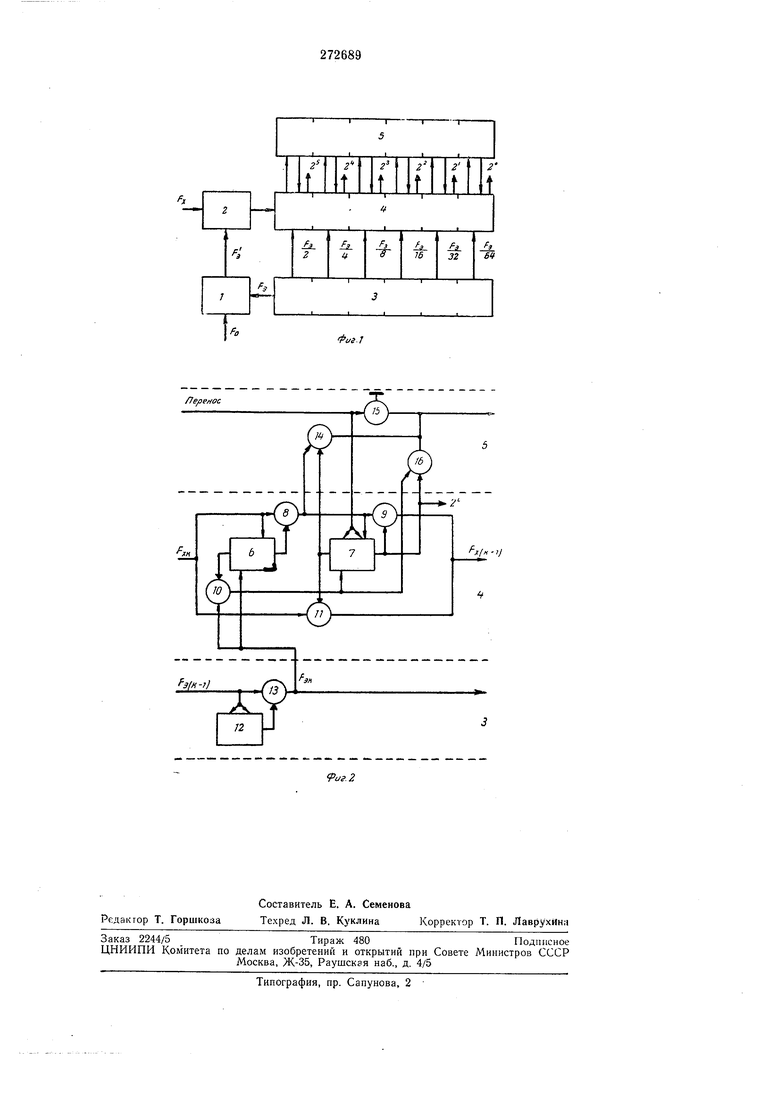

На фиг. 1 дана общая схема онисываемого преобразователя, а на фиг. 2 - один разряд преобразователя.

Преобразователь содержит формирователь / эталонных частот, схему 2 привязки входных

частот, ячейки 4 сравнения частот и схему 5 коррекции. Преобразователь состоит в последовагельF г эталонных

частот

из

ном вычитании

F F F

-, -, -.. и запоминании результатов. Ес248

ли входная частота F., например, к-ой ячейки больше эталонной частоты Fg/c этого разряда, то в данном разряде записывается единица.

Формирователь / обеспечивает формирование двух опорных последовательностей импульсов FS и fj, сдвинутых во времени на

Го -. В схеме 2 привязки входные импу.льсьг

0

частоты F, совмещаются во времени с импульсами последовательности F . При этом импульсы ца выходе схемы привязки имеют частоту Fjf, но появляются только в моменты появления импульсов f . Это необходимо для исключения совпадений во времени импульсов на двух входах ячейки сравнения частот. Схемы привязки широко известны.

Делитель эталонной частоты прсдназначоп для формирования эталонных частот делением частоты Fg в каждом разряде на два.

Сравнение входной и эталонной частот данного разряда производится в ячейках 4.

Для исключения аномальных ошибок, которые возможны в промежутке времени между моментом изменения состояния старшего разряда и соответствуюш.им изменением младших, служит схема 5 коррекции.

В состав одного разряда преобразователя (см. фиг. 2) входят ячейка сравнения частот хк и 9к 1 включающая триггеры б и 7 и вентили 8-11, триггер 12 и вентиль 13 делителя эталонной частоты и схема коррекции на основе вентилей 14-16.

В исходном состоянии (F 0) работает триггер 12 делителя, формируя импульсы эталонной частоты. Триггеры 5 и 7 всех ячеек сравнения в нулевом состоянии. После включения входных импульсов, в зависимости от знака разности (f - эк} импульсы разностной частоты проходят через вентиль 8, если

F.PB

ИЛИ через вентиль 11, если

С зк- в первом случае триггер 7 устанавливается в единичное состояние, и импульсы разностной частоты через вентиль 9 поступают на выход ячейки. Во втором случае триггер 7 остается в нулевом состоянии, и импульсы частоты Fj без изменения поступают па выход ячейки через вентиль 11. Таким образом в соответствующие состояния устанавливаются триггеры 7 всех ячеек. Двоичный код

числа - результата преобразования снимается с единичных выходов триггеров 7. Зависимость между числом N и частотой входных и.мпульсов имеет вид:

п

Л,

где э

эталонная частота на входе дели геля эталонной частоты;

п -число разрядов делителя эталонной

частоты;

Любое изменение входной частоты f conpo вождается соответствующим изменением числа N.

При изменении частоты F. может наблюдаться положение, при котором состояние триггера 7 старшей ячейки изменилось, а младших не изменилось. При считывании числа в этот момент возможны аномальные ошибки. Для исключения их служит схема коррекции. С ее помощью при каждом изменении состояния триггера 7 в цепь переноса к младшим разрядам поступает импульс, из.меняющий состояние всех младших разрядов. Например,

если триггер 7 переходит из нулевого состояния в единичное, то импульс, вызывающий этот процесс, переходит через вентиль 14 в цепь коррекции, переводя все младшие разряды в нулевое состояние. Применение схемы коррекции необходимо при работе устройства совместно с ЦВМ, при визуальном же считывании в коррекции нет необходимости.

Предмет изобретения

Преобразователь частоты в цифровой код, содержащий источники измеряемой и эталонной частот, делитель эталонной частоты, триггеры и .вентили, отличающийся тем, что, с целью повышения точности и быстродействия, в

нем источник измеряемой частоты соединен с единичным входом первого триггера и импульсным входом вентиля, управляемого этим триггером, выход вентиля подключен к единичному входу второго триггера и импульсному

входу вентиля, управляемого вторым триггером, нулевой выход второго триггера соединен с управляемым входом вентиля, импульсный вход которого подключен к источнику измеряемой частоты, а выход этого вентиля связап с выходом вентиля, управляемого вторым триггером,выход делителя эталонной частоты соединен с нулевым входом первого триггера и импульсным входом вентиля, управляемый вход которого связан с нулевым выходом первого триггера, а выход этого вентиля соединен с нулевым входом второго триггера.

J

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТЫ В ЦИФРОВОЙ КОД | 1969 |

|

SU240345A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Устройство преобразования сигнала с датчика | 1989 |

|

SU1651364A1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Устройство для преобразования частоты | 1981 |

|

SU1008904A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 2000 |

|

RU2170444C1 |

| Устройство для ввода информации | 1989 |

|

SU1645949A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2038694C1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| Аналого-цифровой преобразователь с цифровой коррекцией погрешностей | 1978 |

|

SU788374A1 |

fslH-JJ

Даты

1970-01-01—Публикация