Данное изобретение относится к области цифровых диффереициальных анализаторов (ЦДЛ).

Известио суммирующее устройство дискретных прираш,еиий для цифрового диффереициального анализатора, содержащее триггеры и вентили.

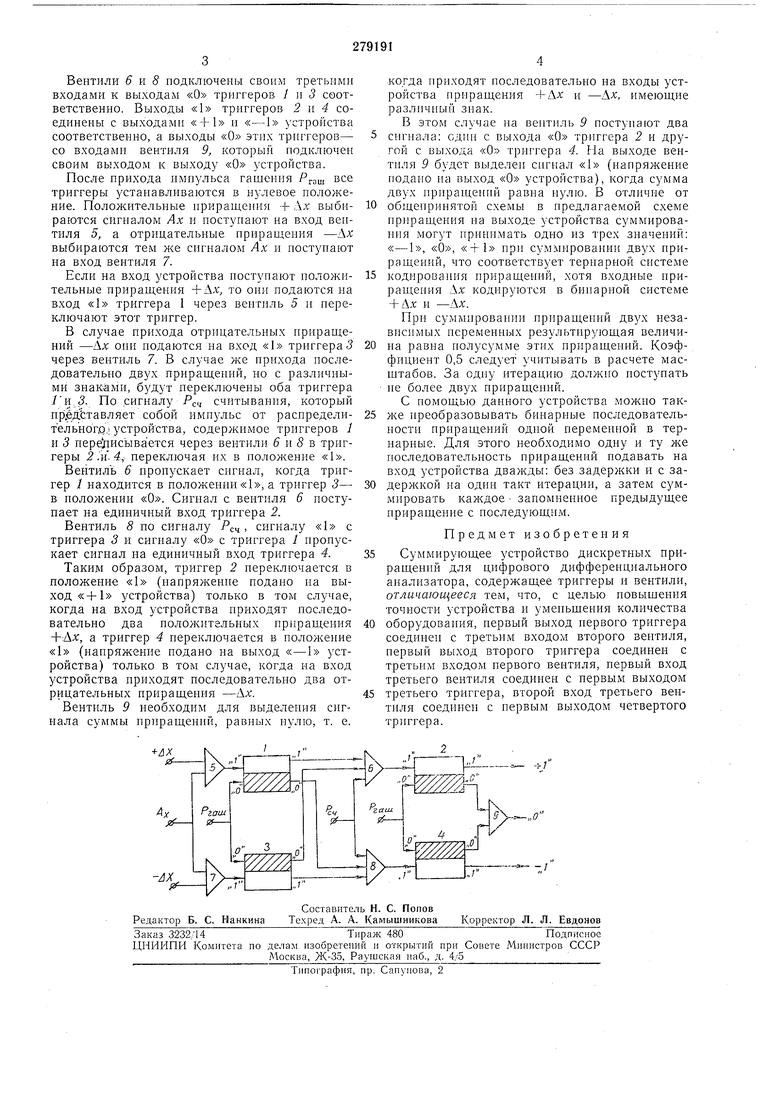

Предлагаемое устройство отличается от известного тем, что иервый выход первого триггера соединен с третьим входом второго вентиля, первый выход второго триггера соединен с третьим входом первого вентиля, иервый вход третьего вентиля соедииеи с первым выходом третьего триггера, второй вход третьего веитиля соединен с первым выходом четвертого триггера.

Это позволяет повысить точность устройства и уменьщить количество оборудования.

Известны два принципа кодироваппя приращений в ЦДА: бинариый ( + 1; -I) и териарный ( + 1; 0; -1). Опыт создаиия ЦДА показал, что ЦДА с тернарной системой кодироваиия приращений требуют большего объема оборудовапия, однако ЦДЛ с бнпарной системой имеют ограниченную область применения.

Педостаток этот заключается в том, что при бинарном кодировании ириращепий и ири длительном времени рещения иоявляется накапливающаяся фазовая ощибка, что неприемлемо для навигационного вычислительного устройства. Умепьщения фазовой ощибки ЦДА можно добиться ирименением смешанной системы кодироваиня ириращеиий, сущиость которой состоит в том, что в осиовном кодировакие п передача информацнн в ЦДА осуществляются в бииариой системе, а в тех узлах, где может возннкать фазовая ощпбка, производится местиое преобразованпе кодироваиия ирпращений из бинарной в тернарную систему.

Преобразование бинарного кодирования последовательности прпращеиий в тернарное основано па том, что сумма двух бинарных приращеннй в любом случае может быть равна одному из трех зиачепий. одно из которых нуль, а два другнх равны между собой но абсолютному значенню, но нмеют различные знаки, что является основным тернарным призиаком кодирования приращеиий.

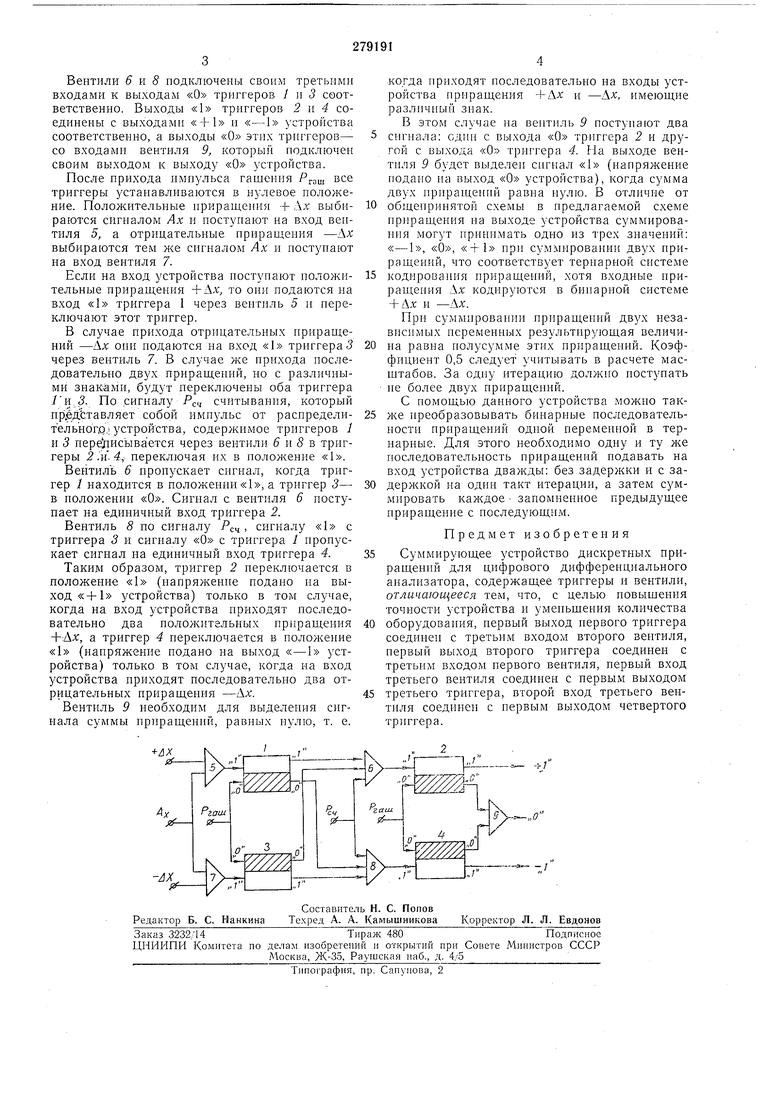

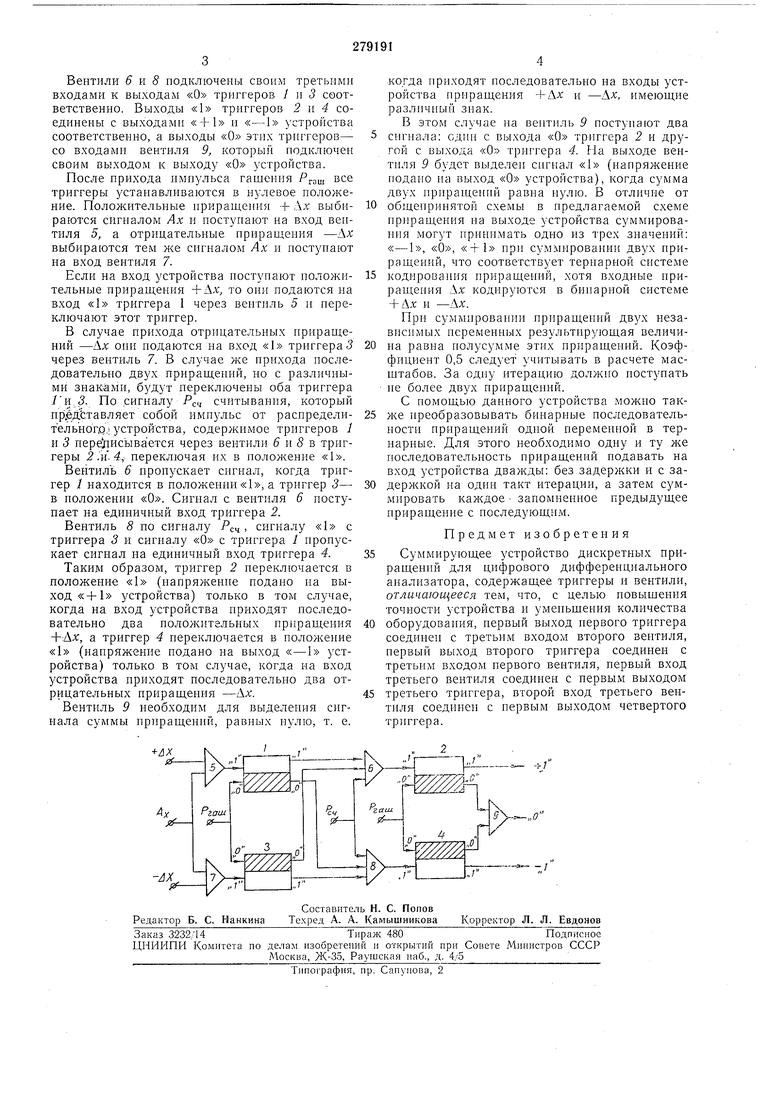

Устройство, схема которого приведена на чертеже, состоит из четырех триггеров 1-4 и пяти вентнлей 5-9.

Устройство нмеет три входа и три выхода.

Ко входу + ирпсоедииеиы последовательно вентиль 5, триггер /, вентиль 6 и триггер 2. Ко входу нрисоедииены последовательно вентиль 7, триггер 3, веитиль 8 и триггер 4. Вентили 5 ц 7 нодключены своими вторыми

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР ПОСЛЕДОВАТЕЛЬНОГО ТИПА | 1970 |

|

SU281025A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1971 |

|

SU294157A1 |

| УСТРОЙСТВО ПАМЯТИ ПРИРАЩЕНИЙ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО АНАЛИЗАТОРА | 1968 |

|

SU222031A1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU294156A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1973 |

|

SU387395A1 |

| Устройство соединения интеграторов | 1961 |

|

SU146097A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1972 |

|

SU415676A1 |

| Устройство для отображения графи-чЕСКОй иНфОРМАции HA эКРАНЕ элЕКТРО-HHO-лучЕВОй ТРубКи | 1979 |

|

SU834739A1 |

| Дифференцирующее устройство | 1984 |

|

SU1264170A1 |

Даты

1970-01-01—Публикация