Изобретение относится к области вычислительной техники: к уиравля10ш;им машипсш, применяемым в бортовой аииаратуре.

Известны цифровые диффереридиальные анализаторы (ЦДА) носледовательно-иараллельного тина, содержащие накапливающие сумматоры, коммутаторы, регистры храие)1ия приращений, запоминающие устройства, устройства для вычисления нодынтегральных функций.

Для известных анализаторов характср1И)1 сравнительно малое быстродействие и большое количество оборудования.

В иредложеипом анализаторе увеличение быстродействия и упрощение блока унравления достигаются путем жесткого соединения блоков между собой в онределенном порядке, необходимом для одновременного вычисления приращений направляющих косинусов.

С этой целью выходы блоков запоминания соединены со входами блоков вычисления нодынтегральных функций, другие входы которых соединены с выходами блока хранения квантовых приращений, выходы блоков вычисления подынтегральных функций соединены с одними входами блоков запоминания, с ишнами ввода информацин и вывода, с одними входами коммутаторов и через преобразователи с другими входами коммутаторов, а осталыиле входы коммутаторов соединены с

выходами блока ввода, соединенного тремя входными ujuHaNni с нрав.1ясмым объектолг и с одним выходом блока управления, один выход первого коммутатора соединен с первым входом второго сумматора, а другой выход соединен с iiepB-iiAi входом третьего сумматора, однн выход второго коммутатора соедипсп со вторым входом третьего сумматора, а друго выход сосдиген со вторым входом первого сумматора, один выход третьего коммутатора соединен с нсрвым входом иервого сумматора, а выход соедипен со вторым входом второго с мматора. выходы сумматоров соединены с одннми входамн корректируюни1х блоков, а другие их входы соединены со вторым В1з1ходом блока унравления и с другими входами блоков заиомннання, выходы корректируюни1х блоков соединены с одними входами формирователей, другие входы которых сосдинеиы с третьим выходом блока унравлепия, четвертый выход которого соединен с одним входом блока хранения информации, другие входы которого соединены с выходами формнрователей.

Вычисление на чавляющих косинусов оиределяется алгоритмом:

v /lyOi-I) - /2/;i гЗОИ) 3/,;

Ч 92{/i i); (/1-);

, 2, 3;

l-ij-косинус угла, образованного i-й осью объекта (1, 2, 3) и /-и ииерциальной осью; Уф;п-приращение угловых перемещений

текущей информации.

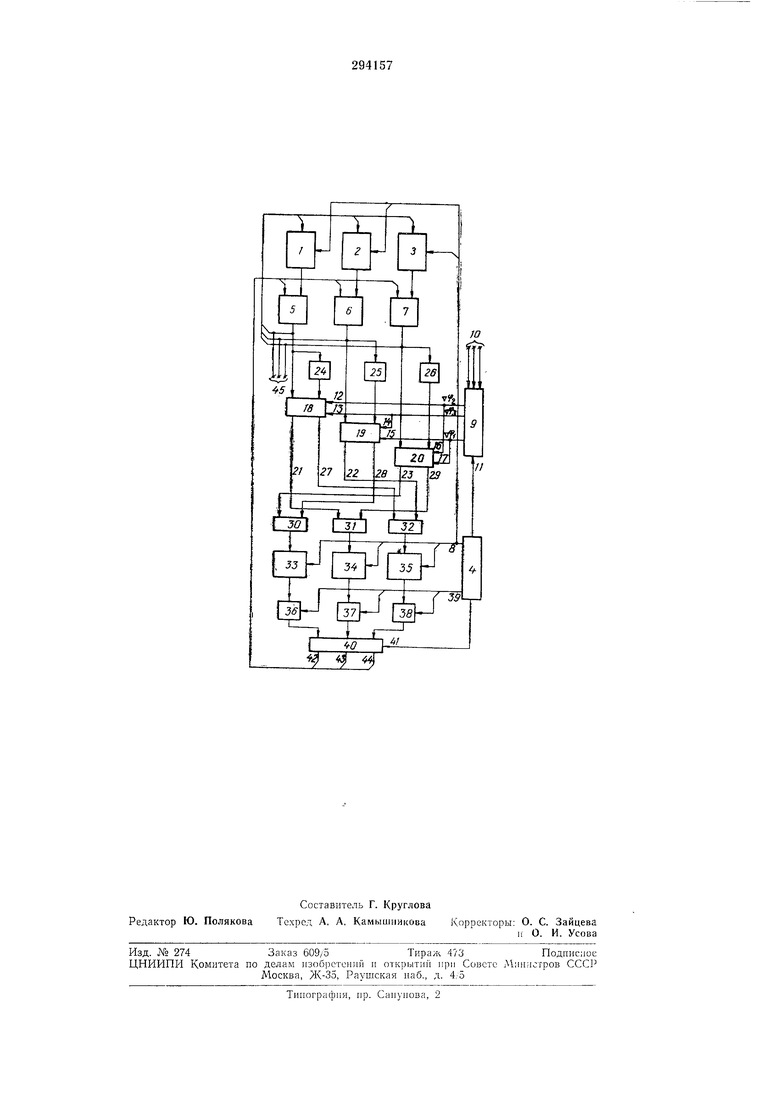

На чертеже ириведена блок-схема цифрового дифферецциального анализатора.

В состав каждого из блоков /-3 заномииающих ячеек входят три ячейки, предназначенные для прие.ма, хранения и выдачи последовательных кодов трех направляющих косинусов. Направляющие косинусы 1и, , ks хранятся в блоке /; /2i, /22, 23 - в блоке 2; а /зь /32, - в блоке 3. В качестве запоминающих ячеек .целесообразно использовать динамические линии задержки или регистры.

Блок 4 управления служит для управления всеми блоками ЦДЛ с помощью вырабатываемых в нем управляющих сигналов.

В начале каждого этапа интегрирования в блоки запоминающих ячеек /, 2, 3, а также в блоки 5-7 коррекции с выхода 8 блока 4 поступает сигнал управления, комм тпруюн1ий запоминающие ячейки.

Блоки 5-7 предназначены для вычисления на каждом шаге интегрнрования новых значений подынтегральных функций, представляющих собой направляющие косинусы.

Но сигналу управления с выхода 8 блока 4 запоминающие ячейки блоков 1-3, которые хранят направляющие косинусы, необходимые для интегрирования на данном этапе, подключаются соответственно к блокам 5, 6, 7 в качестве У-регистров.

Блок 9 ввода текущей информации предназначен для преобразования в поток приращений информации, иоступаюнхей обычно в виде ненрерывных величин на его входные шины 10 от унравляемого объекта.

Неред каждым marOiM интегрирования по сигиалу, постунающему из блока управления 4 на вход // блока 9, на входах 12-П коммутаторов /8-20 устанавлнваются новые значения нриращеипй независимых неременных, которые фиксируются в течение всего nuira интегрирования. На входах 15, П фиксируется приращение иезависимой переменной V((,i; на входах 12, 16 - Vcpa; на входах 13, 14 -

Уфз,

Каждый из коммутаторов 18-20 состоит из четырех двухвходовых схем совнадения и двух собирательных схем на два входа. Коды направляющих косинусов с выходов блоков 5- 7 проходят соответственно на выходы 21-23, если текущая информация, ноступающая соответственно на входы 13, 15, 16, имеет отрицательный знак. Если текущая инфор1мация имеет положительный знак, то на выходы 21-23 проходят коды с выходов нреобразователей кодов 24-26. Носледовательные коды направляющих косинусов проходят на выходы 27-29 с выходов блоков, соответственно 5-7, если текущая информация, поступающая соответственно на входы 12, 14, 17, и.меет положительный знак. Если текущая информация с отрицательным знако.м, то на выходы 27-29 нроходят коды с выходов преобразователей 24-26.

5 Нреобразователи кода последовательного действия 24-26 предназначены для перехода от кодов направляющих косинусов, поступающих на их вход, к дополнительным кода.м этих же величин.

10 Если на какой-либо вход коммутатора не поступает текущая информация, то на соответствующий выход этого коммутатора не проходит код направляющего косинуса. Так, например, если Уф1 0, то на выходы 22 и 29 15 коммутаторов 19 и 20 не проходят коды соответствующих направляющих косинусов.

На выходах сумматоров 30-32 получаются неквантованные приращения нанравляющих косинусов, соответственно V/u, V/2i, V/3j. 20

Корректирующие блоки 33-.35 предназначены для коррекции неквантованных приращений направленных косинусов, вычисленных на данном щаге интегрирования, путем их 5 сложения с хранимыми в этих блоках остатками тех приращений направляющих косинусов, которые были вычислены и скорректированы на предыдущем шаге интегрирования. Каждый корректирующий блок состоит из 0 двухвходового сумматора последовательного действия и блока запоминающих ячеек, аналогичного блокам 1-3. Запо.минающие ячейки блоков 33-35 используются в качестве R-регистров.

5 Выходы сумматоров 30-32 соединены со входами сумл1аторов блоков 33-35 соответственно. Вторые входы этих сум.маторов сигнало.м управления подключаются к выходам тех запоминающих ячеек, которые хранят 0 остатки приращений, необходимых для осуществления коррекции на данном этапе интегрирования.

Формирователи квантованных приращений 36-38 по сигналу с выхода 39 блока 4 ана5 лизируют два разряда, поступающие на их вход после разрядов, воспроизводящих цифровую часть неквантованных скорректированных приращений направляющих косинусов, и формируют квантованные значения этих при0 ращений по тернарной систе.ме кодирования нриращений.

Блок 40 служит для приема, хранения и выдачи квантованных приращений направляющих косинусов. Неред кажды.м этапом интегрирования по сигналу управления, поступающему из блока 4 на вход 41 блока 40, квантованные приращения направляющих косинусов V/1,-, V/2J, V/3J с выходов 42-44 соответственно поступают на входы блоков 5-7. Шины 45 предназначены для ввода исход)1ой информации и вывода результатов решения задачи.

Y-регистров на рассматриваемом этапе интегрирования и входящих в состав блоков /-.Л направляющие косинусы ), izjin-i), /злп-п, вычисленные па предыдущем шаге интегрирования, в последовательном коде поступают па входы блоков 5-7 соответственно. Одновременно на вторые входы этих блоков поступают квантованные приращения направляющих косинусов V/ij,,, V/2j7b V/s.in с выходов блока 40.

Новые значения направляющих косинусов , l2m, Izjn с выходов блоков 5-7 В последовательпом коде поступают в блоки /-3 соответственно и записываются в запоминающие ячейки, используемые в качестве Y-регистров на данном этапе интегрирования.

Одновременно новые значения направляющих косинусов с выходов блоков 5-7 поступают непосредственно, а также через преобразователи кодов 24-26 соответственно па входы коммутаторов 18-20.

Для управления на два остальных входа каждого коммутатора поступают приранюния двух независимых переменных.

Последовательный код неквантованного приращения направляющего косинуса V/ij(n-:-n постунает на вход блока 33 с выхода сумматора 30. На входы последнего поступают последовательные коды приращений слагаемых /2jnVфз-/ззпУфа с выходов 28, 23 коммутаторов 19, 20 соответственно. На вход блока 34 поступает последовательный код неквантованного приращения направляющего косинуса V/2j{n-i-i) с выхода сумматора 31. На вход последнего подаются в последовательном коде неквантовапные приращения слагаемых /з.;пАф1-/i:mV93 С ВЫХОДОВ 29, 21 коммутаторов 20, 18 соответственно. Последовательные коды неквантованных нриращений слагаемых /ljnVф2-/2.inVфl поступают на входы сумматора 32 с выходов 27, 22 коммутаторов 18, 19 соответственно. Неквантованное прнрап;ен1 е V/3j(n-fi) с выхода сумматора 32 в последовательном коде проходит на вход блока 35.

В корректирующих блоках 33-35 поступающие на их вход приращения направляющих косинусов суммируются с остатками приращений направляющих косинусов, вычисленных на предыдущем щаге интегрирования. Цифровые части неквантованных скорректированных приращений направляющих коси)усов с выходов сумматоров блоков коррекпии поступают в запоминающие ячейкп, используемые на рассматриваемом этане в качестве R-регистров.

Старщие разряды (знаковый, а также разряд, следующий за ним) неквантованных скорректированных прпран1,енпй паправляющих косинусов поступают последовательно с выходов блоков 33-35 )ia входы формпрователей квантованных приращенщ 36-38, открытые сигналом на выходе 39 блока 4.

Квантованные приращения V/i.i(+n. У/2,;(я+п, V/3,;(7i-i) с выходов формирователей 36-38 соответственно поступают в блок 40 для храпения в течение двух последующих этапов.

Нре

д м е т

изооретения

Ннфровой дпфференцпальный анализатор для вычисления направляющих косинусов, содержащий запомппающие блоки, блоки вычисления подыщ-егральпой функции, преобразователи кодов, коммутаторы, сумматоры, корректирующие блоки, формирователи квантовых нрираи1.ен1п, блоки хранения квантовых приращений, блок управлення, блок ввода, отличающийся тем, что. с целью увеличення быстродействия, выходы блоков запоминания

соединены со входами блоков вычисления подынтегральных функций, другие входы которых соединены с выходами блока хранения квантовых приращений, выходы блоков вычисления подынтегральных функций соединены с одннмп входами блоков зaпo rинaния, с щинами ввода информации и вывода, с однимн входами коммутаторов и через преобразователи с другими входами коммутаторов, а остальные входы коммутаторов соединены с

выходами блока ввода, соединенного тремя входными щипами с управляемым объектом и с одппм выходом блока управления, один выход первого коммутатора соедннен с первым входом второго сумматора, а другой выход

соединен с первым входом третьего сумматора, один выход второго коммутатора соединен со вторым входом третьего сумматора, а другой выход соединен со вторым входом первого сумматора, один выход третьего коммутатора соединен с первым входом первого сумматора, а др)той выход соединен со вторым входом второго сумматора, выходы сумматоров соединены с одними входами корректирующих блоков, а другие их входы соедииены со вторым выходом блока управлення и с другими входами блоков заиомипания, выходы корректирующих блоков соединены с одними входами формирователей, другие входы которых соединепы с третьим выходом

блока управления, четвертый выход которого соединен с одним входом блока хранения ипформацпп, другие входы которого соединены с выходами формирователей.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1973 |

|

SU387395A1 |

| Интегрирующее устройство интегрирующей машины последовательного типа | 1974 |

|

SU526927A1 |

| Цифровой интегратор | 1974 |

|

SU519735A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| Интегро-арифметическое устройство | 1977 |

|

SU746602A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор для решения краевых задач | 1984 |

|

SU1211712A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

Даты

1971-01-01—Публикация