1

Изобретение относится к управляющим машинам, применяемым в бортовой аппаратуре для решения задачи определения ориентации летательных аппаратов.

Известен цифровой дифференциальный анализатор для решения системы разностных уравнений.

VU (n+l) a/nVT3 (я-f 1) - (п + 1). V2y(n+l) itJnVfl(it-}l) - f,jnVf3(n + l),(1)

VS; (n+1) (nf 1) - l JnVfl (n+I).

У 1,2,3...

связываюш,их направляюш,ие косинусы и угловую скорость летательного аппарата, в котором учтены все особенности системы уравнений Н1аправляюш,их косинусов. В этом ЦДЛ на шаге интегрирования новое значение каждого направляюш.его косинуса вычисляется один раз я поступает в качестве подинтегральной функции непосредственно, а также через преобразователь кода на входы специального коммутатора, управляемого прираш,ениями двух независимых переменных. В качестве независимых переменных используется текущая информация Vffi с соответствующих датчиков. С ВЫХОДОВ коммутатора снимаются некванггованные приращения сразу двух .слагаемых системы уравнений (1), которые содержат в качестве сомножителя один и тот же направляющий косинус.

Увеличение быстродействия и упрощение блока управления достигается путем жесткого соединения в выщеуказанйом ЦДЛ блоков между собой в определенном порядке, необходимом для одновременного вычисления приращений трех направляющих косинусов, согласно алгоритму (1). Так как , 2, 3, то вычисление приращений девяти направляющих косинусов на -каждом шаге интегрироваНИН осуществляется в три этапа, на каждом этапе реализуя алгоритм (1) с конкретным значением /. По сравнению с обычным ЦДЛ последовательного типа, предназначенного для вычисления направляющих косинусоч,

быстродействие прототипа увеличено в 6 раз, а оборудование его возросло всего на два цифровых ИНтегратора. Однако, прототип имеет тот недостаток, что ов оперирует с квантованными приращениями направляющих косинусов, что не позволяет использовать возможность сокращения затрат оборудования, потенциально заложенных в его структуре. Использование квантованных приращений связано не только с расходом оборудования, необходимого для кор.рекции некваитованвых приращений, квантования их и хранения квантованных приращений, но и с ухудщением точности вычислений текущих значений направляющих косинусов.

Цель изобретения - дальнейшее сокращение расхода ооорудования на построение ЦДЛ, для вычисления направляющих косинусов, а также повышение точности этих вычислений. Это достигается с помоидыо новых связей блоков ЦДА, позволяющих оперировать полноразрядными приращениями направляющих косинусов. В предлагаемом ЦДА каждая из запоминающих ячеек, предназначенная для хранения текущих значений направляющих косинусов имеет два выхода. Через выход, связанный со средним разрядом запоминающей ячейки, информация на старшей половине ноля ячейки выводится для использования в вычислениях полноразрядных приращений направляющих косинусов. Одновременно через выход, связанный с младшим разрядом ячейки, информация со всего поля ячейки выводится для вычисления нового зн1ачения надравляющего косинуса. На входы выходных сумматоров, предназначенных для вычисления текущих значений направляющих косинусов, одновременно со старыми звачениями этих величин поступают подноразрядные приращения направляющих косинусов, вычисляемые на данном шаге интегрирова-ния.

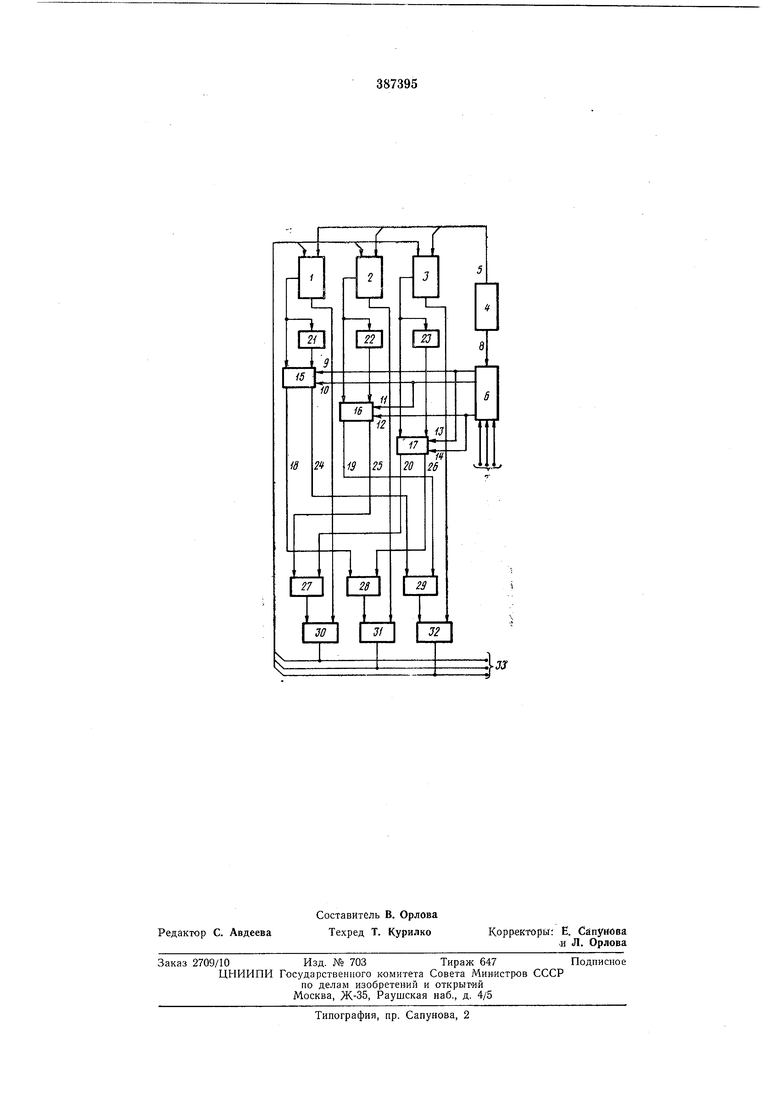

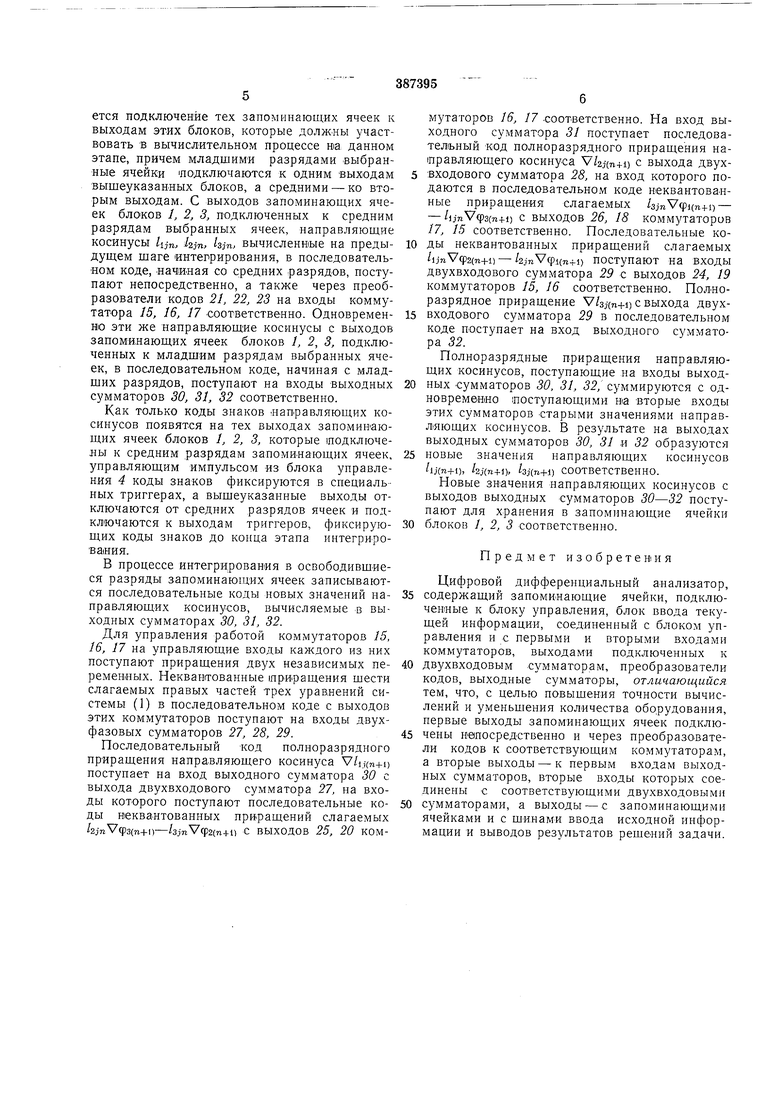

На чертеже приведена блок-схема предлагаемого ЦДА.

В состав каждого из блоков Л 2 н 3 запоминающих ячеек входят три ячейки, предназначенные для приема, хранения и выдачи последовательных кодов трех направляющих косинусов. Направляющие косинусы /ц, /is, /is хранятся в блоке /; /2ь /22, /аз- в блоке 2, а /31, /32, /33 - в блоке 3. Каждый из блоков, кроме трех ячеек, содержит специальпый триггер для фиксации, начиная с середины каждого этапа интегрирования, знаков направляющих косинусов в порядке их участия в вычислительном процессе. В качестве запоминающих ячеек целесообразно использовать линии задержки или регистры. Блок управления 4 служит для управления всеми блоками ЦДА с помощью управляющих сигналов, вырабатываемых в этом же блоке. В начале каждого этапа интегрирования в каждом из заиоминающих ячеек блоков J, -2 и 3 с выхода 5 блока травления 4 поступает сигнал, подключающий к выходам блока ячейку-, хранящую тот направляющий косинус, который необходим для-вычислительного процесса на данном этапе интегрирования. Блок ввода текущей информации 6 предназначен для преобразования информации, поступающей на его входные шины 7 от управляемого объекта обычно в виде непрерывных величин, в наиболее пригодную для использования в ЦДА форму, т. е. в поток приращений.

Перед каждым шагом интегрирования по сигналу, пОСтупающему из блока управления 4 на вход 8 блока ввода текущей информации 6, на входах 9, 10, 11, 12, 13, и 14 коммутаторов 15, 16 и 17 устанавливаются новые значения приращений независимых переменных, которые фиксируются в течение всего шага интегрирования. На входах 12 и 14 фиксируется

приращение независимой переменной Уф1; на входах 9, 13 - Уф2; на входах 10, 11 - Vcps. Каждый из коммутаторов 15-17 состоит из четырех двувходовых схем совпадения и двух собирательных .схем на два входа. Коды направляющих косинусов, начиная со средних разрядов ячеек, с выходов запоминающих ячеек блоков /, 2, 3 проходят соответственно на выходы 18, 19, 20, если текущая информация,

поступающая соответственно на управляющие входы 10, 12 и 13 имеет отрицательный знак. Если же текущая информация имеет положительный знак, то на выходы 18, 19, 20 проходят КОДЫ с выходов преобразователей кодов

21, 22 и 23. Носледовательные коды направляющих косинусов, начиная со средних разря,дов ячеек, проходят выходы 24, 25 w. 26 с выходов запоминающих ячеек соответственно блоков 1, 2 и 3, если текущая информация,

поступающая соответственно на управляющие входы Я 11, 14 положительного знака. Если же текущая информация отрицательного знака, то на выходы 24, 25 и 26 проходят коды с выходов преобразователей кодов 21, 22 и 23.

Нреобразователи кодов 21-23 последовательного действия предназначены для перехода от кодов направляющих косинусов, поступающих на их входы, к дополнительным кодам этих же величин.

Если же на какой-либо вход коммутатора не поступает текущая информация, то Hia соответствующий выход этого коммутатора не проходит код направляющего косинуса. Так, например, если Vcpi «0, то на выходы 19 ч

26 коммутаторов 16 и 17 не проходят коды соответствующих направляющих косинусов.

Для сложения неквантованных приращений слагаемых правых частей уравнения системы (1) предназначены сумматоры 27, 28 и 29, на

входах которых получаются неквантованные (полноразрядные) приращения направляющих косинусов, соответственно V/ij, Vkj, Vkj. Выходы двухвходовых сумматоров 27, 28, 29 соединены со входами выходных сумматоров 30, 31 и 32 соответственно. Выходные сумматоры 30-32, вторые входы которых соединены с выходами соответственно запоминающих ячеек блоков /, 2, 3 предназначены для вычисления текущих значений направляющих

косинусов.

Шины 33 служат для ввода исходной информации в запоминающие ячейки блоков 1, 2, 3 и вывода результатов решения задачи. Шаг интегрирования состоит из трех этаinoB. На каждом этапе одновременно вычисляются текущие значения трех направляющих косинусов.

Работа предлагаемого ЦДА совершенно одинакова на всех трех этапах шага интегрирования.

Рассмотрим работу ЦДА на одном из этапов и-го шага интегрировапия. Управляющим импульсом из блока управления 4, поступающим в начале этапа интегрирования в запоминающие ячейки блоков /, 2, 3, осуществляется подключение тех запоминающих ячеек к выходам этих блоков, которые долж-ны участвовать в вычислительном процессе на данном этапе, причем младшими разрядами выбранные ячейки подключаются к одним выходам вышеуказанных блоков, а средними - ко вторым выходам. С выходов запоминаюш,их ячеек блоков 1, 2, 3, подключенных к средним разрядам выбранных ячеек, направляюшие косинусы kjn, kin, Isjn, вычисленн1ые на предыдуш;ем шаге интегрирования, в последовательном коде, начиная со средних разрядов, поступают непосредственно, а также через преобразователи кодов 21, 22, 23 на входы коммутатора 15, 16, 17 соответственно. Одновременно эти же направляюш,ие косинусы с выходов заноминающих ячеек блоков /, 2, 3, подключенных к младшим разрядам выбранных ячеек, в последовательном коде, начиная с младших разрядов, поступают на входы выходных сумматоров 30, 31, 32 соответственно.

Как только коды знаков направляюш,их косинусов появятся на тех выходах запоминаюших ячеек блоков 1, 2, 3, которые шодключелы к средним разрядам запоминаюших ячеек, управляющим импульсом из блока управления 4 коды знаков фиксируются в специальных триггерах, а вышеуказанные выходы отключаются от средних разрядов ячеек и подключаются к выходам триггеров, фиксирующих коды знаков до конца этапа интегрирования.

В процессе интегрирования в освободившиеся разряды запоминающих ячеек записываются последовательные коды новых значений направляющих косинусов, вычисляел№1е в выходных сумматорах 30, 31, 32.

Для управления работой коммутаторов 15, 16, 17 на управляющие входы каждого из них поступают приращения двух независимых переменных. Неквантованные 1приращения шести слагаемых правых частей трех уравнений системы (1) в последовательном коде с выходов этих коммутаторов поступают на входы двухфазовых сумматоров 27, 28, 29.

Последовательный код полноразрядного прирашения направляющего косинуса V/ij(«+i) поступает на вход выходного сумматора 30 с выхода двухвходового сумматора 27, на входы которого поступают последовательные коды неква-нтованных приращений слагаемых /2j7zV93(n+o-/3jKVcp2(n+u с выходов 25, 20 коммутаторов 6, 17 .соответственно. На вход выходного сумматора 31 поступает последовательный код полноразрядного приращения натравляющего косинуса V/2j(n+i) с выхода двухвходового сумматора 28, на вход которого подаются в последовательном коде неквантованные приращения слагаемых 4jnV9i(n+i) - - AjreV93(7j+i) с выходов 26, 18 коммутаторов 17, 15 соответственно. Последовательные коды неквантованных приращений слагаемых /и-пУф2(и+1) - 4;яУф1(п+1) поступают на входы двухвходового сумматора 29 с выходов 24, 19 коммутаторов 15, 16 соответственно. Полноразрядное приращение V/3,-(7n-i) с выхода двухвходового сумматора 29 в последовательном коде поступает на вход выходного сумматора 32.

Полноразрядные приращения направляющих косинусов, поступающие на входы выходных сумматоров 30, 31, 32, суммируются с одновременно поступающими на вторые входы этих сумматоров старыми значениями направляющих косинусов. В результате на выходах выходных сумматоров 30, 31 и 32 образуются

новые значения направляющих косинусов ij(«-n), 4j(n+i), зяи+1) соответственно.

Новые значения направляющих косинусов с выходов выходных сумматоров 30-32 поступают для хранения в запоминающие ячейки

блоков 1, 2, 3 соответственно.

Предмет изобретения

Цифровой дифференциальный анализатор,

содержащий запоминающие ячейки, подключенные к блоку управления, блок ввода текущей информации, соединенный с блоком управления и с первыми и вторыми входами коммутаторов, выходами подключенных к

двухвходовым сумматорам, преобразователи кодов, выходные сумматоры, отличающийся тем, что, с целью повышения точности вычислений и уменьшения количества оборудования, первые выходы запоминающих ячеек подключены непосредственно и через преобразователи кодов к соответствующим коммутаторам, а вторые выходы - к первым входам выходных сумматоров, вторые входы которых соединены с соответствующими двухвходовыми

сумматорами, а выходы - с запоминающими ячейками и с щннами ввода исходной информации и выводов результатов рещений задачи.

Авторы

Даты

1973-01-01—Публикация