Изобретение касается устройств соединения интеграторов в цифровом дифференциальном анализаторе последовательного типа.

В известных конструкциях цифровых дифференциальных анализаторах ЦДА для подготовки задачи используется метод запоминания величин переполнения с помоцдью регистра динамического типа с числом разрядов, отличным от ч-исла интеграторов ЦДА. Поэтому в этих конструкциях за один период содержимое регистра сдвигается (прецессирует).

Изобретение имеет цель упростить подготовку задачи на ЦДА.

Отличие предложенного устройства от ранее известных состоит в том, что запоминание переполнений в нем осуществляется без «прецессии, подготовка машины к решению выполняется путем соединения интеграторов на наборном поле. В нем применено коммутационное устройство, содержащее регистр для хранения переполнений с числом разрядов, равным количеству разрядов в интеграторах, управляющие цепи и доску с гнездами, предназначенную для набора задачи соединением гнезд, представляющих выходы одних интеграторов, о гнездами, представляющими входы других интеграторов.

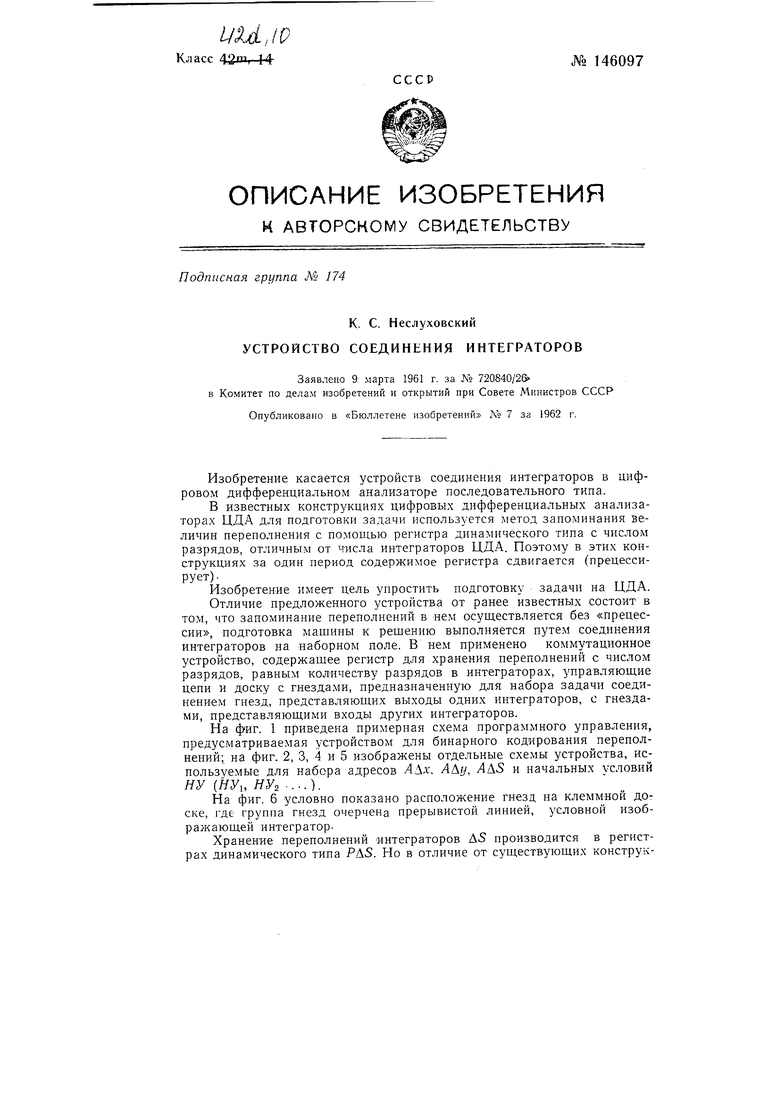

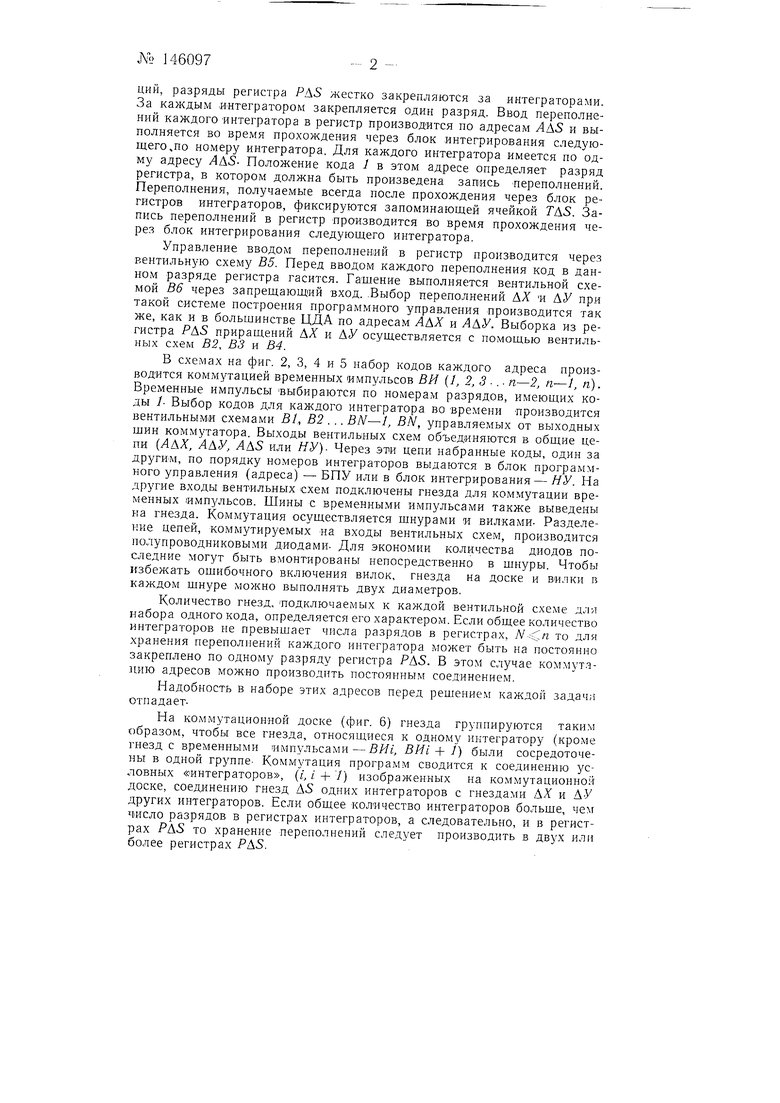

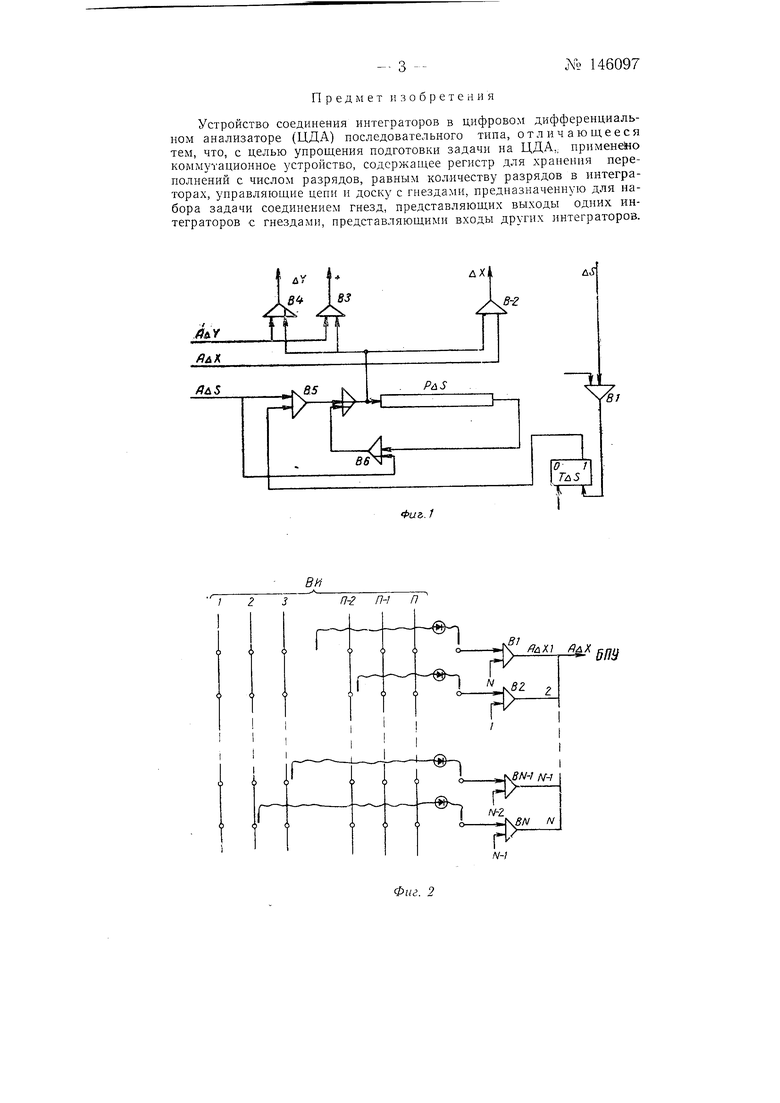

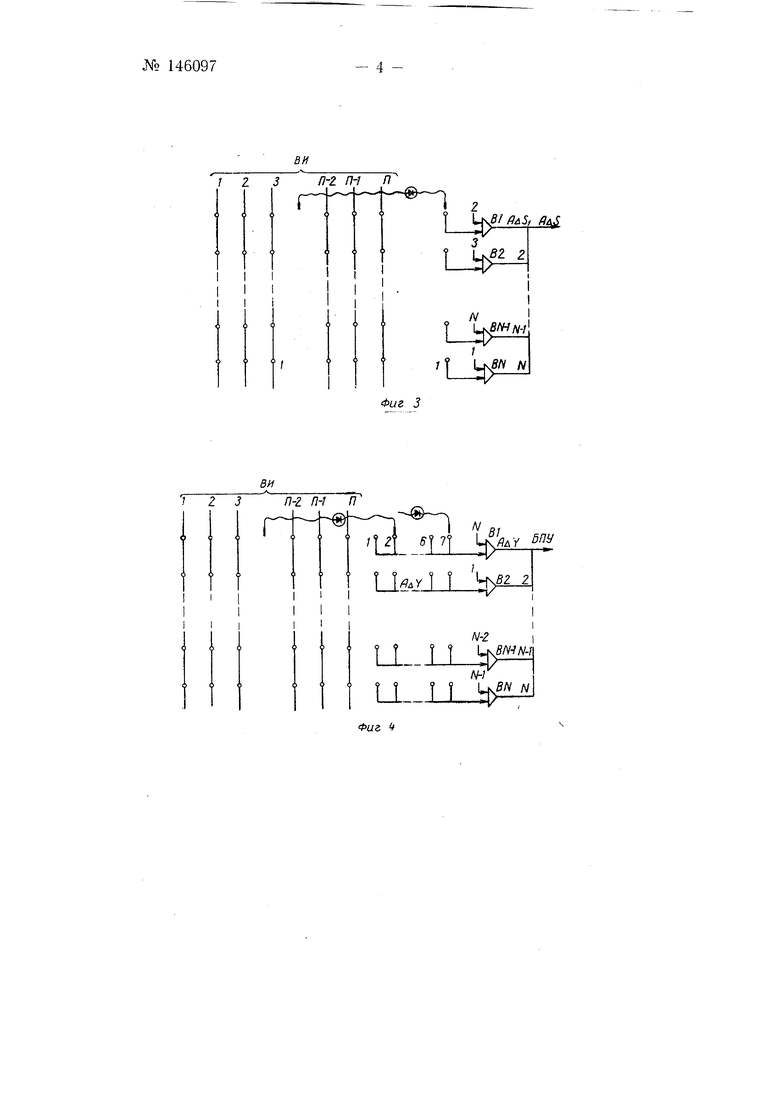

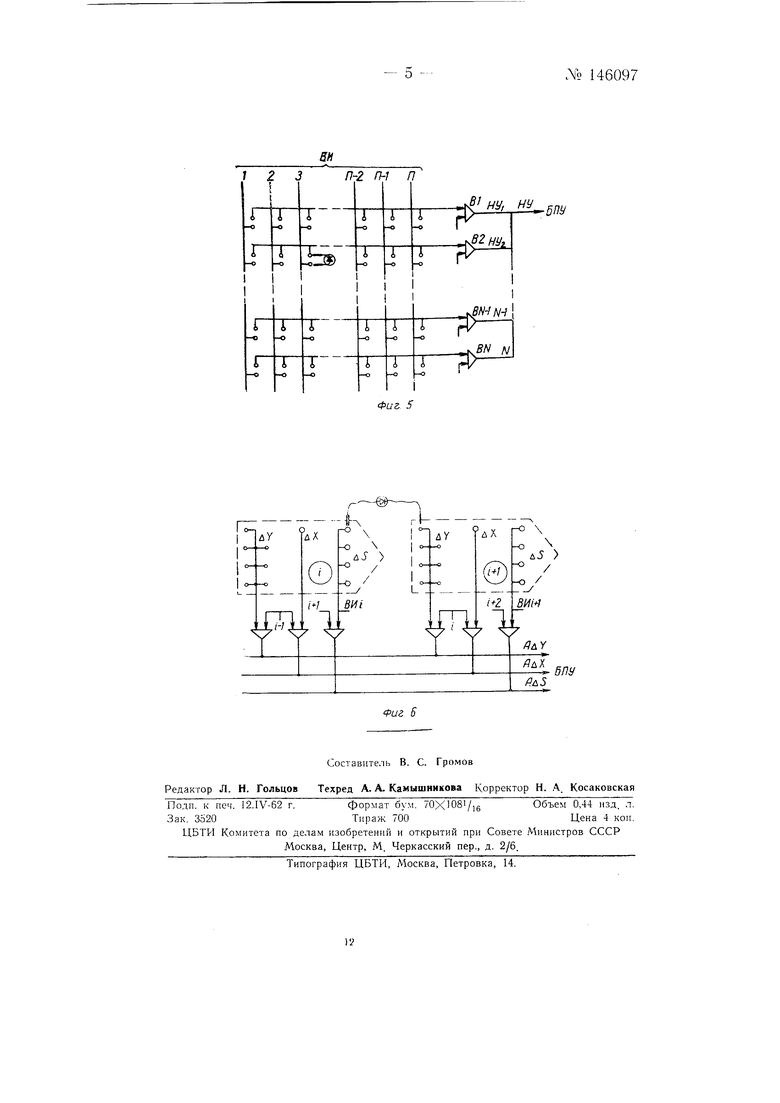

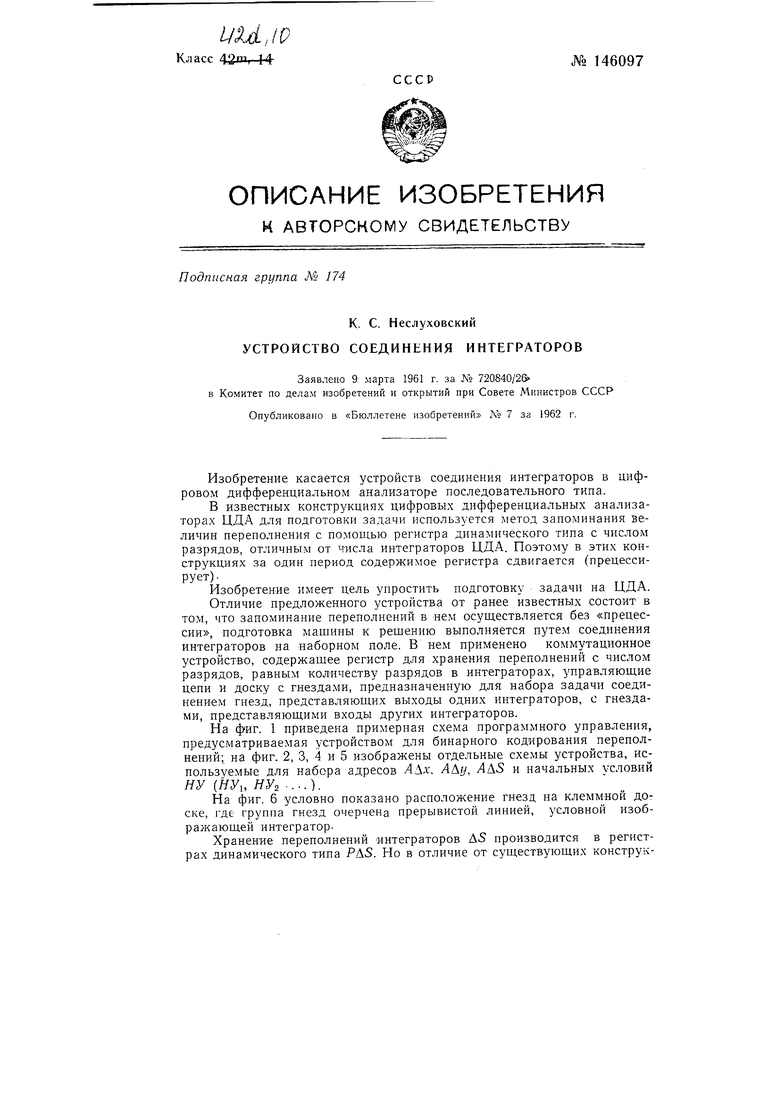

На фиг. 1 приведена примерная схема программного управления, предусматриваемая устройством для бинарного кодирования переполнений; на фиг. 2, 3, 4 и 5 изображены отдельные схемы устройства, используемые для набора адресов . ЛДу, ЛД5 и начальных условий НУ (ЯУь ЯУ2 ....).

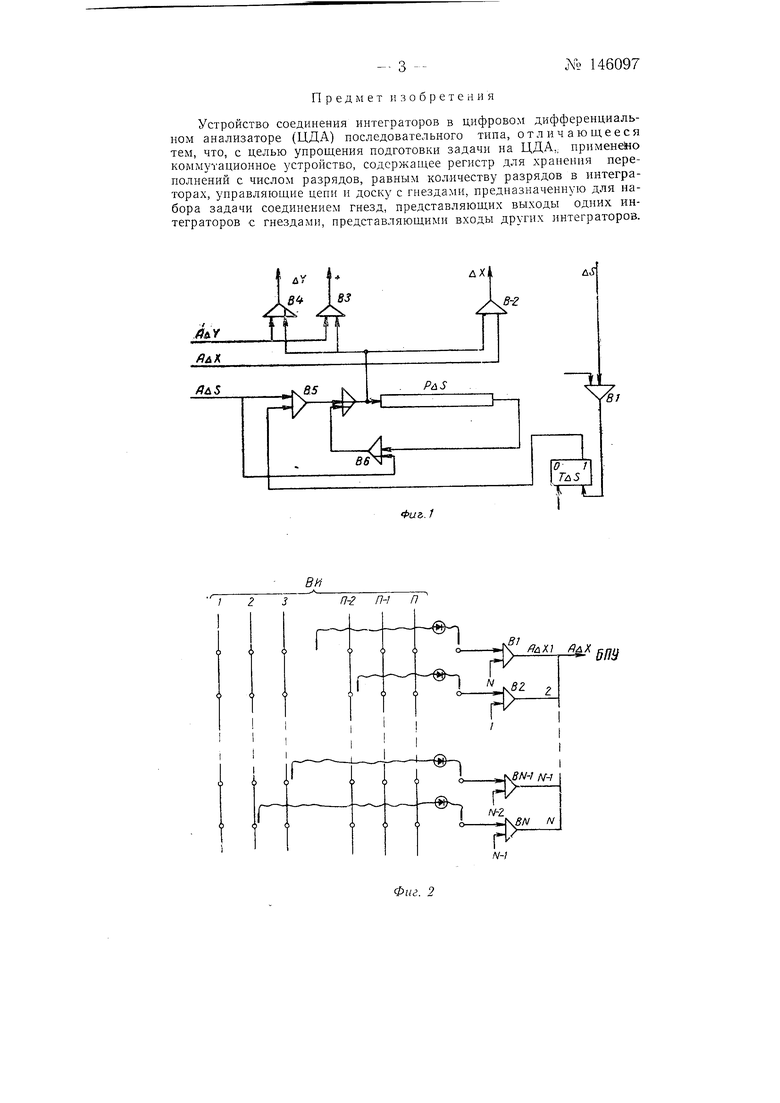

На фиг. 6 условно показано расположение гнезд на клеммной доске, где группа гнезд очерчена прерывистой линией, условной изображающей интеграторХранение переполнений интеграторов AS производится в регистрах динамического типа РД5. Но в отличие от существующих конструкЛ1 146097 - 2 ций, разряды регистра ЯД5 жестко закрепляются за интеграторами. За каждым интегратором закрепляется один разряд. Ввод переполнений каждого интегратора в регистр производится по адресам AAS и выполняется во время прохождения через блок интегрирования следующего,по номеру интегратора. Для каждого интегратора имеется по одму адресу A&S- Положение кода 1 в этом адресе определяет разряд регистра, в котором должна быть произведена запись переполнений. Переполнения, получаемые всегда после прохождения через блок регистров интеграторов, фиксируются запоминающей ячейкой TAS. Запись переполнений в регистр производится во время прохождения через блок интегрирования следующего интегратора.

Управление вводом переполпений в регистр производится через вентильную схему В5. Перед вводом каждого переполнения код в данном разряде регистра гасится. Гашение выполняется вентильной схемой В6 через запрещающий вход. .Выбор переполнений АХ и АУ при такой системе построения программного управления производится так же, как и в больщинстве ЦДЛ по адресам ЛАХ и ААУ. Выборка из регистра РД5 приращений АХ и АУ осуществляется с помощью вентильных схем В2, 83 и В4.

В схемах на фиг. 2, 3, 4 и 5 набор кодов каждого адреса производится коммутацией временных импульсов ВИ (1, 2, 3 .. п-2, п--1, п. Временные импульсы -выбираются по номерам разрядов, имеющих коды / Выбор кодов для каждого интегратора во времени производится вентильными схемами 5/, В2 . ..BN-1, BN, управляемых от выходных щин коммутатора. Выходы вентильных схем объединяются в общие цепи (ЛДЛ, ААУ, А AS или НУ}- Через эти цепи набранные коды, один за други, по порядку номеров интеграторов выдаются в блок программного управления (адреса) - БПУ или в блок интегрирования - НУ. На другие входы вентильных схем подключены гнезда для коммутации временных импульсов. Шины с временными импульсами также выведены на гнезда. KoJMмyтaция осуществляется щнурами и вилками- Разделение цепей, коммутируемых на входы вентильных схем, производится полупроводниковыми диодами. Для экономии количества диодов последние могут быть вмонтированы непосредственно в щнуры. Чтобы избел ать ощибочного включения вилок, гнезда на доске и вилки в каждом шнуре можно выполнять двух диаметров.

Количество гнезд, -подключаемых к каждой вентильной схеме для набора одного кода, определяется его характером. Если общее количество интеграторов не превышает числа разрядов в регистрах, то для хранения переполнений каждого интегратора может быть на постоянно закреплено по одному разряду регистра PAS. В этом случае коммутацию адресов можно производить постоянным соединением.

Надобность в наборе этих адресов перед решением каждой задачи отпадаетНа коммутационной доске (фиг. 6) гнезда группируются таким образом, чтобы все гнезда, относящиеся к одному интегратору (кроме гнезде временными импульсами-ВИ1, ВИ1 + 1} были сосредоточены в одной группе- Коммутация программ сводится к соединению условных «интеграторов, (/, i + 1) изображенных на ко.ммутационной доске, соединению гнезд AS одних интеграторов с гнездами АХ и ДУ других интеграторов. Если общее количество интеграторов больше, чем число разрядов в регистрах интеграторов, а следовательно, и в регистрах PAS то хранение переполнений следует производить в двух или более регистрах PAS.

Предмет изобретения

Устройство соединения интеграторов в цифровом дифференциальном анализаторе (ЦДЛ) последовательного типа, отличающееся тем, что, с целью упрощения подготовки задачи на ЦДЛ,, применено коммутационное устройство, содержащее регистр для хранения переполнений с числом разрядов, равным количеству разрядов в интеграторах, управляющие цепи и доску с гнездами, предназначенпую для набора задачи соединением гнезд, представляющих выходы одних интеграторов с гнездами, представляющими входы других интеграторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1972 |

|

SU415676A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР ПОСЛЕДОВАТЕЛЬНОГО ТИПА | 1970 |

|

SU281025A1 |

| РЕШАЮЩИЙ БЛОК ДЛЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО | 1972 |

|

SU355631A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР | 1973 |

|

SU387395A1 |

| ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU294156A1 |

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Арифметическое устройство цифрового дифференциального анализатора | 1961 |

|

SU148965A1 |

| Устройство для отображения графи-чЕСКОй иНфОРМАции HA эКРАНЕ элЕКТРО-HHO-лучЕВОй ТРубКи | 1979 |

|

SU834739A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

дХ

/

F

ьт

II-т-

i I I i 1

5Л/-/ ЛЛ/

23 л-г п-1 п

г

lit tit I Ь.у I

I I I

i I I I I J i i 1

--.-®fLjlILJ

В

БПУ

I I 4 1

II 11 VL/

1 2 J

П-2 ГИ П

Авторы

Даты

1962-01-01—Публикация

1961-03-09—Подача