Известен запоминающий элемент на тункельном диоде, резисторе и транзисторе, соединенный с чи1сло1вой и разрядной шинами.

Недостатками нзвест1ного за1пО|МИнающегоэлемента является невысокая надежность, определяемая малым отношением тока записи к току тю.мехи,.

Описываемый запо.М1Инающий элемент отличается от извесгнОго тем, -что .в нем к -катоду туинельнаго диода подключен эмиттер транзистора, база которого 1сюе.л#1нена с Числовой шиной, Z коллектор подсоединен к разрядной шине.

Указанное отличие нозвоЛяет товысить надежность запоминаюшего элемента.

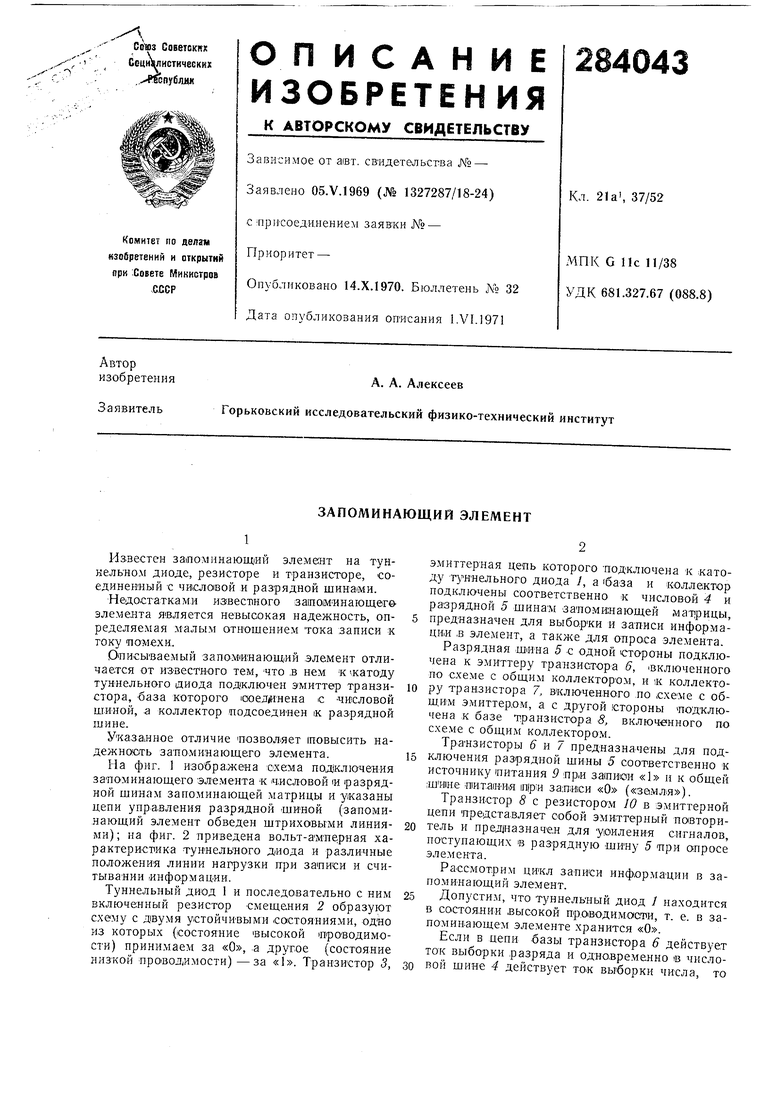

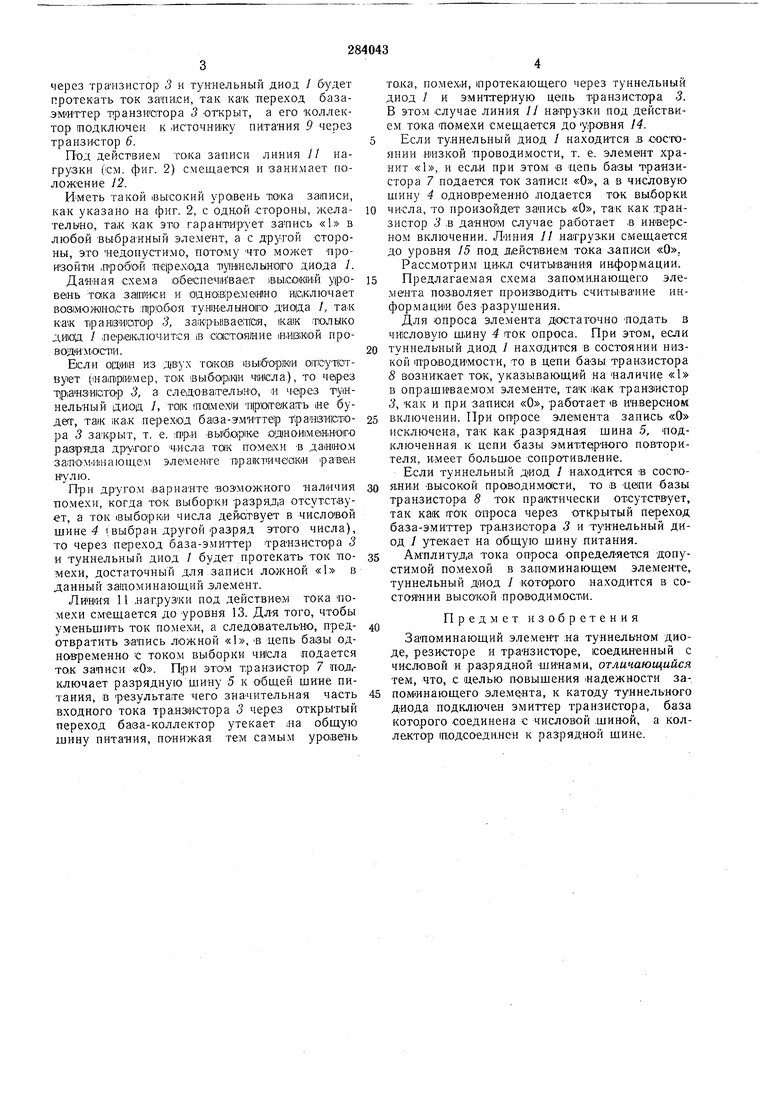

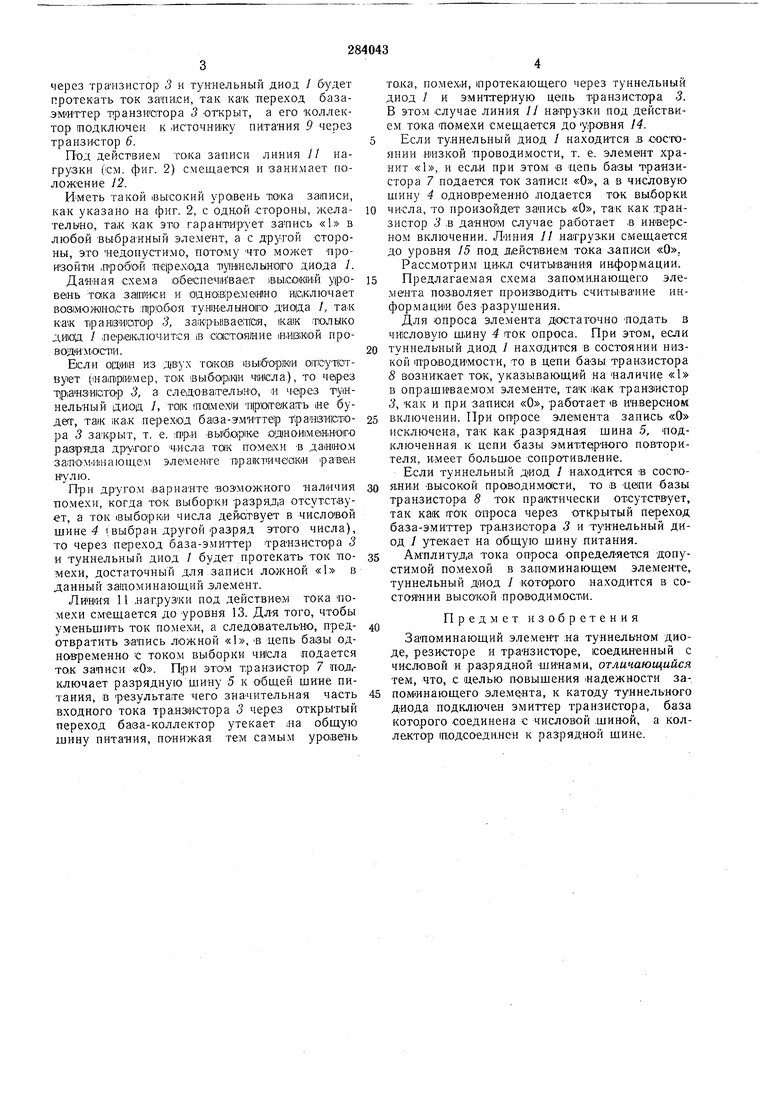

На фиг. 1 изобраЖеНа схема подключения запоминаюш,еГО элемента К чисЛОвой «и разрядной шинам запоминаюш,ей матрицы и указаны цепи управления разрядной шиной (запоминающий элемент обведен штриховыми линиями); на фиг. 2 приведена вольт-аМпе рная характеристика туннельнОГО диода и различные положениЯ линии нагрузки ггри записи и считывании информации.

Туннельный диод 1 и последовательно с ним включенный резистор Смещения 2 образуют схему с Д1вумя устойчивыми состояниями, одно из которых (состояние высокой проводимости) принимаем за «О, .а другое (состояние низкой проводимости) -за «1. Транзистор 5,

эмиттерная цепь которого подключена к :катоду тзннельного диода У, а база и коллектор подключены соответственно о числовой 4 и разрядной 5 шинам запо.мияающей ,

предназначен для выборки и записи информации в элемент, а для опроса элемента.

Разрядная шйна 5 с одной стороны подключена к эмиттеру транзистора 6, включенного по схеме с общим коллектор-ом, и ж коллектору транзистора 7, включенного ,по схе-ме с обш,Им эмиттер.ом, а с другой стороны подключена к базе транзистора 8, включенного цо схеме с общи.м коллектором. Транзисторы (3 и 7 предназначены для подключения разрядной шины 5 соответственно к источнику питания 9 при записи «1 а к общей ;шИ1не шитаиия запаси «О («за.мл1Я).

ТранзИСтор 8 с резисторОм 10 в эмиттерной цепи Представляет собой эмитгерный повторитель и предназначен для усИленИЯ сигналов, поступающих в разрядную ШИну 5 при опросе элемента.

РаССмотрим цикл за-писи информации в запоминающий элемент.

Допустим, что туннельный диод 7 находится в состоянии .высокой пр.оводимости, т. е. в запомивающем элементе хранится «О.

Если в цепи базы транзистора 6 действует ток выборки разряда и одновременно и числочерез транзистор 3 и туннельный диод У будет протекать ток записи, так переход базаэмадттер т;ранзиатора 3 открыт, а его коллектор подключен к .источни1ку питання 9 через транзистор 6.

Под действием тока записи линия // нагрузки (см. фиг. 2) смещается и занимает положение 12.

Иметь такой гвысокий уровень тока записи, как указано на фиг. 2, с одной .стороны, желательно, та.к как это гарантирует запись «1 в любой выбранный элемент, а с другой стороны, это недопустимо, потому что может произойти лрабой перехода Т1у|н|нелыно|го диода /.

Данпая схема юбеспечи васт )ВЫ(СО1К1ий ypioвень така эатйс и и О)дно:кремвн1но и|с,ключает во81мож1но,сть щробоя тушнелыного диода /, как транвиютор 3, за1Кръпвае;т(ая, 1ка1к толыко диюд / .пер1е1ключпт:ся IB с101стая1ние я.ивкюй проВО-ДИМОСТИ.

Бели 01Д1И1Н из д)вух такав 1выбор|К1И отсутютвует (iHampMiMep, TOIK вы6ар1К|и числа), то чарез т ранзиютор 3, а след-оваггелыто, « чарез туннельный диод /, TOIK по|мехи п(рите)ка;ть йе будегг, таж 1ка.к переход б as а-эмиттер транвшсгго ja 3 за-крыт, т. е. вы1бор1ке ояноимеиног-о разрЯда другО1ГО ч-исла так no ieixH в даииом запомИ.нающе м П1рал т1ичес1К1И равей нулю.

При другом .варианте воэможното паличия помехи, когда то-к выборки разря,Л|а отсутствует, а ток (Выборки числа дей.отвует в числовой шине «выбран другой разряд этого числа), то через переход база-эмиттер транзистора 3 и туннельный диод / будет протекать ток по:иехи, достаточный для записи ложной «1 в данный запоминающий элемент.

Лиадия 11 .натрузки под действием тока помехи смещается до уровня 13. Дл-я того, чтобы уменьшить ток помехи, а следователь-но, нредотвратить запись ложной «1, В цепь ба13ы однавремеино с током выборки числа подается так записи «О. При этом транзистор 7 по,д,ключает разрядную шину 5 к общей щине питания, в результате чего значительная часть входного тока траязадстора 3 через открытый переход база-коллектор утекает аа общую шину питания, панижая тем самым уровень

тока, помех.и, протекающего через туннельный диод / и эмиттерную цепь транзистора 3. В этом случае линия И на грузкн под действием тока помехи смещается до уровня 14.

Если туннельный диод / находится в состоянии Н1ИЗКОЙ проводимости, т. е. элемент хранит «1, и есл.и при этом в цепь базы транзистора 7 подается ток записи «О, а в числовую шину 4 одновре.менно подается ток выборки

числа, то произойдет запись «О, так как т;ранзистор 3 в даяном случае работает в инверсном включении. Линия 11 на1груз.ки смещается до уровня 15 под действием то,ка записи «О. Рассмотрим ЦИ.КЛ считывания информации.

Предлагаемая схема запоминающего элемента позволяет производить считывание информации без разрушения.

Для опроса элемента достаточно подать в чи|словую ш.ину 4 ток опроса. При этом, если

туннельный диод / находится в состоянии низкой проводимости, то в цепи базы транзистора 8 возникает ток, указываю|ЩИ й на наличие «I в опрашиваемом элементе, так 1как транзистор 3, как и при записи «О, работает в инверсном

включении. При опросе элемента запись «О исключена, так как разрядная шина 5, подключенная к цепи базы эмитте рного повторителя, имеет большое сопротивление.

Если туннельный диод 1 находится в состоя:нни высокой пр01водимо(сти, ТО В -цвпи базы транзистора 8 ток практически отсутствует, так как ITOK опроса через открытый переход база-эмиттер транзистора 3 и туннельный диод / утекает на общую шину питания.

Амплиту.д,а тока опроса определяется допустимой помехой в запоминающем элементе, туннельный диод 1 котарого находится в состоянии высокой праводим ост.и.

Предмет изобретения

Запоминающий элемент на туннель-ном диоде, резисторе и тр;анзисторе, соединенный с числовой и разрядной шинами, отличающийся тем, что, с целью повышения надежности запом инающето , к катоду туннельного диода подключен эмиттер транзистора, база которого соединена с числовой шиной, а коллектор 1подсоеди,нен к разрядной шине.

-О

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1979 |

|

SU773728A1 |

| Матричный накопитель | 1979 |

|

SU799007A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Запоминающий элемент | 1975 |

|

SU562866A1 |

| СТАБИЛИЗАТОР ТОКА | 1969 |

|

SU240761A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающий элемент | 1977 |

|

SU752477A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU347797A1 |

| Динамический элемент памяти | 1978 |

|

SU763966A1 |

Даты

1970-01-01—Публикация