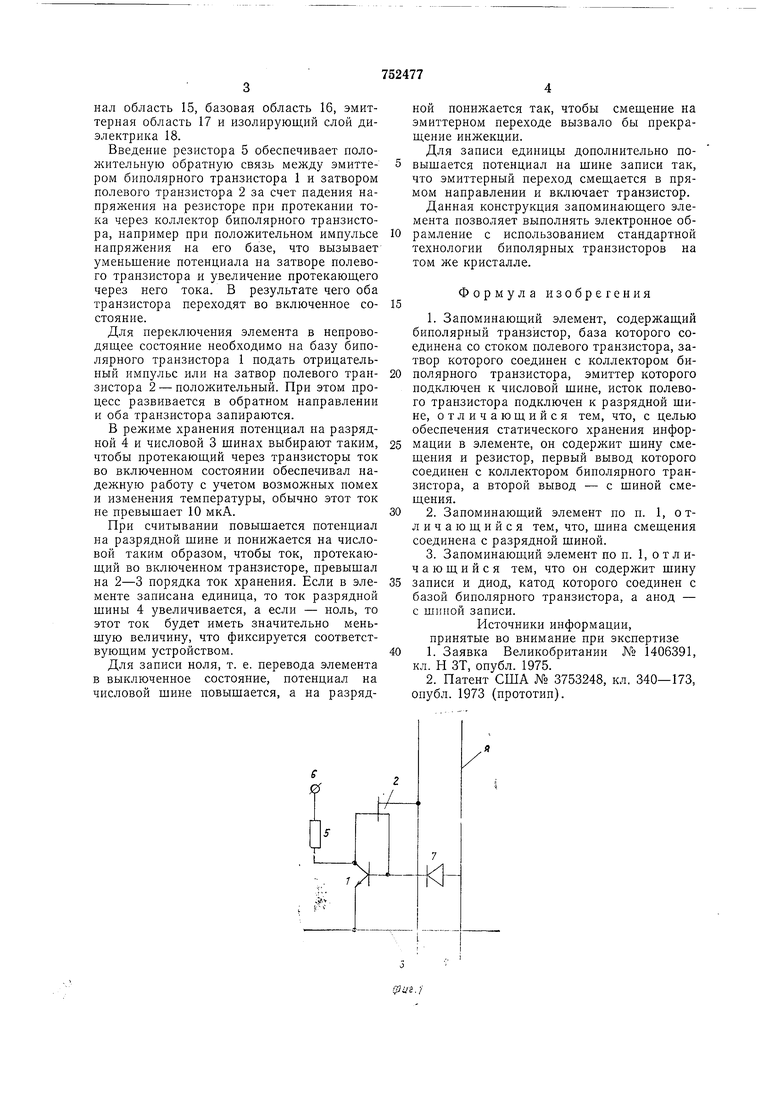

нал область 15, базовая область 16, эмиттерная область 17 и изолирующий слой диэлектрика 18.

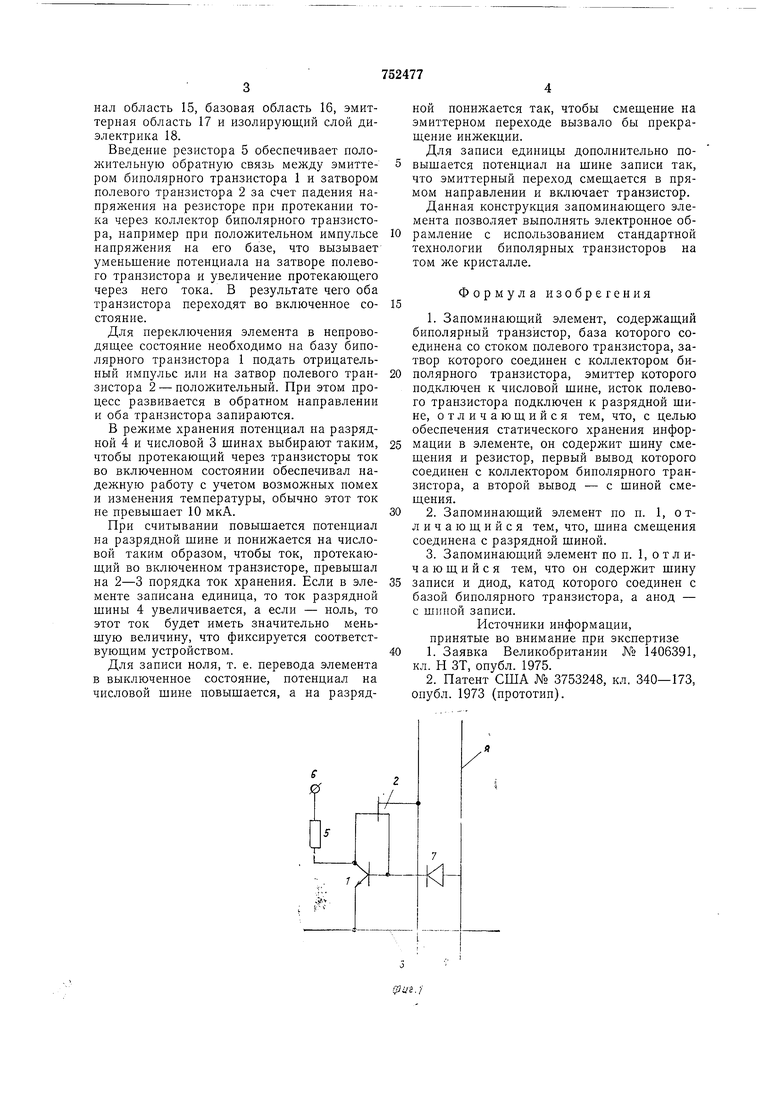

Введение резистора 5 обеспечивает положительную обратную связь между эмиттером биполярного транзистора 1 и затвором полевого транзистора 2 за счет падения напряжения на резисторе при протекании тока через коллектор биполярного транзистора, например при положительном импульсе напряжения на его базе, что вызывает уменьшение потенциала на затворе полевого транзистора и увеличение протекающего через него тока. В результате чего оба транзистора переходят во включенное состояние.

Для переключения элемента в непроводящее состояние необходимо на базу биполярного транзистора 1 подать отрицательный импульс или на затвор полевого транзистора 2 - положительный. При этом процесс развивается в обратном направлении и оба транзистора запираются.

В режиме хранения потенциал на разрядной 4 и числовой 3 щинах выбирают таким, чтобы протекающий через транзисторы ток во включенном состоянии обеспечивал надежную работу с учетом возможных помех и изменения температуры, обычно этот ток не превышает 10 мкА.

При считывании повышается потенциал на разрядной шине и нонижается на числовой таким образом, чтобы ток, протекающий во включенном транзисторе, превышал на 2-3 порядка ток хранения. Если в элементе записана единица, то ток разрядной шины 4 увеличивается, а если - ноль, то этот ток будет иметь значительно меньшую величину, что фиксируется соответствующим устройством.

Для записи ноля, т. е. перевода элемента в выключенное состояние, потенциал на числовой шине повышается, а на разрядной понижается так, чтобы смещение на эмиттерном переходе вызвало бы прекращение инжекции.

Для записи единицы дополнительно повышается потенциал на шине записи так, что эмиттерный переход смещается в прямом направлении и включает транзистор.

Данная конструкция запоминающего элемента позволяет выполнять электронное обрамление с использованием стандартной технологии биполярных транзисторов на том же кристалле.

Формула изобрегения

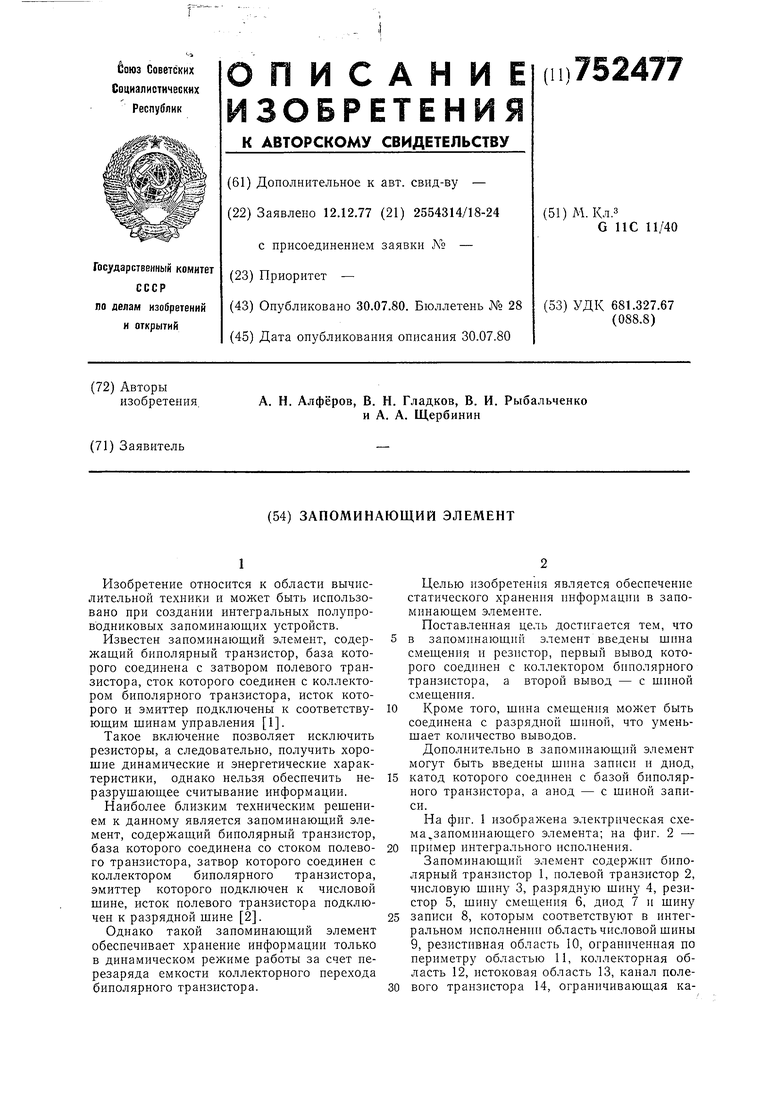

1.Запоминающий элемент, содержащий биполярный транзистор, база которого соединена со стоком полевого транзистора, затвор которого соединен с коллектором биполярного транзистора, эмиттер которого подключен к числовой шине, исток полевого транзистора подключен к разрядной шине, отличающийся тем, что, с целью обеспечения статического хранения информации в элементе, он содержит шину смещения и резистор, первый вывод которого соединен с коллектором биполярного транзистора, а второй вывод - с шиной смещения.

2. Запоминающий элемент по п. 1, отличающийся тем, что, шина смещения соединена с разрядной шиной.

3. Запоминающий элемент по п. 1, о т л ичающийся тем, что он содержит шину

записи и диод, катод которого соединен с базой биполярного транзистора, а анод - с шиной записи.

Источники информации, принятые во внимание при экспертизе

1. Заявка Великобритании N° 1406391, кл. Н ЗТ, опубл. 1975.

2.Патент США № 3753248, кл. 340-173, опубл. 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| Динамический элемент памяти | 1978 |

|

SU763966A1 |

| Матричный накопитель | 1979 |

|

SU773728A1 |

| Долговременный запоминающий элемент | 1978 |

|

SU680054A1 |

| Формирователь импульсов (его варианты) | 1980 |

|

SU974562A1 |

| Ячейка памяти | 1973 |

|

SU444244A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Одновибратор | 1982 |

|

SU1064432A1 |

п - - INI -1

И

77 7f

.

/тл

7J /2 / 5

Авторы

Даты

1980-07-30—Публикация

1977-12-12—Подача