1

Изобретение отноеитея к вычислительной технике.

Известен запоминающий элемент, содержащий два транзистора р-п-р типа, эмиттеры которых соединены с адресной шиной, коллектор первого транзистора р-я-р типа соединен с базой первого, с эмиттером второго транзистора п-р-п тина и с эмиттером третьего транзистора р-п-р типа, коллектор второго транзистора р-п-р типа соединен с базой второго, с эмиттером первого транзистора п-р-п типа и с эмиттером четвертого транзистора р-п-р типа, коллекторы третьего и четвертого транзисторов р-п-р типа соединены с разрядными шинами, базы р-л-р транзисторов и коллекторы п-р-п транзисторов соединены с шиной опорного напряжения 1.

Этот запоминающий элемент имеет низкое быстродействие и малый ток считывания, требующий высокочувствительные усилители считывания. Это объясняется малой величиной коэффициента передачи р-п-р транзисторов, связанных с разрядными шинами.

Наиболее близким техническим решением к данному изобретению является запоминающий элемент, содержаний два транзистора р-п-р типа, эмиттеры которых соединены с адресной И1иной, коллектор первого транзистора р-п-р типа соединен с базами первого

и третьего и с эмиттером четвертого транзисторов п-р-п типа, коллектор второго транзистора р-п-р типа соединен с базами второго и четвертого и с эмиттером третьего

транзистора п-р-п типа, базы транзисторов р-п-р типа соединены соответственно с коллекторами первого, третьего, второго и четвертого транзисторов п-р-п типа, эмиттеры которых соединены с разрядными шинами.

Благодаря тому, что запоминающий элемент связан с разрядными шинами через третий и четвертый транзисторы п-р-п типа, а не через транзисторы р-п-р типа, как у описанного, такой запоминающий элемент имеет более высокое быстродействие и не требует высокочувствительных усилителей считывания

2. I

Однако при записи информации в этот элемент необходимо протекание по разрядным

шинам большого разрядного тока, что ограничивает быстродействие и снижает надежность работы, так как может вызывать сбои в запоминаюших элементах, объединенных общими разрядными шинами. Это объясняется тем,

что запись информации в такой запоминающий элемент происходит за счет протекания базового тока включенного п-р-п транзистора в разрядную щину, при этом туда же течет и коллекторный ток п-р-п транзистора, связанного с разрядной шиной, который в

р раз больше базового тока, где |3 - коэффициент усиления п-р-л транзистора, связанного с разрядной шиной. В результате этого в разрядную шину втекает ток в (Р+1) раз больше тока, необходимого для записи.

Цель изобретения - повышение быстродействия запоминаюш,его элемента при записи информации и надежности его работы за счет снижения величины тока записи в разрядных шинах.

Достигается это тем, что запоминаюищй элемент, содержащий два транзистора р-п-р типа, эмиттеры которых соединены с адресной шиной, коллектор первого транзистора р-п-р типа соединен с базами первого и третьего и с эмиттером четвертого транзисторов п-р-п типа, коллектор второго транзистора р-п-р типа соединен с базами второго и четвертого и с эмиттером третьего транзисторов л-р-п типа, базы транзисторов р-п-р типа соединены соответственно с коллекторами первого, третьего, второго, четвертого транзисторов п-р-л типа, эмиттеры которых соединены с разрядными шинами, содержит два диода, катоды которых соединены с шиной опорного напряжения, а аноды, соответственно, - с базами транзисторов р-л-р типа.

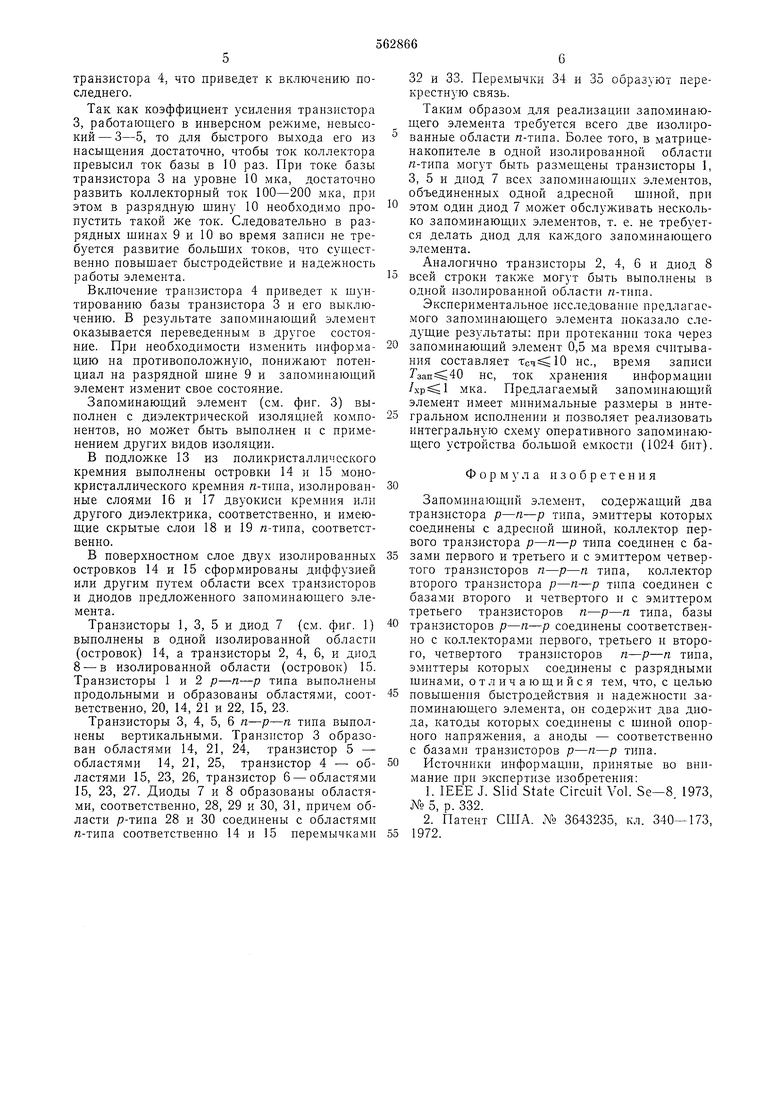

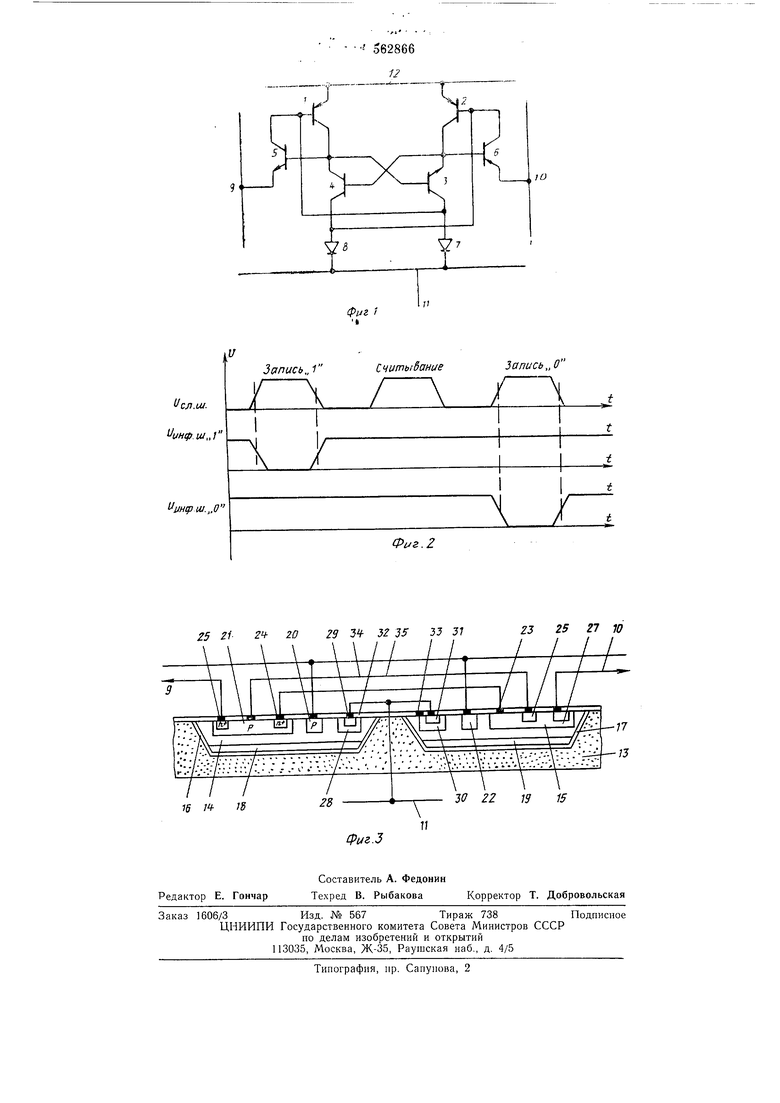

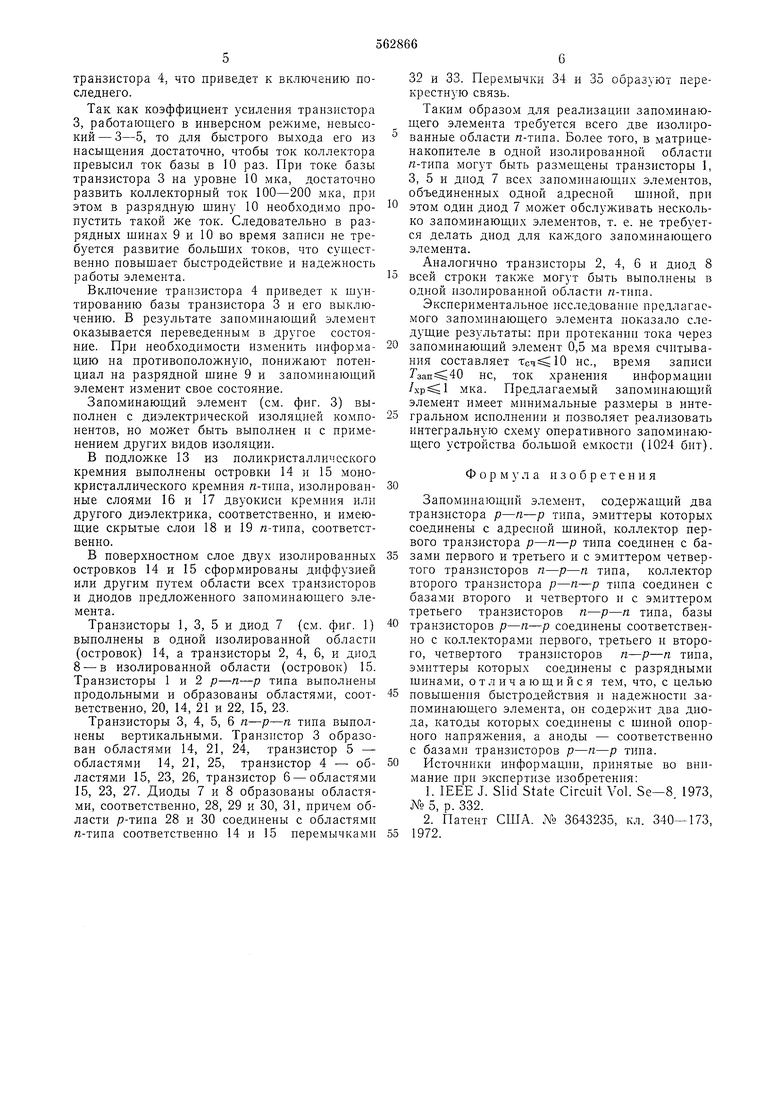

На фиг. 1 изображена принципиальная электрическая схема предлагаемого запоминаюш,его элемепта; па фиг. 2 - временная диаграмма работы запоминающего элемента; на фиг. 3 - сечение одного из вариантов конструктивного выполнения предложенного запоминающего элемента в интегральпом виде.

Предлагаемый запомипающий элемент содержит транзисторы 1 и 2 р-л-р типа, транзисторы 3-6 л-р-л типа и диоды 7 и 8.

Эмиттер транзистора 3 соединен с базой транзистора 4, а эмиттер транзистора 4 - с базой транзистора 3, образуя перекрестную связь. Эмиттеры транзисторов 5 и 6 соединены соответственно с разрядными шинами 9 и 10, п-база транзистора 1 и коллекторы транзисторов 3 и 5 соединены между собой и через диод 7 - с шиной 11 опорного напряжения, п-база транзистора 2, коллекторы транзисторов 4 и 6 соединены между собой и через диод 8 - также с шиной И опорного напряжения. Таким образом, л-базы транзисторов 1 и 2 разделены между собой с помощью встречно включенных диодов 7 и 8.

Питание на запоминающий элемент задается по адресной шине 12, к которой подключены эмиттеры транзисторов 1 и 2.

Предлагаемый запоминающий элемент работает следующим образом. В режиме хранения информации потенциалы на разрядных щинах 9 и 10 поддерживают на уровне

р ш . ш-t/oi

где Ур. ш - потенциал на разрядных шинах; адр.ш - потенциал на адресной шине; и о - падение напряжения на открытом переходе база-эмиттер.

При этом ток из адресной шины 12 протекает через эмиттерные переходы р-п-р транзисторов 1 и 2 и диоды 7 и 8 в шину 11 опорного напряжения.

Коллекторный ток р-п-р транзисторов I и 2 через эмиттерные переходы л-р-л транзисторов 5 и 6 протекать в разрядные шины 9 и 10 не может, так как для этого потенциал разрядных шин должен быть не выше, чем

t-р- ш адр. ш- УКН- - о,

где t/Kii - напряжение коллектор-эмиттер насыщенного р-л-р транзистора.

Коллекторный ток р-л-р транзисторов 1 и 2 является базовым током л-р-п транзисторов 3 и 4, соответственно, работаюпшх в инверсном включении.

Благодаря наличию перекрестных связей между транзисторами 3 и ,4 и при условии идентичности р-л-р транзисторов 1 и 2 базовые и коллекторные токи л-р-л транзисторов 3 и 4 равны между собой и, при условии, что инверсный коэффициент усиления транзисторов 3 и 4 РШШ, транзисторы 3 п 4 образуют бистабильную триггерную ячейку, в которой один из транзисторов будет открыт, например, транзистор 3, а другой - транзистор 4 - закрыт. На базе открытого транзистора 3 поддерживается высокий уровень равный {Уадр.ш-f/KH, а на базе транзистора 4 -

низкий, равный Ьадр. + кп, ГДе UK« -

напряжение коллектор-эмиттер насыщенного л-р-л транзистора 3 в инверсном включении. Таким образом обеспечивается хранение информации.

При считывании информации на разрядных шинах 9 и 10 устанавливают потенциал

-адр. ш-26о- -Ски рш- адр. ш- L/KII - L/oТак как база транзистора 5 соединена с базой транзистора 3, через эмиттерный переход транзистора 5 потечет ток в разрядную щину 9 и на ней установится уровень ш-

- f/KH-t/o.

В результате между разрядными шинами 9 и 10 образуется разность потенциалов, которая и улавливается усилителем считывания.

Для записи информации в предлагаемый запоминающий элемент необходимо на одной из разрядных щин, например, на шине 9 оставить потенциал режима хранения или несколько повысить его, а на щине 10 понизить потенциал

до уровня /рш 1/адр. ш - .

При этом через эмиттерный переход л-р-п транзистора 6 потечет ток в разрядную шину 10 и вызовет включение транзистора 6, коллекторный ток которого является базовым током р-л-р транзистора 2.

Возрастание базового тока транзистора 2 вызовет возрастание его коллекторного тока, который является и коллекторным током транзистора 3, в то время, как базовый ток транзистора 3 остается неизменным на уровне режима хранения. В результате возрастания коллекторного тока транзистор 3 выйдет из насыщения и перестанет шунтировать базу

5

транзистора 4, что приведет к включению последнего.

Так как коэффициент усиления транзистора 3, работающего в инверсном режиме, невысокий - 3-5, то для быстрого выхода его из насыщения достаточно, чтобы ток коллектора превысил ток базы в 10 раз. При токе базы транзистора 3 на уровне 10 мка, достаточно развить коллекторный ток 100-200 мка, при этом в разрядную шину 10 необходимо пропустить такой же ток. Следовательно в разрядных шинах 9 и 10 во время записи не требуется развитие больших токов, что существенно повышает быстродействие и надежность работы элемента.

Включение транзистора 4 приведет к шунтированию базы транзистора 3 и его выключению. В результате запоминающий элемент оказывается переведенным в другое состояние. При необходимости изменить информацию на противоположную, понижают потенциал на разрядной шине 9 и запоминающий элемент изменит свое состояние.

Запоминающий элемент (см. фиг. 3) выполнен с диэлектрической изоляцией компонентов, но может быть выполнен и с применением других видов изоляции.

В подложке 13 из поликристалличсского кремния выполнены островки 14 и 15 монокристаллического кремния «-тина, изолированные слоями 16 и 17 двуокиси кремния или другого диэлектрика, соответственно, и имеющие скрытые слои 18 и 19 /г-типа, соответственно.

В поверхностном слое двух изолированных островков 14 и 15 сформированы диффузией или другим путем области всех транзисторов и диодов предложенного запоминающего элемента.

Транзисторы 1, 3, 5 и диод 7 (см. фиг. 1) выполнены в одной изолированной области (островок) 14, а транзисторы 2, 4, 6, и диод 8 - в изолированной области (островок) 15. Транзисторы 1 и 2 р-п-р типа выполнены продольными и образованы областями, соответственно, 20, 14, 21 и 22, 15, 23.

Транзисторы 3, 4, 5, 6 п-р-п типа выполнены вертикальными. Транзистор 3 образован областями 14, 21, 24, транзистор 5 - областями 14, 21, 25, транзистор 4 - областями 15, 23, 26, транзистор 6 - областями 15, 23, 27. Диоды 7 и 8 образованы областями, соответственно, 28, 29 и 30, 31, причем области /5-тииа 28 и 30 соединены с областями п-типа соответственно 14 и 15 перемычками

6

32 и 33. Пере.мычки 34 и Зо образуют перекрестную связь.

Таким образом для реализации запоминающего элемента требуется всего две изолированные области л-типа. Более того, в матриценакопителе в одной изолированной области л-типа могут быть размещены транзисторы 1, 3, 5 и диод 7 всех запоминающих элементов, объединенных одной адресной шиной, при

этом один диод 7 может обслуживать несколько запоминающих элементов, т. е. не требуется делать диод для каждого запоминающего элемента. Аналогично транзисторы 2, 4, 6 и диод 8

всей строки также могут быть выполнены в одной изолированной области л-типа.

Экспериментальное исследование предлагаемого запоминающего элемента показало следущие результаты: при протекании тока через

запоминающий элемент 0,5 ма время счнтывания составляет не., время записи НС, ток хранения информации мка. Предлагаемый запоминающий элемент имеет минимальные размеры в интегральном исиолнении к позволяет реализовать интегральную схему оперативного запоминающего устройства больщой емкости (1024 бит).

Форм}л а изобретения

Запоминающий элемент, содержащий два транзистора р-п-р типа, эмиттеры которых соединены с адресной шиной, коллектор первого транзистора р-л-р типа соединен с базами первого и третьего и с эмиттером четвертого транзисторов л-р-л типа, коллектор второго транзистора р-л-р типа соединен с базами второго и четвертого и с эмиттером третьего транзисторов л-р-л типа, базы

транзисторов р-л-р соединены соответственно с коллекторами первого, третьего и второго, четвертого транзисторов л-р-л типа, эмиттеры которых соединены с разрядными шинами, отличающийся тем, что, с целью

повышения быстродействия и надежности запоминающего элемента, он содержит два диода, катоды которых соединены с шиной опорного напряжения, а аноды - соответственно с базами транзисторов р-л-р тииа.

Источники информации, принятые во внимание при экспертизе изобретения:

1.ШЕЕ J. Slid State Circuit Vol. Se-8 1973, jYo 5, p. 332.

2.Патент США. N 3643235, кл. 340-173, 1972.

Фиг i

| название | год | авторы | номер документа |

|---|---|---|---|

| Инжекционный запоминающий элемент | 1974 |

|

SU526951A1 |

| Элемент памяти | 1975 |

|

SU525160A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Запоминающий элемент | 1977 |

|

SU733022A1 |

| Запоминающий элемент | 1975 |

|

SU570921A1 |

| Запоминающее устройство | 1974 |

|

SU658600A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Запоминающее устройство с произвольной выборкой | 1977 |

|

SU769626A1 |

| Запоминающее устройство | 1977 |

|

SU769627A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

Авторы

Даты

1977-06-25—Публикация

1975-07-01—Подача