Известны устройства для управления стековой памятью, содержащие счетчик адреса стековой памяти, регистр адреса оперативной памяти и счетчик операндов.

Предлагаемое устройство отличается тем, что оно содержит регистр команд программы вычислений и стек адресов оперативной памяти, выходы которого подключены ко входам регистра адреса оперативной памяти, а входы подсоединены к выходам разрядов регистра команд, соответствующих очередному слогу программы. Это позволяет сократить время выполнения операций.

На фиг. 1 дана блок-схема нредлагаемого устройства.

Схема содержит регистры 1 и 2; оперативную память (ОП) 3; регистр 4 адреса оперативной памяти (РА); магазинную память (стек) 5; счетчик 6 адресов стека (САС); счетчик 7 операндов (СО); регистр 5 команд программы вычисления (-i); стек 9 адресов (Lz).

Аргументы Л и В операции располагаются в регистрах 1 и 2, а результат операции направляется в регистр 2. Роль запоминающих устройств выполняют оперативная память (ОП) 3 и магазинная память 5. Кроме регистра 8 команд, схема содержит дополнительный регистр 9 - стек адресов, разделенный на слоги как и регистр 8. Перед каждым слогом C в этом регистре размещается число - указатель промежуточных результатов (УПР), величина которого не превосходит увеличенной на единицу емкости основного стека (при емкости стека, не превосходящей семи ячеек, для храпения УПР достаточно трех разрядов). Количество слогов, помещаемых в регистре 9, накладывает ограничеиия на используемые формулы, подобные ограничениям, накладываемым конечной емкостью основного стека.

Практически достаточно иметь емкость регистра 9 равную 5 -J- 6 слогам.

Регистр 9 обладает способностью сдвига находящейся в нем информации в обе стороны на величину слога вместе с предшествующим ему УПР. Младшие разряды регистра, отведенные для хранения УПРО, образуют реверсивный счетчик, аналогичный счетчику адресов основного стека.

Кроме того, в схему входит счетчик 7 операндов СО, емкость которого не превосходит увелнчеиного на единицу количества регистров арифметического устройства АУ, в которые необходи.мо раснределять подготавливаемые операнды.

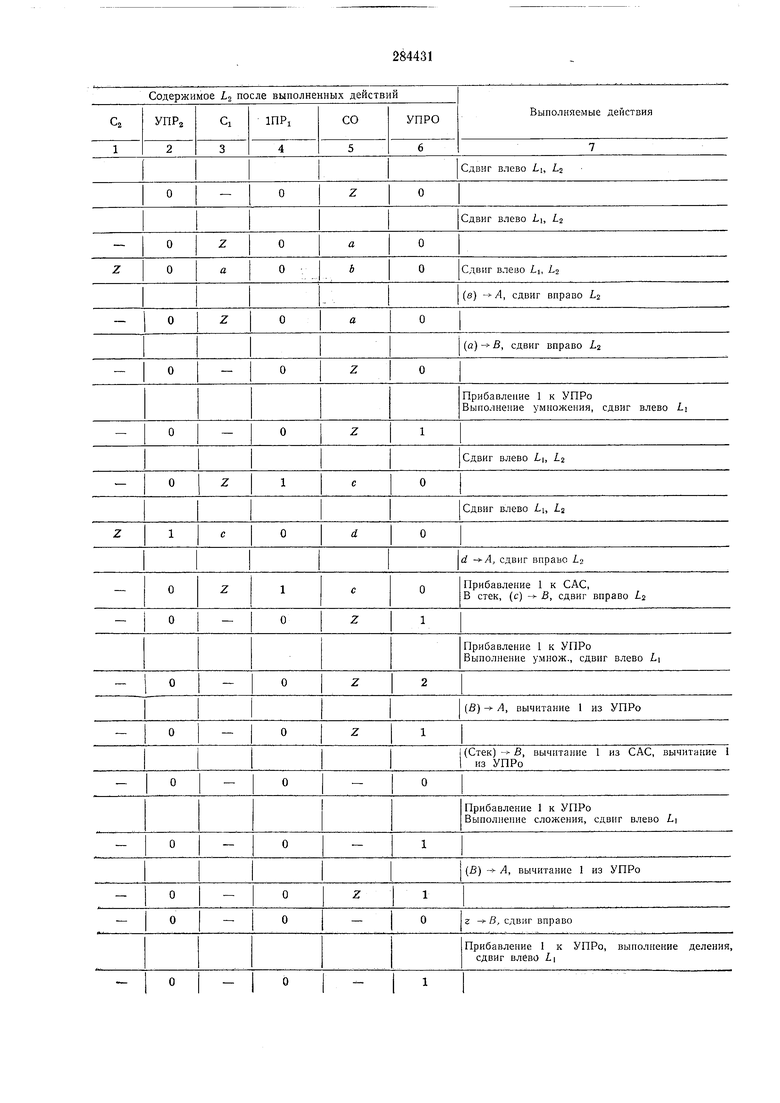

Логика процесса подготовки аргументов операций с помощью описанной схемы приведена на фиг. 2. Здесь: ды. Запись нуля в УПРО - указатель промежуточных результатов; 11- проверка того, является ли старший слог а, кодом операции; 12- запись в СО числа, равного количеству аргументов, участвующих в операции;13- проверка равенства нулю содержимо14- прибавление единицы к УПРО; 15- выполнение операции в АУ; 16- сдвиг L влево на од,ин слог; 17-проверка равенства нулю УПРО; 18- проверка наличия информации в регистре 2; 19- проверка равенства единице содержимого СО; 20- прибавление единицы к содержимому САС, запись информации из регистра 2 в основной стек; 21- передача СО в РА, выборка информации из ОП в RI, сдвиг L.2 вправо на один слог, где RI-регистр / или 2; 22- передача информации из регистра 2 23- передача информации из основного стека B., вычитание единицы из содержимого САС; 24- вычитание единицы из УПРО; 25- вычитание единицы из содерл имого СО. Из указанной логики непосредственно следует, что слог - адрес стека адресов управляет выборкой операнда из памяти лишь в том случае, когда значение относящегося к нему указателя промежуточных результатов равно нулю, а на выходе регистра команд находится слог - код операции, и аргумент, адресуемый расшифровываемым слогам, всегда направляется в один из регистров арифметического устройства, после чего соответствующий слогоадрес выдвигается из стека адресов. Содержимое (г) счетчика операндов СО определяет номер регистра АУ, в который направляется 1-й аргумент операции, причем и R B. Перед началом подготовки в счетчик 7 помещается количество участвующих в ней аргументов (в рассматриваемом случае двуместных операций это количество всегда равно двум, так что первый распределяемый аргумент направляется в регистр 1). После распределения очередного аргумента значение счетчика 7 уменьшается на единицу. Распределение прекращается, когда значение счетчика 7 становится равным нулю. В таблице показано последовательное изменение информации в регистре при расшифровке формулы. ab + cd Логика функционирования устройства без изменений распространяется на случай подготовки аргументов для многоместных операций арифметического устройства. Количество регистров в арифметическом устройстве при этом соответственно увеличивается. Кроме исключения излишних пересылок информации н достигаемой таким образом экономии времени при подготовке аргументов использование описанного устройства приводит к фактическому увеличению емкости стека,

предмет изобретения

Устройство для управления стековой памятью, содержащее счетчик адреса стековой памяти, регистр адреса оперативной памяти и счетчик операндов, отличающееся тем, что, с целью сокращения времени выполнения операций, оно содержит регистр команд программы вычислений и стек адресов оперативной памяти, выходы которого подключены ко входам регистра адреса оперативной памяти, а входы подсоединены к выходам разрядов регистра команд, соответствующих очередному слогу программы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Процессор | 1981 |

|

SU962964A1 |

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| ПАШИНО-ТЕХНН'-'Р'^Н.АЯБИБЛИОТЕКА | 1971 |

|

SU301703A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Процессор микропрограммируемой ЭВМ | 1979 |

|

SU860077A1 |

Даты

1970-01-01—Публикация