Настоящее изобретение относится к вычислительной технике и, в частности, к построению арифметических устройств.

Известны устройства для запоминания, последовательного выполнения онераций сложения, вычитания и счета импульсов с десятичным представлением чисел, содержащее триггеры и логические схемы «И и «ИЛИ.

Эти устройства довольно сложны.

Предлагаемое устройство отличается от известных тем, что схемы «И на входе триггеров разрядов с одинаковым весом соединены через схему «ИЛИ с глиной ввода этих разрядов, второй вход первой схемы «И связан с щиной сигнала выполнения операции, а вторые входы остальных схем «И - с единичным выходом -предшествующего триггера, причем единичный выход каждого триггера разрядов с одинаковы.м весом подключен к соответствующему входу пятивходовой схемы «И, пятый вход которой соединен через схему «ИЛИ с щиной ввода разрядов, а выход пятивходовой схемы «И соединен с нулевыми входами триггеров с одинаковы.м весом и с ипшой переноса в следующую декаду; второй вход схемы «ИЛИ подключен через дифференцирующую Цепочку к выходу триггера разрядов с весом «1, счетный вход которого соедиисн с шиной ввода переноса из .младшей декады и разряда с весом «1.

Это позволяет упростить устройство.

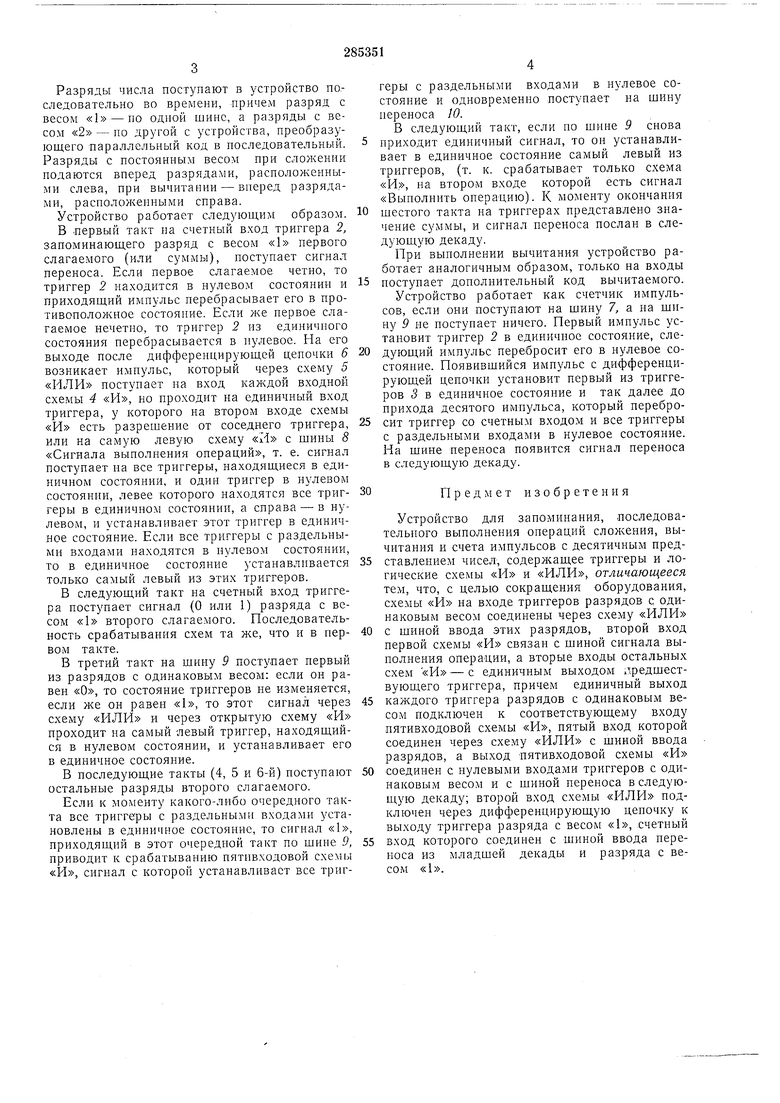

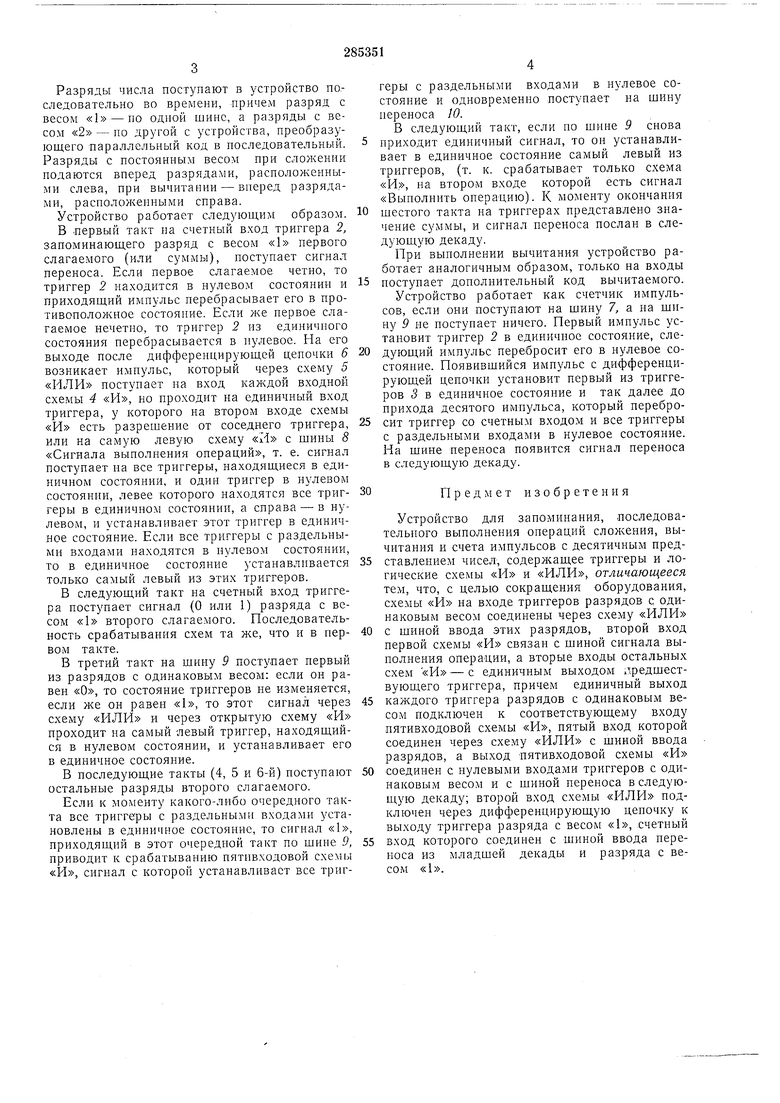

Схема устройства показана на чертеже, где / - пятивходовая логическая схема 2- триггер разряда с весом 3 - триггеры разрядов с весом 4 - двухвходовые логические схемы 5 - логическая схема «11ЛИ ; 6 - дифференцирующая цепочка; 7- шина ввода переноса и разряда с весом 8 - шина сигнала о выполнении оиерации; 9- шина ввода разрядов с весом W - шииа переноса в следующую декаду. Для выполнепия онераций применяется прямой код десятичных чисел и дополнительный (до 9) код, который используется при вычитании (см. таблицу).

Разряды числа поступают в устройство последовательно во времени, причем разряд с весом «1 - по одпой шине, а разряды с весом «2 - по другой с устройства, преобразующего параллельный код в последовательный. Разряды с постоянным весом при сложении подаются вперед разрядами, расположенными слева, при вычитании - вперед разрядами, расположенными справа.

Устройство работает следующим образом.

В .первый такт на счетный вход триггера 2, запоминающего разряд с весом «1 первого слагаемого (или суммы), поступает сигнал переноса. Если первое слагаемое четно, то триггер 2 находится в пулевом состоянии и приходящий импульс перебрасывает его в противоположное состояние. Если же первое слагаемое нечетно, то триггер 2 из единичного состояния перебрасывается в нулевое. На его выходе после дифференцирующей цепочки 6 возникает импульс, который через схему 5 «ИЛИ поступает на вход каждой входной схемы 4 «И, но проходит на единичный вход триггера, у которого на втором входе схемы «И есть разрешение от соседнего триггера, или на самую левую схему «И с щины 8 «Сигнала выполнения операций, т. е. сигнал поступает па все триггеры, находящиеся в единичном состоянии, и один триггер в нулевом состоянии, левее которого находятся все триггеры в единичном состояиии, а справа - в нулевом, и устанавливает этот триггер в единичное состояние. Если все триггеры с раздельными входами находятся в нулевом состоянии, то в единичное со,стояние устанавливается только самый левый из этих триггеров.

В следующий такт на счетный вход триггера поступает сигнал (О или 1) разряда с весом «1 второго слагаемого. Последовательность срабатывания схем та же, что и в первом такте.

В третий такт на шину 9 поступает первый из разрядов с одинаковым весом: если он равен «О, то состояние триггеров не изменяется, если же он равен «1, то этот сигнал через схему «ИЛИ и через открытую схему «И проходит на самый -левый триггер, находящийся в нулевом состоянии, и устанавливает его в единичное состояние.

В последующие такты (4, 5 и 6-й) поступают остальные разряды второго слагаемого.

Если к моменту какого-либо очередного такта все триггеры с раздельными входами установлены в единичное состояние, то сигнал «1, приходящий в этот очередной такт по шине 9, приводит к срабатыванию пятивходовой схемы «И, сигнал с которой устанавливает все триггеры с раздельными входами в нулевое состояние и одновременно поступает на шину переноса 10.

В следующий такт, если по шине 9 снова приходит единичный сигнал, то он устанавливает в единичное состояние самый левый из триггеров, (т. к. срабатывает только схема «И, на втором входе которой есть сигнал «Выполнить операцию). К моменту окончания шестого такта на триггерах представлено значение суммы, и сигнал переноса послан в следующую декаду.

При выполнении вычитания устройство работает аналогичным образом, только на входы поступает дополнительный код вычитаемого.

Устройство работает как счетчик импульсов, если они поступают на шииу 7, а на шину 9 не поступает ничего. Первый импульс установит триггер 2 в единичное состояние, следующий импульс перебросит его в нулевое состояние. Появившийся импульс с дифференцирующей цепочки установит первый из триггеров 3 в единичное состояние и так далее до прихода десятого импульса, который перебросит триггер со счетным входом и все триггеры с раздельными входами в нулевое состояние. На шине переноса появится сигнал переноса в следующую декаду.

Предмет изобретения

Устройство для запоминания, последовательного выполнения операций сложения, вычитания и счета импульсов с десятичным представлением чисел, содерл ащее триггеры и логические схемы «И и «ИЛИ, отличающееся тем, что, с целью сокращения оборудования, схемы «И на входе триггеров разрядов с одинаковым весом соединены через схему «ИЛИ с шиной ввода этих разрядов, второй вход нервой схемы «И связан с шиной сигнала выполнения онерации, а вторые входы остальных схем «И - с единичным выходом предшествующего триггера, причем единичный выход триггера разрядов с одинаковым весом подключен к соответствующему входу пятивходовой схемы «И, пятый вход которой соединен через схему «ИЛИ с шиной ввода разрядов, а выход пятивходовой схемы «И соединен с нулевыми входами триггеров с одинаковым весом и с шиной переноса в следующую декаду; второй вход схемы «ИЛИ подключен через дифференцирующую цепочку к выходу триггера разряда с весом «1, счетный вход которого соединен с шиной ввода переноса из младшей декады и разряда с весом «1.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| УСТРОЙСТВО для ИНТЕГРИРОВАНИЯ ФУНКЦИЙ в ДВОИЧНО-ДЕСЯТИЧНОМ ЦИКЛИЧЕСКОМ КОДЕ | 1967 |

|

SU203321A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| РЕВЕРСИВНАЯ ПЕРЕСЧЕТНАЯ ДЕКАДА | 1969 |

|

SU238249A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1972 |

|

SU351214A1 |

| МАСШТАБИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU360661A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| Арифметическое устройство параллельного действия | 1977 |

|

SU643870A1 |

Даты

1970-01-01—Публикация