1

Изобретение относится к автоматике и вычислительной технике и предназначено для последовательного преобразования кодов правильных дробей.

Известно устройство, выполняюпаее преобразование правильной двоично-десятичной дроби в двоичную дробь, содержащее сдвиговый регистр из статических триггеров, разделенный на тетрады, схему анализа и сдв,ига и схему коррекции.

В предлагаемом устройстве, с целью упрощения и повышения его быстродействия, промежуточные выходы линии задержки соединены со входами схемы коррекции, входы элемента «И соединены с промежуточными выходами распределителя импульсов и линии задержки, а выход элемента «И соединен со входом регистра двоичного числа.

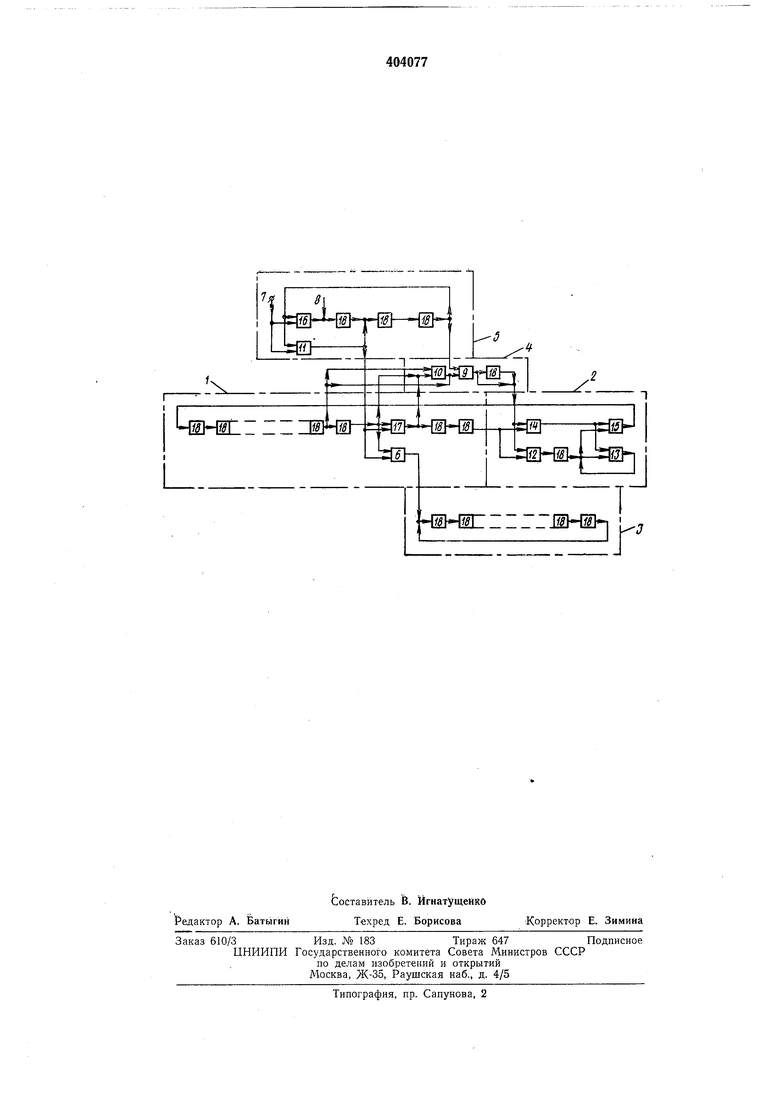

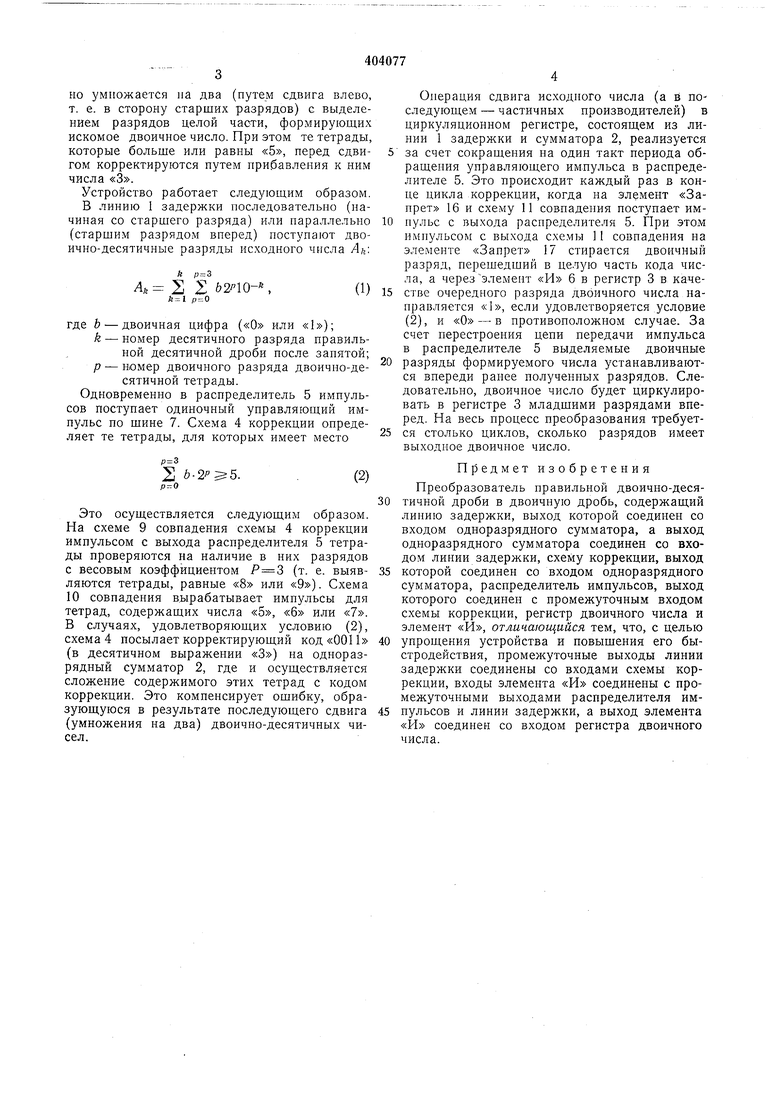

На чертеже нредставлена схема предлагаемого устройства.

Устройство содержит: линию 1 задержки; одноразрядный сумматор 2; регистр 3 двоичного числа; схему 4 коррекции; распределитель 5 импульсов; элемент «И 6; шину 7 управляющих импульсов; вход сигнала «Пуск 8. Для реализации функциональных узлов устройства использованы схемы 9-13 совпадения; элементы «Неравнозначности 14 и 15; элементы «Запрет 16 и 17; накопительные элементы (например, триггеры) 18.

Линия 1 задержки с последовательно соединенным с ней одноразрядным сумматором 2 образует циркуляционный регистр, предназначенный для хранения исходного двоично-десятичного числа, а также промежуточных результатов сдвига. Регистр 3 двоичного числа также нредставляет собой циркуляционный регистр из накопительных элементов, куда -последовательно поступают преобразоваппые двоичные разряды. Оба циркуляционных регистра должны иметь периоды обращепия, кратные четырем. Для сохранения той же точности двоичной дроби, регистр двоичного числа может содержать 1/4 Ig2 числа

элементов регистра двоично-десятичного числа, но в этом случае период обращения регистра двоичного числа должен быть кратен перноду обрапл,ения регистра двоично-десятичного числа. Иными словами, оба регистра, например, могут быть равны между собой, или регистр 3 может быть вдвое короче циркуляционного регистра, состоящего из линии 1 задержки и одноразрядного сумматора 2. Структуру циркуляционного регистра имеет и

распределитель 5 импульсов, период обращения которого равен четырем тактам, а в момент перестроения - трем тактам.

В устройстве используется метод сдвига и коррекции, заключающийся в том, что исходное двоично-десятичное число последовательно умножается на два (путем сдвига влево, т. е. в сторону старших разрядов) с выделением разрядов целой части, формирующих искомое двоичное число. При этом те тетрады, которые больше или равны «5, перед сдвигом корректируются путем прибавления к ним числа «3. Устройство работает следующим образом. В линию 1 задержки последовательно (начиная со старшего разряда) или параллельно (старшим разрядом вперед) поступают двоично-десятичные разряды исходного чнсла /U: л, 2 2 Ь2г1о-, где b - двоичная цифра («О или «1); k- номер десятичного разряда правильной десятичной дроби после запятой; р - номер двоичного разряда двоично-десятичной тетрады. Одновременно в распределитель 5 импульсов поступает одиночный управляющий импульс по шине 7. Схема 4 коррекции определяет те тетрады, для которых имеет место 2 6-2 5. Это осуш.ествляется следующим образом. На схеме 9 совпадения схемы 4 коррекции импульсом с выхода распределителя 5 тетрады проверяются на наличие в них разрядов с весовым коэффициентом (т. е. выявляются тетрады, равные «8 или «9). Схема 10 совпадения вырабатывает импульсы для тетрад, содержащих числа «5, «6 или «7. В случаях, удовлетворяющих условию (2), схема 4 посылает корректирующий код «0011 (в десятичном выражении «3) на одноразрядный сумматор 2, где и осуществляется сложение содержимого этих тетрад с кодом коррекции. Это компенсирует ошибку, образующуюся в результате последующего сдвига (умножения на два) двоично-десятичных чисел. Операция сдвига исходного числа (а в последующем - частичных производителей) в циркуляционном регистре, состоящем из линии 1 задержки и сумматора 2, реализуется за счет сокращения иа один такт периода обращения управляющего импульса в распределителе 5. Это происходит каждый раз в конце цикла коррекции, когда на элемент «Запрет 16 и схему 11 совпадения поступает импульс с выхода распределителя 5. При этом импульсом с выхода схемы 11 совпадения на элементе «Запрет 17 стирается двоичный разряд, перешедший в целую часть кода числа, а через элемент «И 6 в регистр 3 в качестве очередного разряда двоичного числа направляется «1, если удовлетворяется условие (2), и «О - в противоположном случае. За счет перестроения цепи передачи импульса в распределителе 5 выделяемые двоичные разряды формируемого числа устанавливаются впереди ранее полученных разрядов. Следовательно, двоичное число будет циркулировать в регистре 3 младшими разрядами вперед. На весь процесс преобразования требуется столько циклов, сколько разрядов имеет выходное двоичное число. Предмет изобретения Преобразователь правильной двоичио-десятичной дроби в двоичную дробь, содержащий линию задержки, выход которой соединен со входом одноразрядного сумматора, а выход одноразрядного сумматора соединен со входом линии задержки, схему коррекции, выход которой соединен со входом одноразрядного сумматора, распределитель импульсов, выход которого соединен с промежуточным входом схемы коррекции, регистр двоичного числа и элемент «И, отличающийся тем, что, с целью упрощения устройства и повыщения его быстродействия, промежуточные выходы линии задержки соединены со входами схемы коррекции, входы элемента «И соединены с промежуточными выходами распределителя импульсов и линии задержки, а выход элемента «И соединен со входом регистра двоичного числа.

Даты

1973-01-01—Публикация