Изобретение относится к области автоматики и вычислительной техники и предназначено для последовательного преобразования кодов правильных дробей.

Известно устройство для преобразования правильной двоично-десятичной дроби в двоичную дробь, содержащее реверсивный сдвиговый регистр, разделенный на тетрады, схему анализа и сдвига и схему коррекции.

Предлагаемое устройство отличается от известных тем, что выходы распределителя двоичных разрядов по весам соединены с регистром числа, выходы которого соединены со входами запоминающего устройства двоичных эквивалентов, выход которого соединен со входом одноразрядного двоичного сумматора. Это позволяет упростить схему устройства.

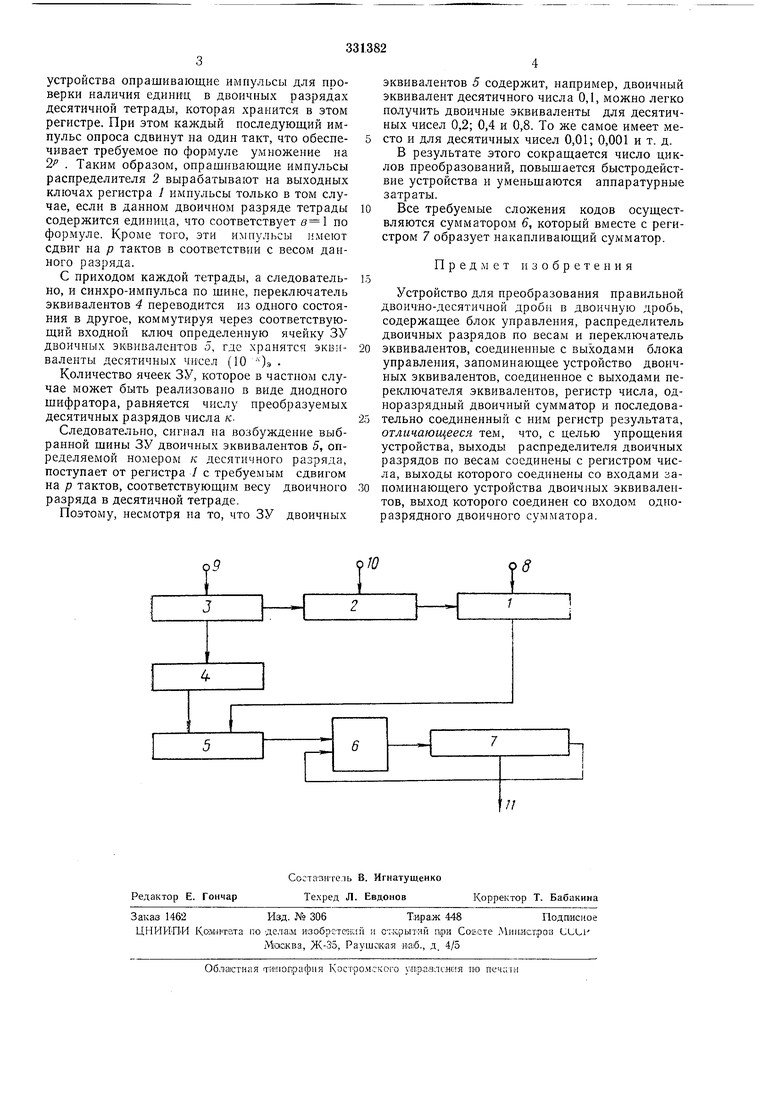

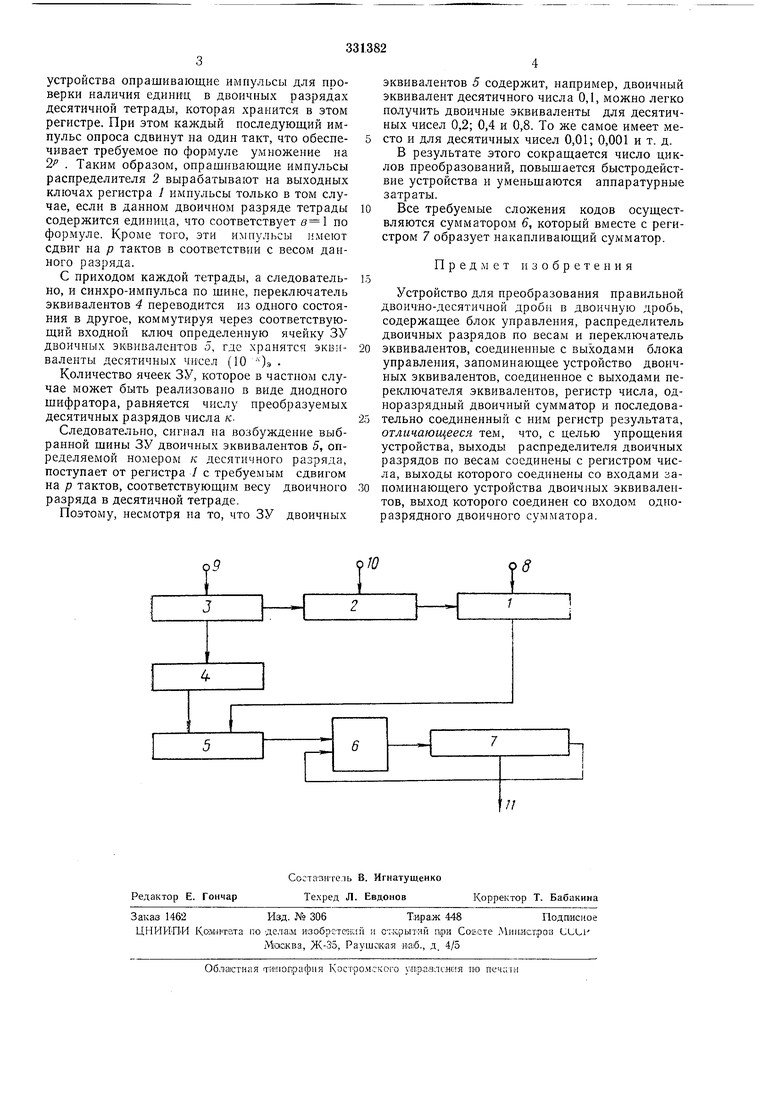

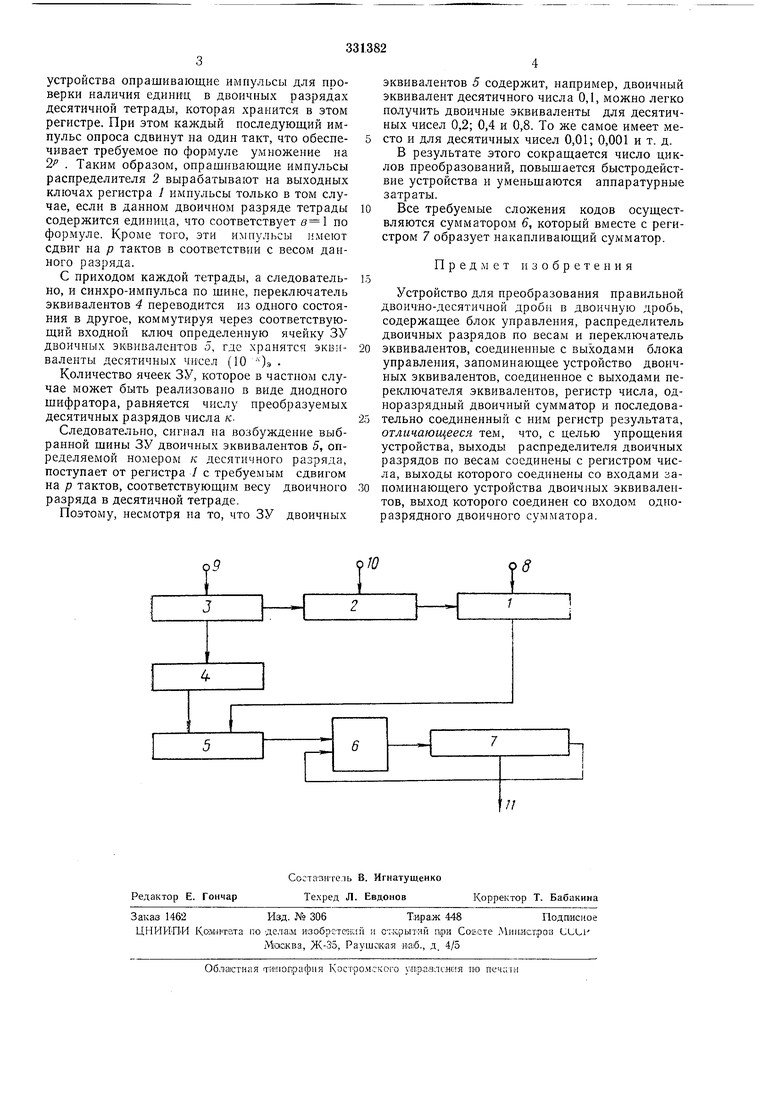

На чертеже изображена схема устройства.

Устройство содержит регистр 1 числа, распределитель 2 двоичных разрядов по весам, блок управления , переключатель эквивалентов 4, запоминающее устройство (ЗУ) двоичных эквивалентов 5, одноразрядньш двоичный сумматор 6, регистр результата 7, выходы 8 двоично-десятичных чисел, вход сипхро-импульсов 9, шину 10 подачи сигналов от датчика циклов и выход //.

Преобразование осуществляется с помощью сдвинутых двоичных эквивалентов десятичных

чисел вида 10

в соответствии со следующим выражением:

п

Л 1) о

где А - искомая правильная двоичная дробь; к - номер десятичного разряда правильной десятичной дроби иосле занятой; р - номер двоичного разряда двоично-десятичной тетрады; в-двоичная цифра (О или 1); (К) )s - двоичный эквивалент десятичного числа вида 10 ч

Устройство работает следующим образом. В регистр / числа по входам 8 последовательно один за другим, начиная со старшего, поступают двоично-десятичные разряды (тетрады) преобразуемого числа. Одновременно с каждым двоично-десятичным разрядом в блок управления 3 поступает управляющий синхро-имнульс, задающий старт-стопный режим работы устройства. Блок управления 3 вырабатывает импульсы, обеспечивающие поступление стробирующих импульсов от датчика циклов по шиие 10 в распределитель двоичных разрядов по их весам. Импульсы датчика циклов синхронизируют работу всего устройства с работой вычислительной машины. Блок 2 построен по принципу старт-стопного сдвигового регистра и выдает в регистр / с каждым циклом работы устройства опрашивающие импульсы для проверки наличия единиц в двоичных разрядах десятичной тетрады, которая хранится в этом регистре. При этом каждый последующий импульс опроса сдвинут на один такт, что обеспечивает требуемое по формуле умножение на 2 . Таким образом, опрашивающие импульсы распределителя 2 вырабатывают на выходных ключах регистра 7 имнульсы только в том случае, если в данном двоичном разряде тетрады содержится единица, что соответствует по формуле. Кроме того, эти импульсы имеют сдвиг на р тактов в соответствии с весом данного разряда. С приходом каждой тетрады, а следовательно, и синхро-импульса но щине, переключатель эквивалентов 4 переводится из одного состояния в другое, коммутируя через соответствующий входной ключ определенную ячейкуЗУ двоичных эквивалентов 5, где хранятся экьч(валенты десятичных чисел (10 Оэ Количество ячеек ЗУ, которое в частном случае может быть реализовано в виде диодного шифратора, равняется числу преобразуемых десятичных разрядов числа к. Следовательно, сигнал на возбуждение выбранной щины ЗУ двоичных эквивалентов 5, определяемой номером к десятичного разряда, поступает от регистра / с требуемым сдвигом на р тактов, соответствующим весу двоичного разряда в десятичной тетраде. Поэтому, несмотря на то, что ЗУ двоичных эквивалентов 5 содержит, например, двоичный эквивалент десятичного числа 0,1, можно легко получить двоичные эквиваленты для десятичных чисел 0,2; 0,4 и 0,8. То же самое имеет место и для десятичных чисел 0,01; 0,001 и т. д. В результате этого сокращается число циклов преобразований, повышается быстродействие устройства и уменьшаются аппаратурные затраты. Все требуемые сложения кодов осуществляются сумматором 6, который вместе с регистром 7 образует накапливающий сумматор. Предмет изобретения Устройство для преобразования правильной двоично-десятичной дроби в двоичную дробь, содержащее блок управления, распределитель двоичных разрядов по весам и переключатель эквивалентов, соединенные с выходами блока управления, запоминающее устройство двоичных эквивалентов, соединенное с выходами переключателя эквивалентов, регистр числа, одноразрядный двоичный сумматор и последовательно соединенный с ним регистр результата, отличающееся тем, что, с целью упрощения устройства, выходы распределителя двоичных разрядов по весам соединены с регистром числа, выходы которого соединены со входами запоминающего устройства двоичных эквивалентов, выход которого соединен со входом одноазрядного двоичного сумматора.

Даты

1972-01-01—Публикация