рого сумматора, выходы счетчика переносов и выходы группы элементов И соединены со вторым входом элемента ИЛИ, первые входы соединены с третьим входом блока управления, а вторые входы соединены с выходом счетчика переносов, вход которого соединен с выходом элемента И.

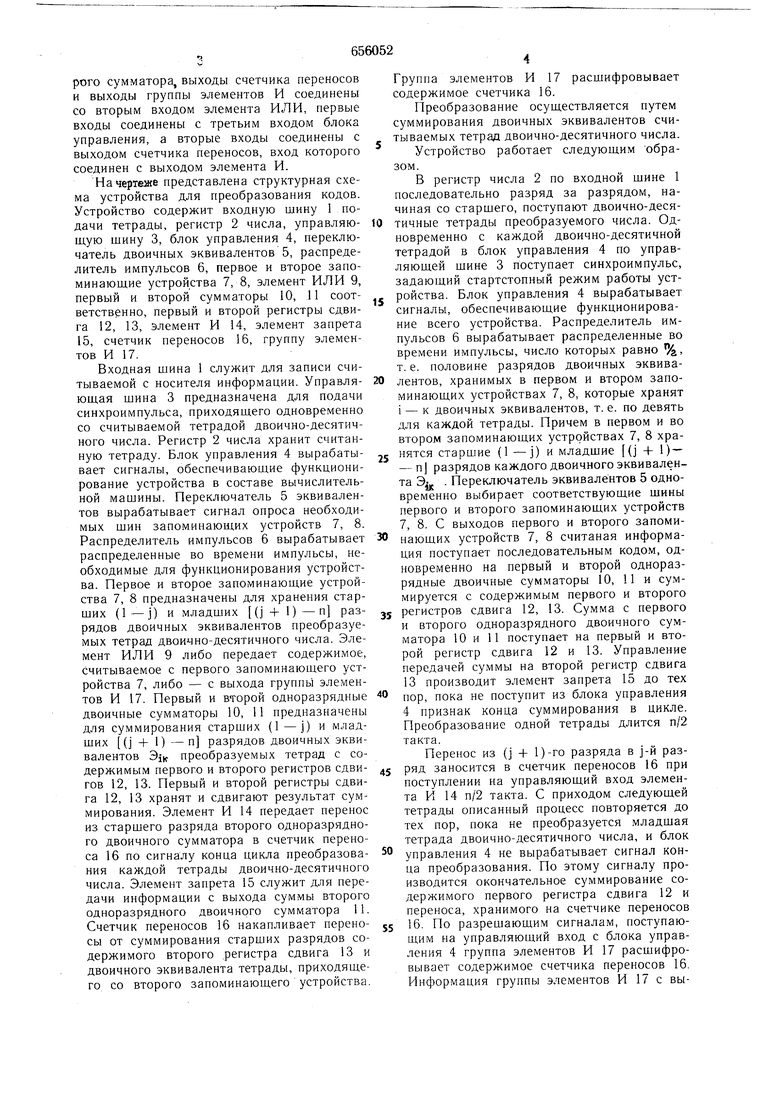

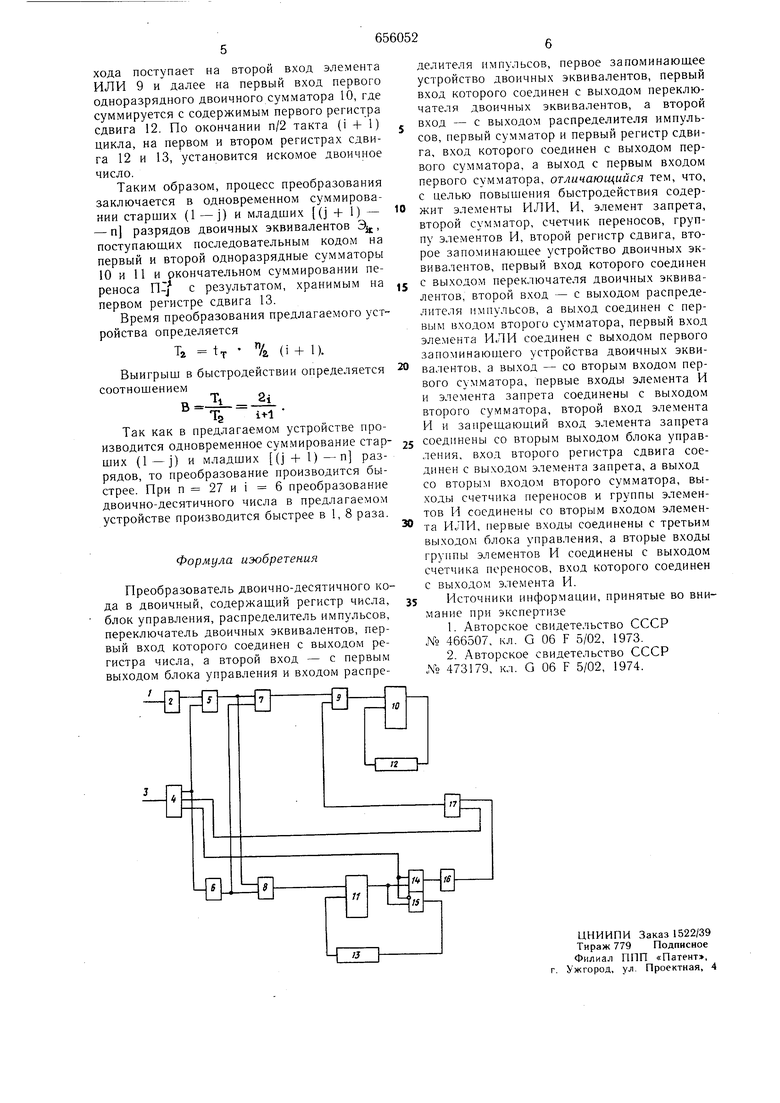

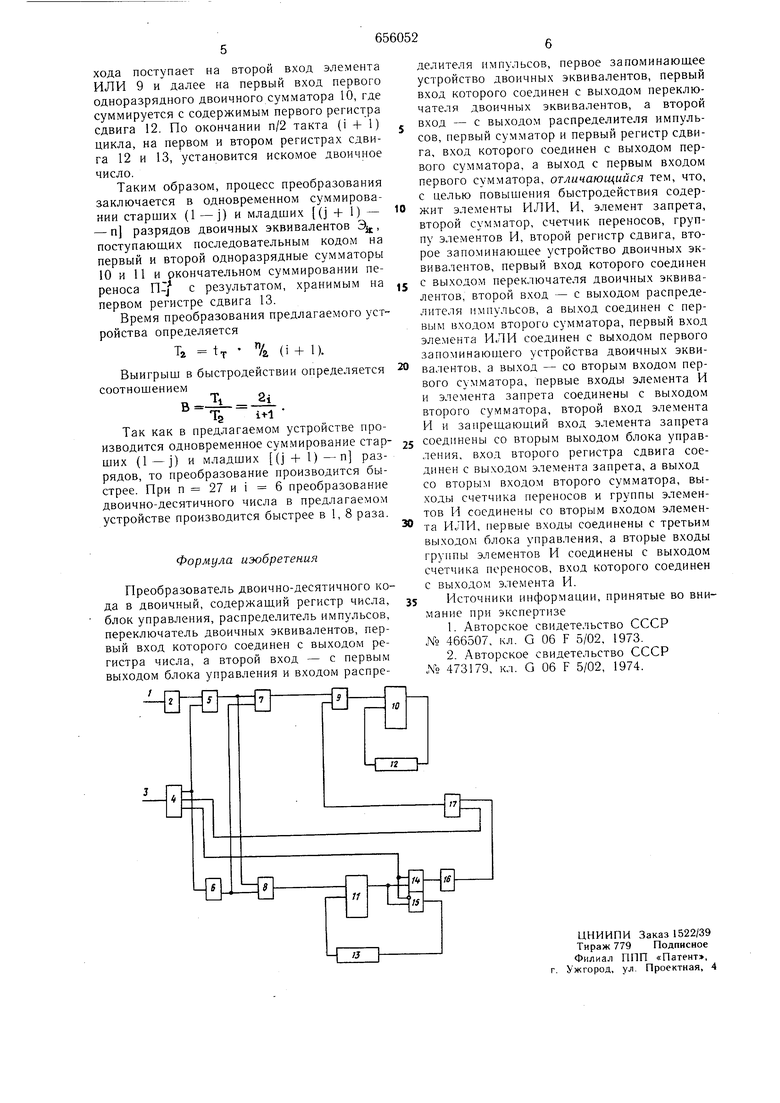

На чертеже представлена структурная схема устройства для преобразования кодов. Устройство содержит входную шину 1 подачи тетрады, регистр 2 числа, управляющую шину 3, блок управления 4, переключатель двоичных эквивалентов 5, распределитель импульсов 6, первое и второе запоминающие устройства 7, 8, элемент ИЛИ 9, первый и второй сумматоры 10, 11 соответственно, первый и второй регистры сдвига 12, 13, элемент И 14, элемент запрета 15, счетчик переносов 16, группу элементов И 17.

Входная шина 1 служит для записи считываемой с носителя информации. Управляющая шина 3 предназначена для подачи синхроимпульса, приходящего одновременно со считываемой тетрадой двоично-десятичного числа. Регистр 2 числа хранит считанную тетраду. Блок управления 4 вырабатывает сигналы, обеспечивающие функционирование устройства в составе вычислительной машины. Переключатель 5 эквивалентов вырабатывает сигнал опроса необходимых шин запоминающих устройств 7, 8. Распределитель импульсов 6 вырабатывает распределенные во времени импульсы, необходимые для функционирования устройства. Первое и второе запоминающие устройства 7, 8 предназначены для хранения старших (1 - j) и младших (J + 1) - п разрядов двоичных эквивалентов преобразуемых тетрад двоично-десятичного числа. Элемент ИЛИ 9 либо передает содержимое. Считываемое с первого запоминающего устройства 7, либо - с выхода группь элементов И 17. Первый и второй одноразрядные двоичные сумматоры 10, 11 предназначены для суммирования старших (1-j) и младщих (j + 1) -п разрядов двоичных эквивалентов 3i)f преобразуемых тетрад с содержимым первого и второго регистров сдвигов 12, 13. Первый и второй регистры сдвига 12, 13 хранят и сдвигают результат суммирования. Элемент И 14 передает перенос из старшего разряда второго одноразрядного двоичного сумматора в счетчик переноса 16 по сигналу конца цикла преобразования каждой тетрады двоично-десятичного числа. Элемент запрета 15 служит для передачи информации с выхода суммы второго одноразрядного двоичного сумматора 11. Счетчик переносов 16 накапливает переносы от суммирования старших разрядов содержимого второго регистра сдвига 13 и двоичного эквивалента тетрады, приходящего со второго запоминающего устройства.

Группа элементов И 17 расщифровывает содержимое счетчика 16.

Преобразование осуществляется путем суммирования двоичных эквивалентов считываемых тетрад двоично-десятичного числа. Устройство работает следующим образом.

В регистр числа 2 по входной щине 1 последовательно разряд за разрядом, начиная со старшего, поступают двоично-десятичные тетрады преобразуемого числа. Одновременно с каждой двоично-десятичной тетрадой в блок управления 4 по управляющей щине 3 поступает синхроимпульс, задающий стартстопный режим работы уст, ройства. Блок управления 4 вырабатывает сигналы, обеспечивающие функционирование всего устройства. Распределитель импульсов 6 вырабатывает распределенные во времени импульсы, число которых равно %, т. е. половине разрядов двоичных эквивалентов, хранимых в первом и втором запоминающих устройствах 7, 8, которые хранят i - к двоичных эквивалентов, т. е. по девять для каждой тетрады. Причем в первом и во втором запоминающих устройствах 7, 8 хранятся старшие (1 -j) и младшие (j + 1) - - nj разрядов каждого двоичного эквивалента Э . Переключатель эквивалентов 5 одновременно выбирает соответствующие шины первого и второго запоминающих устройств 7, 8. С выходов первого и второго запоминающих устройств 7, 8 считаная информация поступает последовательным кодом, одновременно на первый и второй одноразрядные двоичные сумматоры 10, 11 и суммируется с содержимым первого и второго

5 регистров сдвига 12, 13. Сумма с первого и второго одноразрядного двоичного сумматора 10 и 11 поступает на первый и второй регистр сдвига 12 и 13. Управление передачей суммы на второй регистр сдвига 13 производит элемент запрета 15 до тех

пор, пока не поступит из блока управления 4 признак конца суммирования в цикле. Преобразование одной тетрады длится п/2 такта.

Перенос из (j + 1)-го разряда в j-й разряд заносится в счетчик переносов 16 при поступлении на управляющий вход элемента И 14 п/2 такта. С приходом следующей тетрады описанный процесс повторяется до тех пор, пока не преобразуется младщая тетрада двоично-десятичного числа, и блок

управления 4 не вырабатывает сигнал конца преобразования. По этому сигналу производится окончательное суммирование содержимого первого регистра сдвига 12 и переноса, хранимого на счетчике переносов

5 16. По разрешающим сигналам, поступающим на управляющий вход с блока управления 4 группа элементов И 17 расшифровывает содержимое счетчика переносов 16. Информация группы элементов И 17 с выхода поступает на второй вход элемента ИЛИ 9 и далее на первый вход первого одноразрядного двоичного сумматора 10, где суммируется с содержимым первого регистра сдвига 12. По окончании п/2 такта (i + 1) цикла, на первом и втором регистрах сдвига 12 и 13, установится искомое двоичное число. Таким образом, процесс преобразования заключается в одновременном суммировании старших (1 -J) и младших (J + 1) - - п разрядов двоичных эквивалентов Э, поступаюш,их последовательным кодом на первый и второй одноразрядные сумматоры 10 и 11 и окончательном суммировании переноса nrj с результатом, хранимым на первом регистре сдвига 13. Время преобразования предлагаемого устройства определяется Та tT % (i + 1). Выигрыш в быстродействии определяется соотношением i Та 1И Так как в предлагаемом устройстве производится одновременное суммирование старших (1 - J) и младших (J + 1) - п разрядов, то преобразование производится быстрее. При п 27 и i 6 преобразование двоично-десятичного числа в предлагаемом устройстве производится быстрее в 1, 8 раза. Формула изобретения Преобразователь двоично-десятичного ко да в двоичный, содержаш,ий регистр числа, блок управления, распределитель импульсов, переключатель двоичных эквивалентов, первый вход которого соединен с выходом регистра числа, а второй вход - с первым выходом блока управления и входом распре/делителя импульсов, первое запоминающее устройство двоичных эквивалентов, первый вход которого соединен с выходом переключателя двоичных эквивалентов, а второй вход - с выходом распределителя импульсов, первый сумматор и первый регистр сдвига, вход которого соединен с выходом первого сумматора, а выход с первым входом первого сумматора, отличающийся тем, что, с целью повышения быстродействия содержит элементы ИЛИ, И, элемент запрета, второй сумматор, счетчик переносов, группу элементов И, второй регистр сдвига, второе запоминающее устройство двоичных эквивалентов, первый вход которого соединен с выходом переключателя двоичных эквивалентов, второй вход - с выходом распределителя импульсов, а выход соединен с первым входом второго сумматора, первый вход элемента ИЛИ соединен с выходом первого запоминающего устройства двоичных эквивалентов, а выход - со вторым входом первого сумматора, первые входы элемента И и элемента запрета соединены с выходом второго сумматора, второй вход элемента И и запрещающий вход элемента запрета соединены со вторым выходом блока управления, вход второго регистра сдвига соединен с выходом элемента запрета, а выход со вторым входом второго сумматора, выходы счетчика переносов и группы элементов И соединены со вторым входом элемента ИЛИ, первые входы соединены с третьим выходом блока управления, а вторые входы группы элементов И соединены с выходом счетчика переносов, вход которого соединен с выходом элемента И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР М 466507, кл. G 06 F 5/02, 1973. 2.Авторское свидетельство СССР № 473179, кл. G 06 F 5/02, 1974.

Авторы

Даты

1979-04-05—Публикация

1977-04-25—Подача