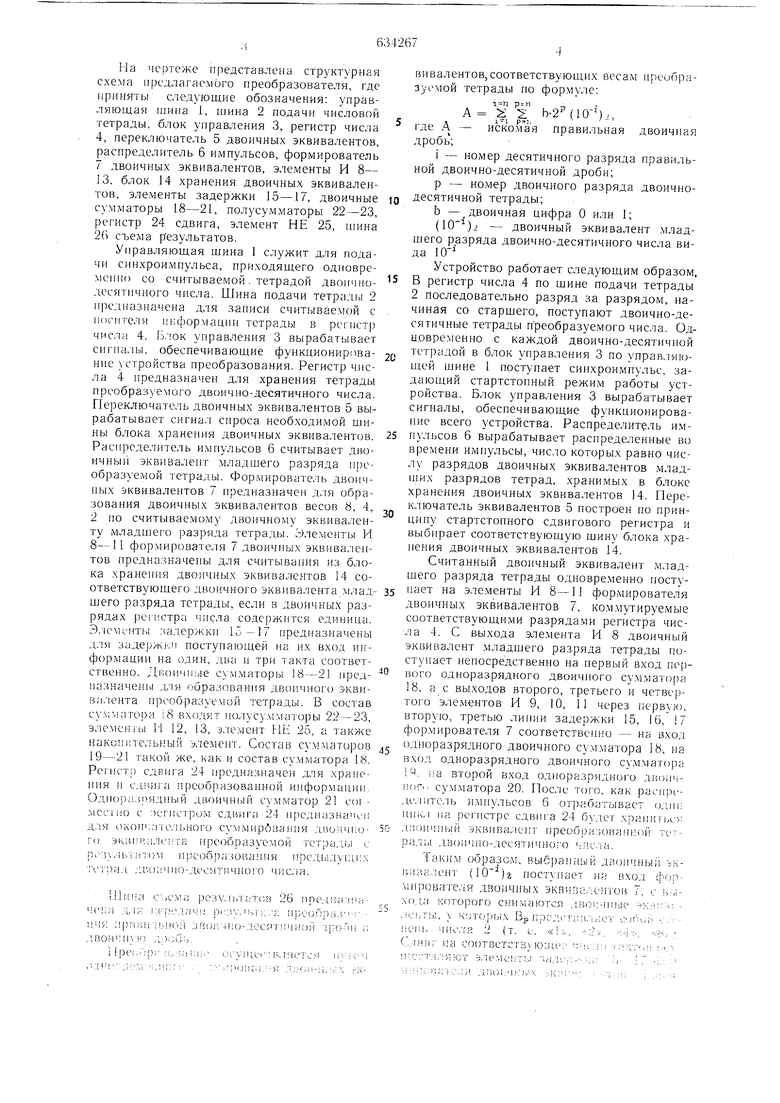

Предлагаемое устройство относится к области цифровой вычислительной техники и может быть использовано в устройствах обработки двоичной информации. Известны устройства для преобразования двоично-десятичных кодов в двоичный код 1, содержащие регистр числа, переключате.ть двоичных эквивалентов, блок хранения двоичных эквивалентов и суммирующие устройства. Недостатком известного устройства является большой объем аппаратуры и относительно низкое быстродействие. Наиболее близким техническим решением является преобразователь двоично-десятичных кодов в двоичный код 2, содержащий регистр числа, блок управления, переключатель двоичных эквивалентов, делитель импульсов, вход которого соединен с выходом блока управления и со входом переключателя двоичных эквивалентов, блок хранения двоичных эквивалентов, входы которого соединены с выходами переключателя двоичных эквивалентов и распределителя импульсов соответственно, четыре двоичных сумматора, регистр сдвига, вход которого соединен с выходом первого двоичного сумматора, а выход - с первым входом первого двоичного сумматора, три элемента задержки. Недостатком известного устройства является относительно большое количество аппаратуры. Целью изобретения является упрощение преобразователя. Цель достигается тем, что он содержит четыре элемента И, первые входы которых соединены с выходом блока хранения двоичных эквивалентов, вторые входы соединены с выходами регистра числа, выход первого элемента И соединен с первым входом второго двоичного с мматора, а выходы второго, третьего и четвертого элементов И через первый, второй и третий элементы задержки соединены со вторым входом второго и первыми входами третьего и четвертого двоичных сумматоров соответственно, выход второго двоичного сумматора соединен со вторым входом третьего двоичного сумматора, выход которого соединен со вторым входом четвертого двоичного сумматора, выход которого соединен со вторым входом первого двоичного сумматора. На чертеже представлена стрзктурная схема предлагаемого преобразователя, где приняты следующие обозначения: управляющая типа 1, шина 2 подачи числовой тетрады, блок управления 3, регистр числа 4, переключатель 5 двоичных эквивалентов, распределитель 6 импульсов, формирователь 7 двоичных эквивалентов, элементы И 8- 13, блок 14 хранения двоичных эквивалентов, элементы задержки 15-17, двоичные сумматоры 18-21, полусумматоры 22-23, регистр 24 сдвига, элемент НЕ 25, нина 26 съема результатов. Управляющая щина 1 служит для подачи синхроимпульса, приходящего одиовремеппо со считываемой. тетрадой двопчнодесятичного числа. Шина подачи тетрады 2 предназначена для записи считываемой с носителя информации тетрады в регистр числа 4. Б.юк управления3 вырабатывает сигналы, обеспечивающие функционирование устройства преобразования. Регистр числа 4 предназначен для хранения тетрады преобразуемого двоичио-десятичного числа. Переключатель двоичных эквивалентов 5 вырабатывает сигнал спроса необходимой шины блока хранения двоичных эквивалент ;в. Распределитель импульсов 6 считывает двоичныи эквивалент младшего разряда преобразуемой тетрады. Формирователь двоичных эквивалентов 7 предназначен д.ля образования двоичных эквивалентов весов 8, 4, 2 но считывае.мому двоичному эквиваленту младшего разряда тетрады. Элементы И формирователя 7 двоичных эквива.лептов предназначены для считывания из блока хранения двоичных эквивалентов 14 соответствующего двоичного эквивалента Л1ладшего разряда тетрады, если в двоичных разрядах peiiiCTpa числа содержится единица. 3.ie iLHTi i задержки 15-17 предназначены для задерж)-. поступающей на их вход информации на один, два н три такта соответственно. Д|К) сумматоры 18--21 иредназначены для образования ;1воичиого эквива.лента преобразуемой тетрады. В состав сумматора 18 входят полусумматоры 22---23, элемсн -ы 11 12, 13, элемент Hti 25, а также накопительный элемент. Состав сумматоров 19-21 такой же, как и состав сумматора 18. Регистр сдвига 24 предназначен для хранения и преобразованной инфор.мации, ().;и1О(); зпядпый двоичный сумматор 21 согмссгмо с ;)crHcTpoFvt сдвига 24 нредназна-Чч; д.ля окон1:ательного с ммирбва1(ия Д15и; чг;оГо экзикалшгга преобразуемой тетра.чь1 с ;):).Л1:.; игом И1;еобразо 5ания прсд|.ау1Д1:л тетрад .и():;чно-деоят11чного 4iic;ia. Лина слма результгггов 26 nptvui; : ;:Ч1м;л д. 1я ксГОлач:: i)i::.v. ; к/г; ipcoor)a, ьпоа .лво:;ч 1о-лесялл;Ч1Л(}11 л|;ои г; .1воичм}ло д.;(;: 1 ipe, ;(.. i;i i:i)i (л/унит-- пляетс:- П : ; i .Л Ip; ,;v::; -.lic:- . ;,.чюигл/Я ;;:jOiv;i.-.j -квивалентов,соответствующих весам преобразуемой тетрады по формуле: , А 2 2 b2(10) ..1де А - искомая правильная двоичная дробь; i - номер десятичного разряда правильной двоично-десятичной дроби; р - номер двоичного разряда двоичнодесятичной тетрады; Ь - двоичная цифра О или 1; (10); - двоичный эквивалент младщего разряда двоично-десятичного чис.ча вида 10 Устройство работает следующим образом, В регистр числа 4 по шине подачи тетрады 2 последовательно разряд за разрядом, начиная со старшего, поступают двоично-десятичные тетрады преобразуемого числа. Оды.овременно с каждой двоично-десятичной тетрадой в блок управления 3 по управляюн ей шине 1 поступает синхроимпульс, задающий стартстопный режим работы устройства. Блок управления 3 вырабатывает сигналы, обеспечивающие фупкпионирование всего устройства. Распределитель импульсов 6 вырабатывает распределенные во времени импульсы, число которых равно числу разрядов двоичных эквивалентов младши.х разрядов тетрад, хранимых в блоке хранения двоичных эквивалентов 14. Пе|)еключатель эквивалентов 5 построен по нринцину стартстопного сдвигового регистра и выбирает соответствующую шину блока хранения двоичных эквивалентов 14. Считанный двончный эквивалент младшего разряда тетрады одновременно поступает па элементы И 8- 11 формирователя двоичных эквивалентов 7, коммутируемые соответствующими разрядами регистра числа 4. С выхода эле.мента И 8 двоичный эквивалент младщего разряда тетрады поступает непосредственно на первый вход первого одноразрядного двоичного су.мматора 18, а с выходов второго, третьего и четве)того элементов И 9, 10, 11 через ). вторую, третью линии задержки 15, 16, 17 формирователя 7 соответственно - на вход одноразрядного двоичного сумматора 18, на в.ход одноразрядного двоичного су.мматора i Ч, iia второй вход одноразрядного диоичi t r.. су.м.матора 20. После того, как расиреде.лптель имнульеов 6 отрабатывает идш: HHi. па ре1Л1Стрс сдвига 24 будет хр;:п1-плд:-/: .чзоичньш эквивале1гг преобразованной .лы дв(Л1чи()-десятично;О чис.ла. TaKiiM образол, выбранный дйоичныг ;.к|1и;и:лепт (0)г ноетупает на вход формирователя двоичных .:снтов 7, с :,;хода которого снимаются . К:- ., K:;T()jJbiX Вр 11род Г;;;.л:лет vijoi,;: .л iiClli. ЧИС.ЛЯ 2 (т. с. «I:-.. -;;,:, , -vN, (. па СООТВеТСТЗХ ЮииЧ ;;;;,::: :;::;:.:; ;-. Ht.ic эквиваленты Heieiiibix десятичных ниф-х isiifiMe единицы, получаются путем суммирюi;;iHnvi двончпых эквивалентов, снимаемых с в 11хода формирователя двоичных эквивалентов 7. В блоке хранения двоичных эк :-;валентов 14 хранятся двоичные эквнва.1енты младших разрядов тетрад вида (0,1). (0,01)2 и т. д. Двоичный эквивалент иреобразуемой тетрады двоично-десятичногч) числа получается в результате суммирования двоичных эквивалентов, снимаемых с выхода формирователя двоичных эквивалентов 7. Предлагаемое устройство иозволяет суничтвенно сократить объем аппаратуры, т. к. отпадает необходимость в дешифрации кода тетрады и коммутации десяти цепей. Уменьн1ается также количество э; емент()в задержки. Формула изобретения Преобразователь двоично-десятичного кода в двоичный, содержащий регистр числа, блок унравления, переключатель двоичных эквивалентов, распределитель импульсов, вход которого соединен с выходом блока управления и со входом переключателя двоичных эквивалентов, блок хранения двоичных эквивалентов, вхолы которого соединеиы с выходам 11.рек.1Очателч ,У-,.:. -:.в;1валентов и раснреде,ч 1теля iiM;; ::hvO соответственно, четыре двоичных с} 1мито})а. регистр сдвига, вход которого сосд1М ен с выходом первого двоичного сумматора, а выход с первым входом первого двоичного сумматора, три элемента задержки, отличающийся тем. что, с целью упрощения устройства, он содержит четыре элемента 11, первые входы которых соединены с выходом блока хранения двоичных эквивалентов, в-гпрые входы соединены с выходами регистра числа, выход первого элемента И соединен с нервым входом второго двоичного С)мматора, а выходы второго, третьего и четвертого элементов И через первый, второй и третий элементы задержки соединены со вторым входом второго и первыми входами третьего, четвертого двоичных сумматоров соответственно, выход второго двоичного сумматора соединен со вторым входом третьего двоичного сумматора, вы.ход которого соединен со вторым входом четвертого двоичного сумматора, выход которого соединен со вторым входом первого двоичного сумматора. Источники информации, принятые во BIHIмание при экспертизе: 1.Авторское свидетельство СССР Лц 329525, кл, G 06 F 5/02, 24.11.70. 2.Авторское свидете.1ьство СССР ,N9 473179, кл. G 06 F 5/02. 5973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный преобразователь двоично-десятичных чисел в двоичные | 1973 |

|

SU473179A1 |

| Преобразование десятичного кода в двоичный код | 1977 |

|

SU742922A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоичнодесятичного кода в двоичный | 1977 |

|

SU656052A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1985 |

|

SU1292188A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU883893A1 |

Авторы

Даты

1978-11-25—Публикация

1975-09-10—Подача