Изобретение может быть применено для испытания и проверки феррит-транзисторны.ч ячеек (ФТЯ).

Известно устройство для испытания интегральных схем, состоящее из генератора импульсов, испытуемых ячеек и схе.м контроля. Вход первой ячейки соединен с выходом генератора иМПульсов, испытуемые ячейки соединены последовательно, а схема контроля поочередно подключается к выходам испытугмых ячеек.

Основным недостатком известного устройства является неточность получаемых при испытаниях результатов, так как вследствие пгриодического подключения контрольных схем невозможно зафиксировать сбои ячегк, возникающие в промежутках между подключениями. Если же использовать параллельный контроль испытуемых ячеек, то количество контрольных схем будет равно числу проверяемых ячеек.

Цель изобретения - упрощение процесса испытаний.

Для этого в предлагаемом устройстве выход каждой испытуемой ячейки соединен со входом записи соседней ячейки следующего столбца и со входом считывания следующей ячейки этого же столбца, обмотки записи всех ячеек первого столбца соединены последовательно и подключены к источнику нодмагничивающего тока, обмотки считывания первых ячеек нечетных столбцов присоединены к первому выходу генератора тактовых импульсов, сб.мотки считывания первых ячеек четных столбцов подключены ко второму выходу того же генератора, а к выходам последней ячейки всех столбцов и всех ячеек последнего столбца подключен блок контроля.

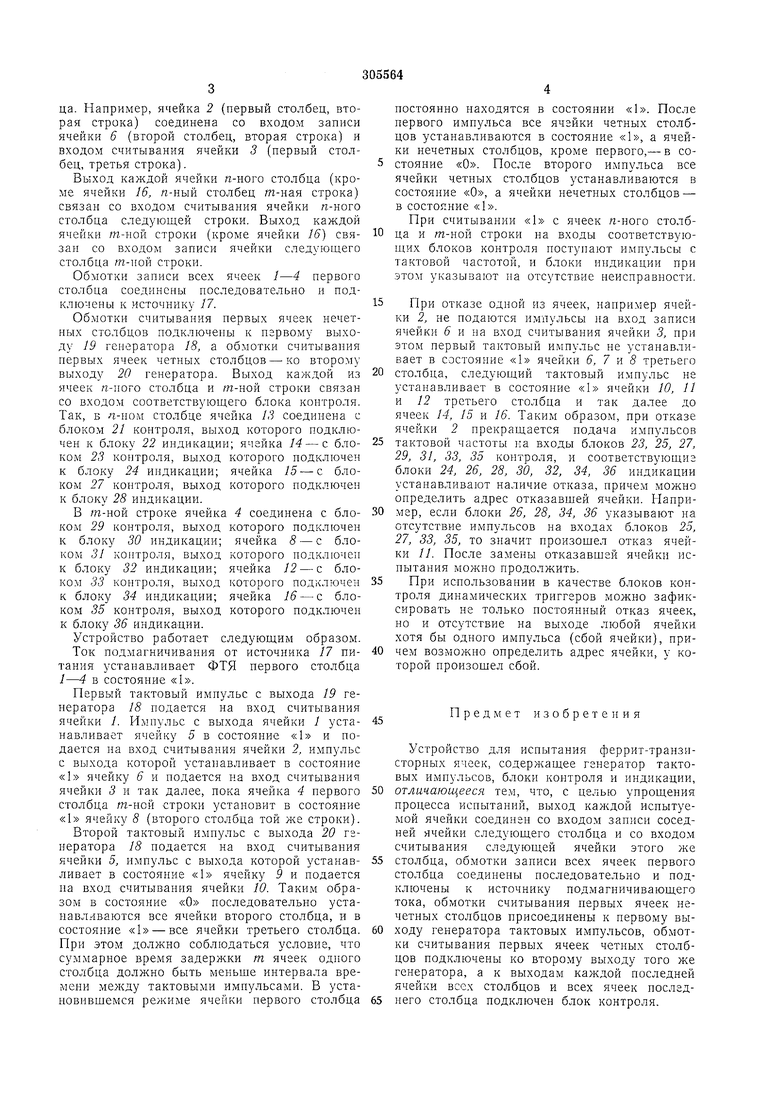

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит феррит-транзисторные ячейки /-16, истог ник 17 подмагничивающего тока, генератор 18 тактовых импульсов с

выходами 19 и 20, блоки 21, 23, 25, 27, 29, 31

33и 35 контроля и блоки 22, 24, 26, 28, 30, 32,

34и 36 индикации.

ФТЯ 1-16 связаны между собой по матричной схеме. Ячейки /-4 образуют первый

столбец матрицы, ячейки 5-8 - второй столбец, ячейки 13-16 - я-ный столбец. Соответственно, ячейки 1, 5, 9 У 13 - образуют первую строку матрицы, ячейки 2, 6, 10 и 14 - вторую строку и ячейки 4, 8, 12 и 16 - «г-ную

строку.

Выход каждой испытуемой ячейки (кроме ячеек, входящих в д-ный столбец и т--ную строку) соединен со входом записи соседней ячейки следующего столбца и со входом счица. Например, ячейка 2 (первый столбец, вторая строка) соединена со входом записи ячейки 6 (второй столбец, вторая строка) и входом считывания ячейки 5 (первый столбец, третья строка). Выход каждой ячейки п-ного столбца (кроме ячейки 16, я-ный столбец т-ная строка) связан со входом считывания ячейки п-ного столбца следующей строки. Выход каждой ячейки т-иой строки (кроме ячейки 16} связан со входом записи ячейки следующего столбца т-ной строки. Обмотки записи всех ячеек /-4 первого столбца соединены последовательно и подключены к источнику /7. Обмотки считывания первых ячеек нечетных столбцов подключены к первому выходу 19 генератора 18, а обмотки считывания первых ячеек четных столбцов-ко второму выходу 20 генератора. Выход каждой из 20 ячеек «-НОГО столбца и т-ной строки связан со входом соответствующего блока контроля. Так, Б п-ном столбце ячейка 13 соединена с блоком 21 контроля, выход которого подключен к блоку 22 индикации; ячейка М - с бло- 25 ком 23 контроля, выход которого нодключен к блоку 24 индикации; ячейка 15 - с блоком 27 контроля, выход которого подключен к блоку 28 индикации. В т-ной строке ячейка 4 соединена с бло- 30 ком 29 контроля, выход которого подключен к блоку 30 индикации; ячейка 8 - с блоком 31 контроля, выход которого нодключен к блоку 32 индикации; ячейка 12 - с блоком 33 контроля, выход которого подключен 35 к блоку 34 индикации; ячейка 16 - с блоком 35 контроля, выход которого подключен к блоку 36 индикации. Устройство работает следующим образом. Ток подмагничивания от источника 17 пи- 40 тания устанавливает ФТЯ первого столбца 1-4 в состояние «I. Первый тактовый имнульс с выхода 19 генератора 18 подается на вход считывания ячейки 1. Импульс с выхода ячейки / уста- 45 навливает ячейку 5 в состояние «1 и подается lia вход считывания ячейки 2, импульс с выхода которой устанавливает в состояние «1 ячейку 6 и подается на вход считывания ячейки 3 и так далее, пока ячейка 4 нервого 50 столбца т-ной строки установит в состояние «1 ячейку 8 (второго столбца той же строки). Второй тактовый импульс с выхода 20 ггнератора 18 подается на вход считывания ячейки 5, импульс с выхода которой устанав- 55 ливает в состояние «1 ячейку 9 и подается на вход считывания ячейки 10. Таким образом в состояние «О последовательно устанавливаются все ячейки второго столбца, и в состояние «1 - все ячейки третьего столбца. 60 При этом должно соблюдаться условие, что суммарное время задержки т ячеек одного столбца должно быть меньше интервала времени между тактовыми импульсами. В установившемся режиме ячейки первого столбца 65 5 постоянно находятся в состоянии «1. После первого импульса все ячейки четных столбцов устанавливаются в состояние «1, а ячейки нечетных столбцов, кроме первого,- в состояние «О. После второго импульса все ячейки четных столбцов устанавливаются в состояние «О, а ячейки нечетных столбцов - в состояние «I. При считывании «1 с ячеек п-ного столбца и т-ной строки на входы соответствующих блоков контроля постунают импульсы с тактовой частотой, и блоки индикации при этом указывают на отсутствие неисправности. При отказе одной из ячеек, например ячейки 2, не подаются импульсы на вход записи ячейки 6 и на вход считывания ячейки 3, при этом первый тактовый импульс не устанавливает в состояние «I ячейки 5, 7 и S третьего столбца, следуюн ий тактовый импульс не устанавливает в состояние «1 ячейки 10, 11 и 12 третьего столбца и так далее до ячеек 14, 15 и 16. Таким образом, при отказе ячейки 2 прекращается подача импульсов тактовой частоты на входы блоков 23, 25, 27, 29, 31, 33, 35 контроля, и соответствующие блоки 24, 26, 28, 30, 32, 34, 36 индикации устанавливают наличие отказа, причем можно определить адрес отказавщей ячейки. Папример, если блоки 26, 28, 34, 36 указывают на отсутствие импульсов на входах блоков 25, 27, 33, 35, то значит произощел отказ ячейки 11. После замены отказавшей ячейки испытания продолжить. При использовании в качестве блоков контроля динамических триггеров можно зафиксировать не только постоянный отказ ячеек, но и отсутствие на выходе любой ячейки хотя бы одного импульса (сбой ячейки), причем возможно определить адрес ячейки, у которой нроизощел сбой. Предмет изобретения Устройство для испытания феррит-транзисторных ячеек, содержащее генератор тактовых импульсов, блоки контроля и индикации, отличающееся тем, что, с целью упрощения процесса испытаний, выход каждой испытуемой ячейки соединен со входом записи соседней ячейки следующего столбца и со входом считывания следующей ячейки этого же столбца, обмотки записи всех ячеек первого столбца соединены носледовательно и подключены к источнику подмагничивающего тока, обмотки считывания первых ячеек нечетных столбцов присоединены к нервому выходу генератора тактовых импульсов, обмотки считывания первых ячеек четных столбцов подключены ко второму выходу того же генератора, а к выходам каждой последней ячейки всех столбцов и всех ячеек последнего столбца нодключен блок контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1981 |

|

SU1001180A1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU949721A1 |

| Устройство для контроля матриц памяти | 1982 |

|

SU1027780A2 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Способ диагностики отказов динамических объектов и устройство для его осуществления | 1990 |

|

SU1718190A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1010651A1 |

| Устройство для преобразования координат | 1982 |

|

SU1092535A1 |

Даты

1971-01-01—Публикация