1

Изобретение относится к области вычислительной техники.

Известно арифметическое устройство (АУ) с контролем, содержаш,ее регистр первого опе|э&нда, прямой выход которого подключен к первому входу первого вентиля, -второй вход которого соединен с первой входной клеммой, & выход - с первым входом сумматора и с первым входом блока сверток. Инверсный выход регистра первого операнда подключен к первому вхОхЦ,у второго вентиля, управляющий вход которого соедипен со второй входной клеммой, а выход - с первыми входами блока сверток и сумматора. Ко второму входу последнего подключепы выходы третьего и четвертого вентилей и второй вход блока сверток, а выход сумматора соединен с первым входом пятого вентиля, второй вход которого подключен к третьей входной клемме, а выход - к первому входу регистра результата, первый выход которого соединен с первым входом шестого вентиля, а второй вход подключен к четвертой входной клемме, выход - к первому входу регистра второго операнда, второй вход которого соединен с выходом седьмого вентиля. К первому входу последнего. по|дк; юч,вп лфаый выход репистра результата, а второй вход соеди.нен с пятой входной клеммой, первый выход регистра второго операнда подключен к входу сдвигового

2

регистра множителя, а второй выход - к первому входу третьего вентиля, второй вход которого соединен с шестой входной клеммой, третий выход регистра второго операнда подключен к первому входу четвертого вентиля, второй вход которого соединен с седьмой входной клеммой. Однако при помош.и этого устройства .невозможно скорректировать ошибку при отказе лгобого элемента.

Цель изобретения - обпаруженне .и коррекция ошибок при выполнении операцпй в АУ и сокращение, необходимого для этого оборудования. Для этого устройство содержит дополнительный сумматор, вентили, схему

кодирования, схему сравнения и блок формирования признаков ошибок, к первому входу которого подключен выход сдвигового регистра множителя, ко второму-первый выход регистра второго операнда, а к третьему -

выходы блока сверток, третий вход которого соединен с выходами восьмого и девятого вентилей и с первым входом дополнительного сумматора, ко второму входу которого подключен четвертый вход блока сверток и выходы десятого и оди-ннадцатого вентилей, а к третьему входу - третий вход первого сумматора и первый выход блока формирования признаков ошибок, второй выход которого соедипен с выходной клеммой, а третий - со

вторым входом регистра результата и третьим

входом регистра второго операнда, к четвертому входу которого подключен выход двенадцатого вентиля, один из входов которого соединен с восьмой входной клеммой, а другой - со вторым выходом .регистра результатов, к третьему входу которого подключен выход схемы кодирования, первый вход которой соединен с выходом первого сумматора, а второй с выходом дополнительного сумматора и первым входом тринадцатого вентиля, второй вход которого подключен к девятой входной клемме, а выход - к четвертому входу регистра результата и к первому входу схемы сравнения, второй вход которой соединен с выходом пятого вентиля, а выход - с четвертым входом блока формирования признаков ошибок, первые входы восьмого и девятого вентилей соединены с инверсным и прямым выходами регистра первого операнда, а вторые входы с первой и второй входными клеммами, соответственно, первые входы десятого « одиннадцатого вентилей соединены с инверсным я прямым выходами регистра второго операнда, а вторые входы - с шестой и седьмой входными клеммами, соответственно.

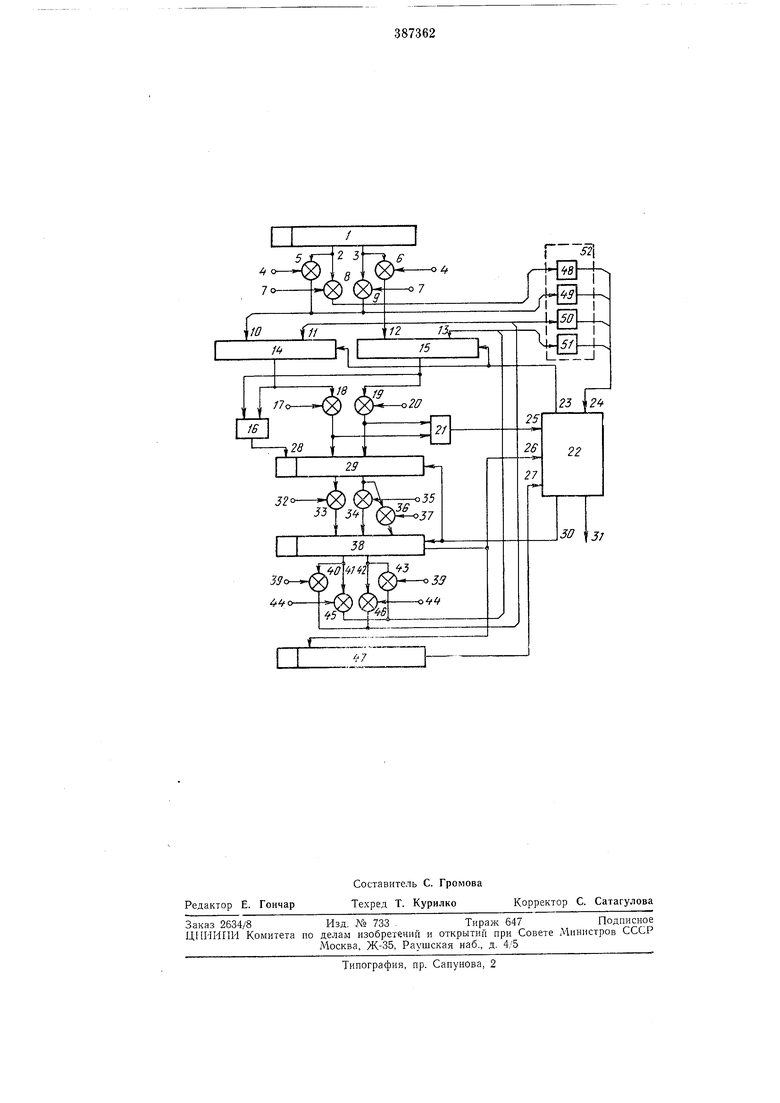

На чертеже представлена предлагаемая блок-схема арифметического устройства с контролем и коррекцией ошибок.

Блок-схема содержит регистр / первого oneранда, шины 2 инверсных значений кода первого операнда, шины 3 прямых значений кода первого операнда, входную клемму 4, на которую подается сигнал прямой передачи первого операнда, вентиль 5 для инверсной передачи операнда в сумматоры, вентиль 6 для прямой передачи операнда в сумматоры, входную клемму 7, на которую подается сигнал инверсной передачи первого операнда, вентиль 8 для инверсной передачи операнда в сумматоры, вентиль 9 для прямой передачи операнда в сумматор, вход 10 сумматора инверсных значений кодов первого операнда, вход 1/У сумматора инверсных значений кода второго операнда, вход 10. сумматора прямых значений кода первого операнда, вход /5 сумматора прямых значений кода второго операнда, дополнительный сумматор 14 инверсных значений кодов операндов, сумматор /5 прямых значений кодов операндов, схему кодирования 16, входную клемму 17, на которую подается сигнал записи инверсного значения результата, вентнль 18, вентиль 19, входную клемму 22, на которую подается сигнал записи прямого значения результата, схему сравнения 21, блок 22 формирования призиаков ошибок, шину 23 установки в «1 третьего входа младшего разряда сумматоров, шину 24 передачи контрольных кодов операндов в блок формирования признаков ошибок, шину 25сигнала совпадения результатов, шину 26 для передачи в блок формирования признаков ошибки значений, теряемых при сдвиге вправо младших разрядов чисел, шину 27 для передачи в блок формирования признаков ошибки значений, теряемых прн сдвиге вправо разрядов множителя, шину 28 передачи контрольного коДа в регистр результата, регистр результата 29, шину 30 установки регистров результата и второго операнда в исходное состояние, выходную клемму 31, входную клемщ 32, на которую подается шина-сигнал передачи инверсного значения из регистра результатов в регистр второго операнда, вентили для передачи инверсного значения результата 33 и прямого значения результата 34, входную клемму 35, на которую подается сигиал передачи прямого значения из регистра результатов в регистр второго операнда, вентиль 36 передачи из регистра результатов в регистр второго онеранда, со сдвигом вправо на один разряд, входную клемму 37, иа которую подается сигнал передачи из регистра результатов в регистр второго операнда со сдвигом вправо на один разряд, регистр 38 второго операнда, входную ,клемму 39, на которую подается сигнал прямой передачи второго операнда в сумматоры, вентиль 40 для инверсной передачи второго оиеранда в сумматоры, шины 41 инверсных значений кода второго операнда, шины 42 нрямых значений кода второго операнда, вентиль 43 для прямой передачи операнда в сумматоры, входную клемму 44, иа которую подается сигнал инверсной передачи второго операнда в сумматоры, вентиль 45 для ииверсной передачи второго операнда в сумматоры, вентиль 46 для прямой передачи второго операнда в сумматоры, сдвиговый регистр 47 множителя, 48, 49, 50, 51 - схемы сверток для формирования контрольных кодов, подаваемых на входы сумматоров прямых и инверсных значений кодов операндов, блок сверток 52.

Предлагаемое устройство работает следуюшим образом. Один из операндов, являющийся результатом предыдущей операции, находится вместе со своим контрольным кодом В регистре результата 29, второй операнд - в регистре /. После начала арифметической операции устройство управления выдает сиг иал на входную клемму 4 или 7. Вентили 5 и 6 или 8 и 9 открываются и первый операнд поступает на вход сумматора прямых значений кодов 15 и на вход 10 сумматора инверсных значений кодов 14. Второй операнд из регистра результатов 29 через вентили 33 и 34, управляемые сигналами из устройства управления, подаваемыми на входпые. клеммы 32 и 35, поступает в регистр второго операнда 38. Затем второй операнд через вентили 40 и 43 или 45 и 46, унравляемые сигналами из устройства управлершя, нодаваемььми на входные клеммы 39 илн 44, поступает на вход 13 сумматора прямых значений кодов 15 и вход // сумматора инверсных значений кодов. Одновременно в блоке 52 на схемах сверток 48-51 получают контрольные коды прямых и инверсных значений операндов. По шинам 24 их передают в блок формирования признаков ошибок, где,производится анализ

соответствия их контрольным признакам, которые сопровождают операнды. Получеппые ка выходах сумматоров М и 15 результаты операции через вентили прямых 19 и «liBepcных /:8 значеиий результата, управляемые сигналами из устройства управления сигпалами, подаваемыми на клеммы /7 и 20, подаются на схему сравнения 2/ и на запись в регистр результатов 29. Со схемы сравнения 21 в блок формирования признаков ошибок 22 по шине 25 выдается сигнал совпадения результатов, полученных в сулгматорах 14 и 15. Одновременно с этим на блоке кодирования 16 формируется контрольный признак результата операции и по шиие 28 он записывается в контрольные разряды регистра результата 29. Если результаты с выходов сумматоров ирямых и -ииверсиых значений кодов совпадают, то считается, что операция выполнена иравильно.

В блоке форл1ирования признаков ошибок 22 на основании сигналов из блока сверток 16 и схемы сравнения 21 вырабатываются сигналы ошибок 71-V5. Эти сигналы по шинам 31 поступают в устройство управления, в котором вырабатываются сигналы, позволяющие скорректировать ошибку.

В предлагаемом устройстве вырабатываются следуюш,ие сигналы ошибок: fi - результаты на выходе сумматоров не совпадают и есть ошибка в одном из операндов канала прямого кода; fz - .результаты совпали, но обнаружена ошибка в коде первого операнда, находящемся в регистре 1;

уз - результаты не совпадают и есть ошибка в одном из операндов канала инверсного кода; YI - результаты ие совпадают, но ошибки в

операндах отсутствуют;

Y5 - результаты совнадают, ио обнаружена ошибка во втором операиде, находящемся в регистре 38 или обнаружена ошибка в регистре миожителя. При появлеиии этих сигналов работа ЛУ протекает следующим образом: YI - по шиле 30 принудительно устанавливается в состояние «1 регистр результата 29 и в него записывается результат, полученный в канале инверсного кода, путем подачи управляющего сигнала по шиие 17 иа вентиль /8; Y2 - проводится повторное считывание первого операнда из памяти и в случае неоднократного повторения сигнала ошибки 72 вырабатывается сигнал ошибки 75;

Y3 - по шине 30 регистр результата 29 прииудительио устанавливается в состояние «О и в него записывается результат из канала прямого кода (ПК) путем подачи управляющего сигнала по шине 20 на вентиль 19;

74 - проводится проверка исправности сумматора прямых и сумматора инверсных значений кодов. Результат формируется в канале с ииверсным сумматором. Работа АУ происходит так же как при появлении сигнала ошибки 7i или 7з;

75 - организуется повторный просчет некоторого участка программы. Контроль операции сдвига влево аналогичен контролю операции сложения, поскольку сдвиг влево осуществляется путем сложения числа с самим собой.

Контроль операции сдвига вправо осуществляется следующим образом. Число из регистра результатов 29 через вентили 36, управляемые сигналы из УУ по шиие 37, подается со сдвигом вправо на один разряд в регистр второго операнда 58. Сдвигаемый вправо младший разряд по шине 26 поступает в блок формирования ошибки 22, где он учитывается при проверке передачи сдвинутого числа из регистра 38 па вход сумматоров, так как в результате сдвига соответствие контрольного кода числу в регистре 38 иарущается.

Дальнейщее прохождение информации из регистра 38 через сумматоры в регистр 29 выполняется аналогично операции , рассмотренной выше.

При операции умножения множимое находится в регистре /, множитель в регистре 47, частное - старшая часть в регистре результатов 29, а младшая часть в регистре множителя 47. Контроль и коррекция образования суммы частичных произведений организуется, как при операции сложеиия и сдвиге вправо. Контроль множителя осуществляется путем сравнения контрольного кода множителя с контрольным кодом, который вырабатывается из сдвигаемых вправо разрядов множителя, поступающих по шине 27 в блок формирования ощибки 22.

В предлагаемом устройстве коррекция ошибки в регистре множителя не предусматривается, поэтому при обнаружении ее блок формирования признака ошибки выдает сигнал 75. по которому предполагается повторное выполнение некоторого участка программы, а значит и повторный ввод множителя и исполнение операции умножения.

Контроль логических операций производится путем сравнения результатов, полученных одновременно в двух сумматорах.

Наличие двойного сумматора и схемы совпадения результ ат10В позволяет при выполнении операции выявить все одиночные и большинство многократных ошибок.

Предмет изобретения

Арифметическое устройство с контролем и коррекцией ошибок, содержащее регистр первого операнда, прямой выход которого подключен к первому входу первого вентиля, второй вход которого соединен с первой входной кле.ммой, а выход - с первым входом сумматора и с первым входом блока с зерток, а

инверсный выход регистра первого операнда

подключен к первому входу -втораго вентиля, управляющий вход которого соединеи со второй входиой клеммой, а выход - с первыми входами блока сверток и сумматора, ко второму входу которого подключены выходы третьего и четвертого вентилей и второй вход блока сверток, а выход сумматора соединен с первым входом пятого вентиля, второй вход которого подключен к третьей входной клемме, а выход - к первому входу регистра результата, первый выход которого соединен с первым входом шестого вентиля, второй вход которого подключен к четвертой входной клемме, а выход - к первому входу регистра второго операнда, второй вход которого соедннен с выходом седьмого вентиля, к первому входу которого подключен первый выход регистра результата, а второй вход соединен с пятой входной клеммой, первый выход регистра второго операнда подключен к входу сдвигового регистра множителя, а второй выход - к первому входу третьего вентиля, второй вход которого соединен с шестой входной клеммой, третий выход регистра второго операнда подключен к первому входу четвертого вентиля, второй вход которого соединен с седьмой входной клеммой, отличающееся тем, что, с целью повышения надежности работы устройства, оно содержит дополнительный сумматор, вентили, схему кодирования, схему сравнения -и блок формирования признаков ошибок, к первому входу которого подключен выход сдвигового регистра мнол ителя, ко второму - первый выход регистра второго операнда, а к третьему - выходы блока сверток, третий вход которого соединен с выходами восьмого и девятого вентилей и с первым входом дополнительного сумматора, ко второму входу которого подключен четвертый вход блока сверток и выходы десятого и одиннадцатого вентилей, а к третьему входу - третий вход нервого сумматора и первый выход блока формирования признаков ошибок, второй выход которого соединен с выходной клеммой, а третий - со вторым входом регистра реззльтата и третьим входом регистра второго операида, к четвертому входу которого подключен выход двенадцатого вентиля, один из входов которого соединен с восьмой входной клеммой, а другой - со вторым выходом регистра результатов, к третьему входу которого подключен выход схемы кодирования, пе|рвый вход которой соединен с выходом первого сумматора, а второй с выходом дополнительного сумматора и первым входом тринадцатого вентиля, второй вход которого подключен к девятой входной клемме, а выход - к четвертому входу регистра результата и к перво.му входу схемы сравнения, второй вход которой соединен с выходом пятого вентиля, а выход - с четвертым входом блока формирования признаков ошибок, первые входы восьмого и девятого вентилей соединены с инверсным и прямым выходами регистра первого операнда, а вторые входы с первой 1И второй входными клеммами соответственно, первые входы десятого и одиннадцатого вентилей соединены с инверсным и прямым выхода,м-и регистра второго операнда, а вторые входы - с шестой и седьмой входными клеммами соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с контролем | 1978 |

|

SU752333A1 |

| Устройство для контроля сумматора | 1983 |

|

SU1111167A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Устройство для умножения с контролем | 1989 |

|

SU1741128A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1076952A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

Авторы

Даты

1973-01-01—Публикация